www.ti.com

SCI Registers

603

SPRUI07–March 2020

Submit Documentation Feedback

Copyright © 2020, Texas Instruments Incorporated

Serial Communications Interface (SCI)

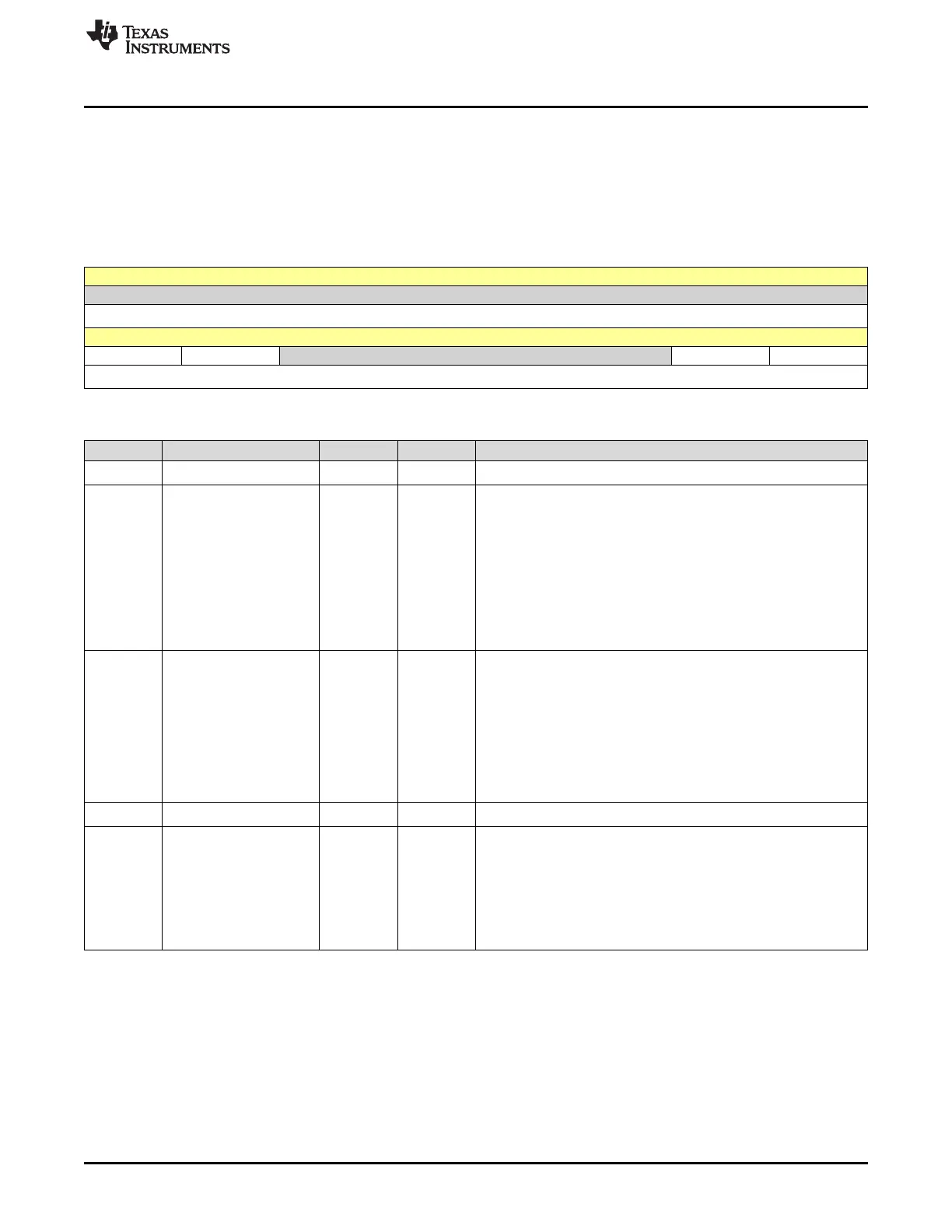

10.14.2.5 SCICTL2 Register (Offset = 4h) [reset = C0h]

SCICTL2 is shown in Figure 10-15 and described in Table 10-11.

Return to the Summary Table.

SCICTL2 enables the receive-ready, break-detect, and transmit-ready interrupts as well as transmitter-

ready and -empty flags.

Figure 10-15. SCICTL2 Register

15 14 13 12 11 10 9 8

RESERVED

R-0h

7 6 5 4 3 2 1 0

TXRDY TXEMPTY RESERVED RXBKINTENA TXINTENA

R-1h R-1h R-0h R/W-0h R/W-0h

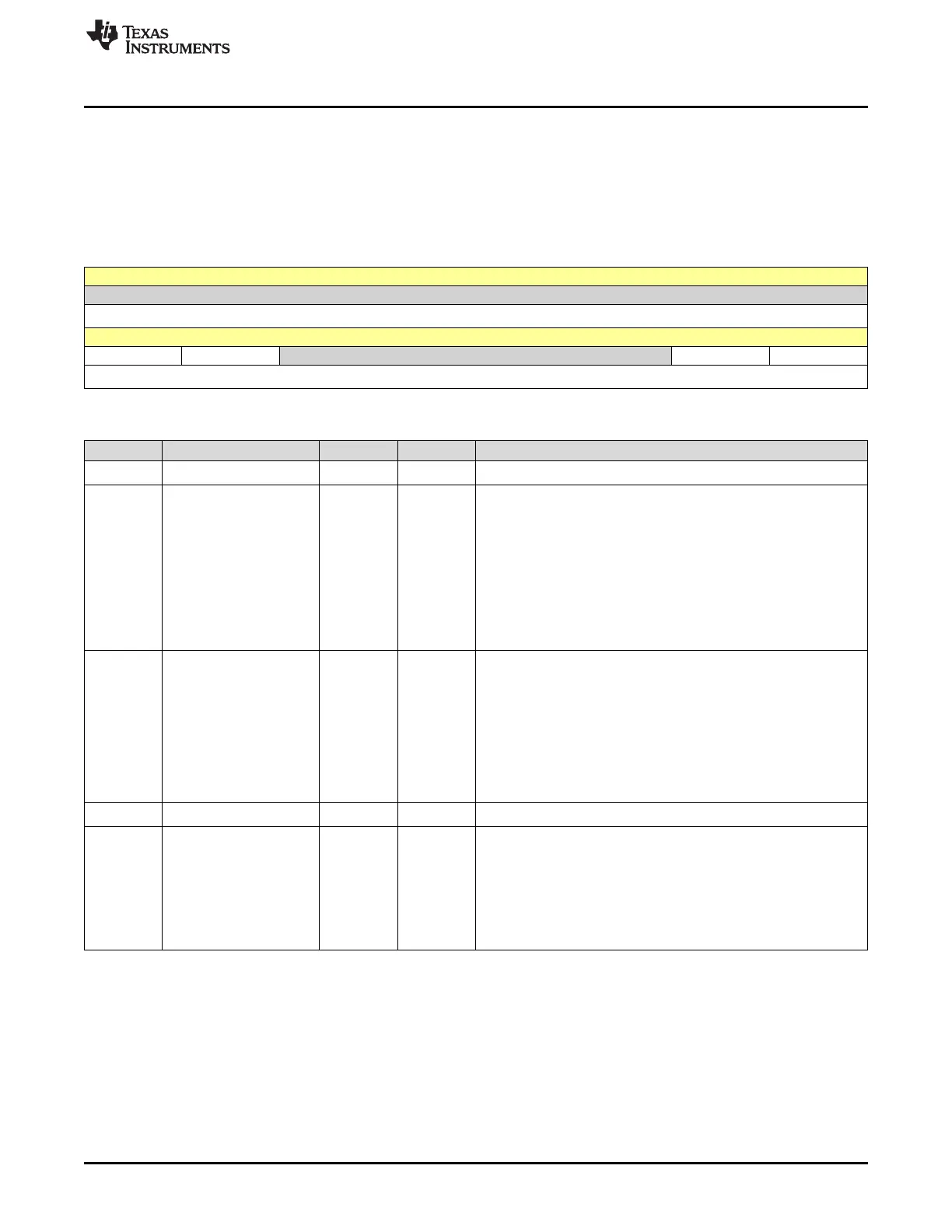

Table 10-11. SCICTL2 Register Field Descriptions

Bit Field Type Reset Description

15-8 RESERVED R 0h

Reserved

7 TXRDY R 1h

Transmitter buffer register ready flag.

When set, this bit indicates that the transmit data buffer register,

SCITXBUF, is ready to receive another character. Writing data to the

SCITXBUF automatically clears this bit. When set, this flag asserts a

transmitter interrupt request if the interrupt-enable bit, TX INT ENA

(SCICTL2.0), is also set. TXRDY is set to 1 by enabling the SW

RESET bit (SCICTL1.5) or by a system reset.

Reset type: SYSRSn

0h (R/W) = SCITXBUF is full

1h (R/W) = SCITXBUF is ready to receive the next character

6 TXEMPTY R 1h

Transmitter empty flag.

This flag's value indicates the contents of the transmitter's buffer

register (SCITXBUF) and shift register (TXSHF). An active SW

RESET (SCICTL1.5), or a system reset, sets this bit. This bit does

not cause an interrupt request.

Reset type: SYSRSn

0h (R/W) = Transmitter buffer or shift register or both are loaded

with data

1h (R/W) = Transmitter buffer and shift registers are both empty

5-2 RESERVED R 0h

Reserved

1 RXBKINTENA R/W 0h

Receiver-buffer/break interrupt enable.

This bit controls the interrupt request caused by either the RXRDY

flag or the BRKDT flag (bits SCIRXST.6 and .5) being set. However,

RX/BK INT ENA does not prevent the setting of these flags.

Reset type: SYSRSn

0h (R/W) = Disable RXRDY/BRKDT interrupt

1h (R/W) = Enable RXRDY/BRKDT interrupt

Loading...

Loading...