SCI Registers

www.ti.com

604

SPRUI07–March 2020

Submit Documentation Feedback

Copyright © 2020, Texas Instruments Incorporated

Serial Communications Interface (SCI)

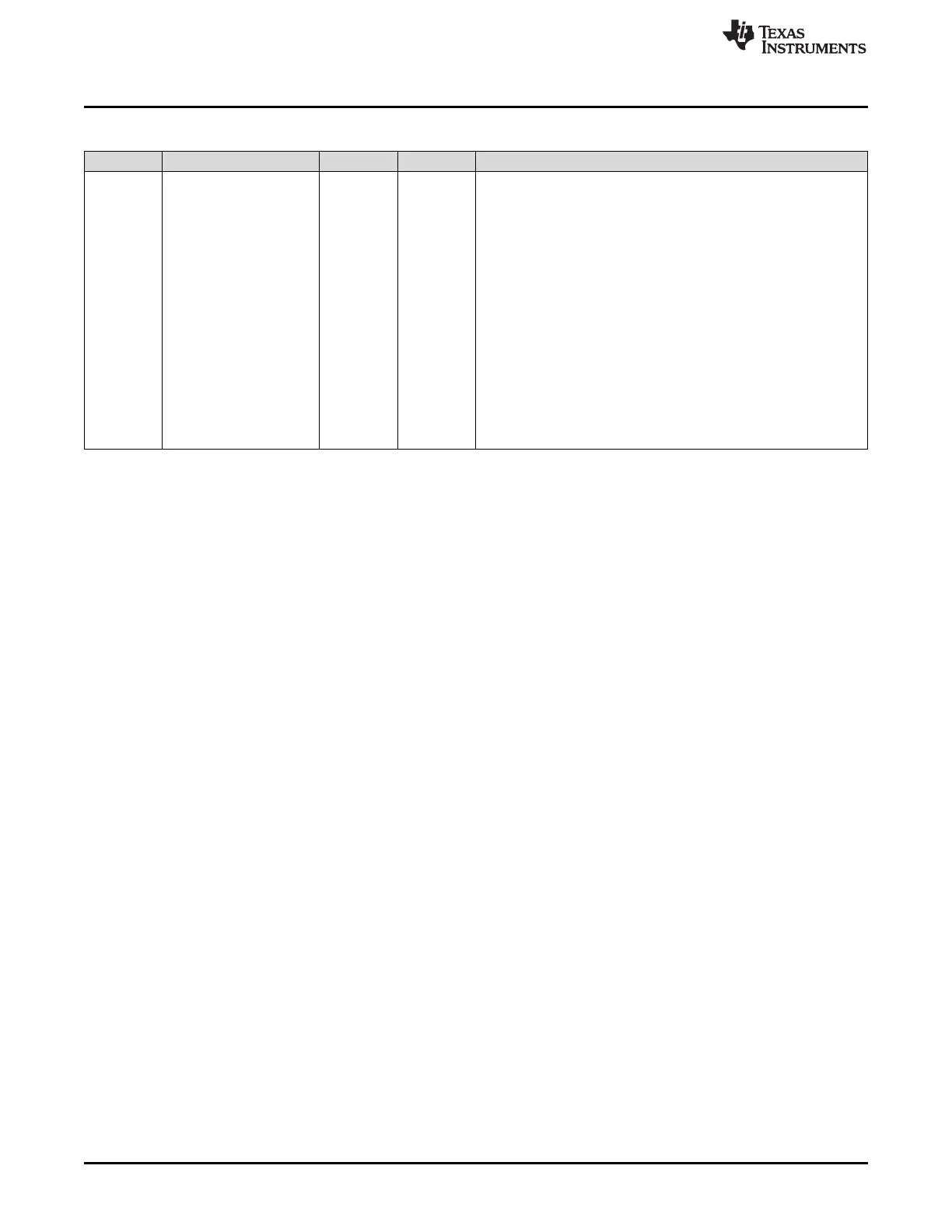

Table 10-11. SCICTL2 Register Field Descriptions (continued)

Bit Field Type Reset Description

0 TXINTENA R/W 0h

SCITXBUF-register interrupt enable.

This bit controls the interrupt request caused by the setting of

TXRDY flag bit (SCICTL2.7). However, it does not prevent the

TXRDY flag from being set (which indicates SCITXBUF is ready to

receive another character).

0 Disable TXRDY interrupt

1 Enable TXRDY interrupt.

In non-FIFO mode, a dummy (or a valid) data has to be written to

SCITXBUF for the first transmit interrupt to occur. This is the case

when you enable the transmit interrupt for the first time and also

when you re-enable (disable and then enable) the transmit interrupt.

If TXINTENA is enabled after writing the data to SCITXBUF, it will

not generate an interrupt.

Reset type: SYSRSn

0h (R/W) = Disable TXRDY interrupt

1h (R/W) = Enable TXRDY interrupt

Loading...

Loading...