I2C Registers

www.ti.com

638

SPRUI07–March 2020

Submit Documentation Feedback

Copyright © 2020, Texas Instruments Incorporated

Inter-Integrated Circuit Module (I2C)

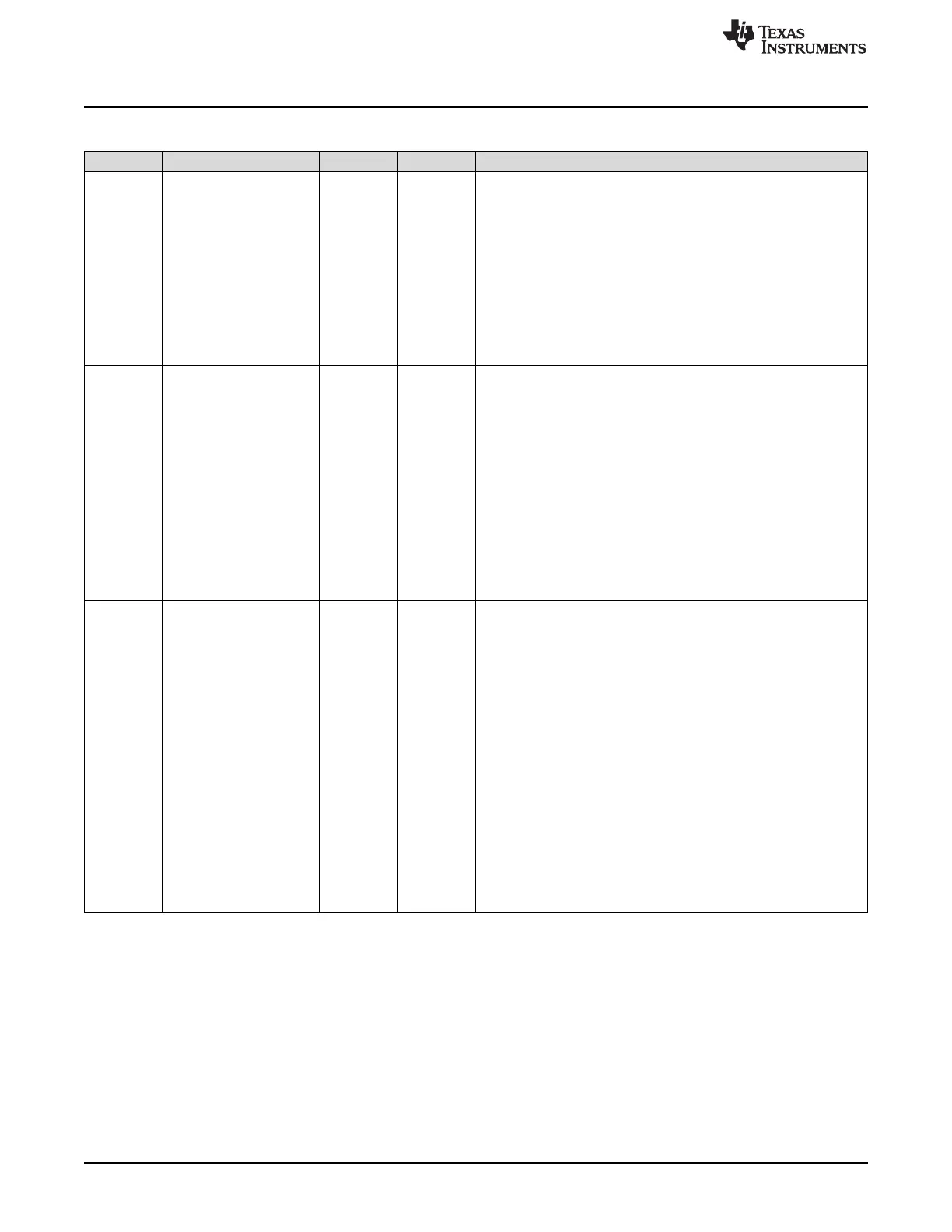

Table 11-12. I2CSTR Register Field Descriptions (continued)

Bit Field Type Reset Description

4 XRDY R 1h

Transmit-data-ready interrupt flag bit.

When not in FIFO mode, XRDY indicates that the data transmit

register (I2CDXR) is ready to accept new data because the previous

data has been copied from I2CDXR to the transmit shift register

(I2CXSR). The CPU can poll XRDY or use the XRDY interrupt

request When in FIFO mode, use TXFFINT instead.

Reset type: SYSRSn

0h (R/W) = I2CDXR not ready. XRDY is cleared when data is

written to I2CDXR.

1h (R/W) = I2CDXR ready: Data has been copied from I2CDXR to

I2CXSR.

XRDY is also forced to 1 when the I2C module is reset.

3 RRDY R/W1C 0h

Receive-data-ready interrupt flag bit.

When not in FIFO mode, RRDY indicates that the data receive

register (I2CDRR) is ready to be read because data has been copied

from the receive shift register (I2CRSR) to I2CDRR. The CPU can

poll RRDY or use the RRDY interrupt request When in FIFO mode,

use RXFFINT instead.

Reset type: SYSRSn

0h (R/W) = I2CDRR not ready. RRDY is cleared by any one of the

following events:

- I2CDRR is read by the CPU. Emulator reads of the I2CDRR do

not affect this bit.

- RRDY is manually cleared. To clear this bit, write a 1 to it.

- The I2C module is reset.

1h (R/W) = I2CDRR ready: Data has been copied from I2CRSR to

I2CDRR.

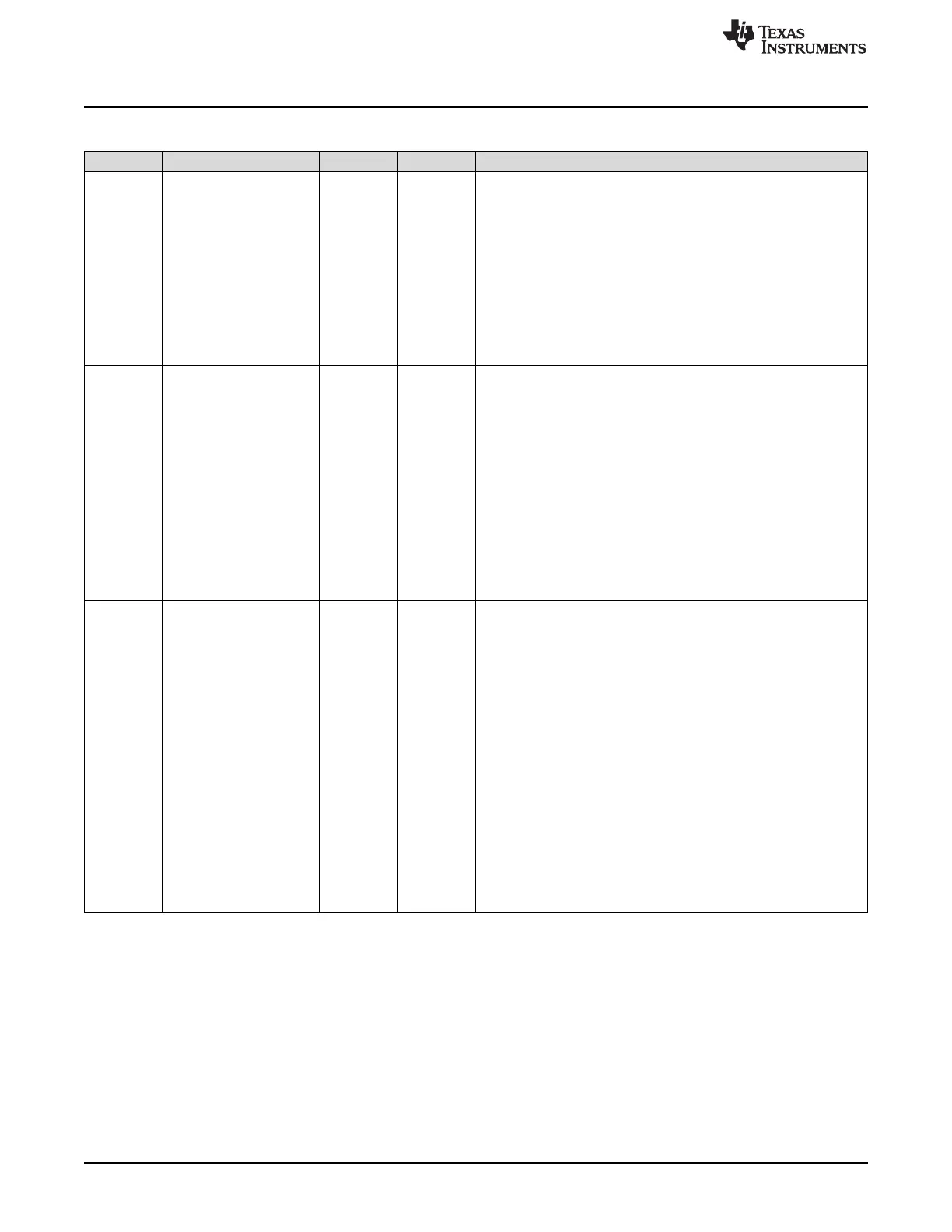

2 ARDY R/W1C 0h

Register-access-ready interrupt flag bit (only applicable when the I2C

module is in the master

mode).

ARDY indicates that the I2C module registers are ready to be

accessed because the previously programmed address, data, and

command values have been used. The CPU can poll ARDY or use

the ARDY interrupt request.

Reset type: SYSRSn

0h (R/W) = The registers are not ready to be accessed. ARDY is

cleared by any one of the following events:

- The I2C module starts using the current register contents.

- ARDY is manually cleared. To clear this bit, write a 1 to it.

- The I2C module is reset.

1h (R/W) = The registers are ready to be accessed.

In the nonrepeat mode (RM = 0 in I2CMDR): If STP = 0 in

I2CMDR, the ARDY bit is set when the internal data counter counts

down to 0. If STP = 1, ARDY is not affected (instead, the I2C

module generates a STOP condition when the counter reaches 0).

In the repeat mode (RM = 1): ARDY is set at the end of each byte

transmitted from I2CDXR.

Loading...

Loading...