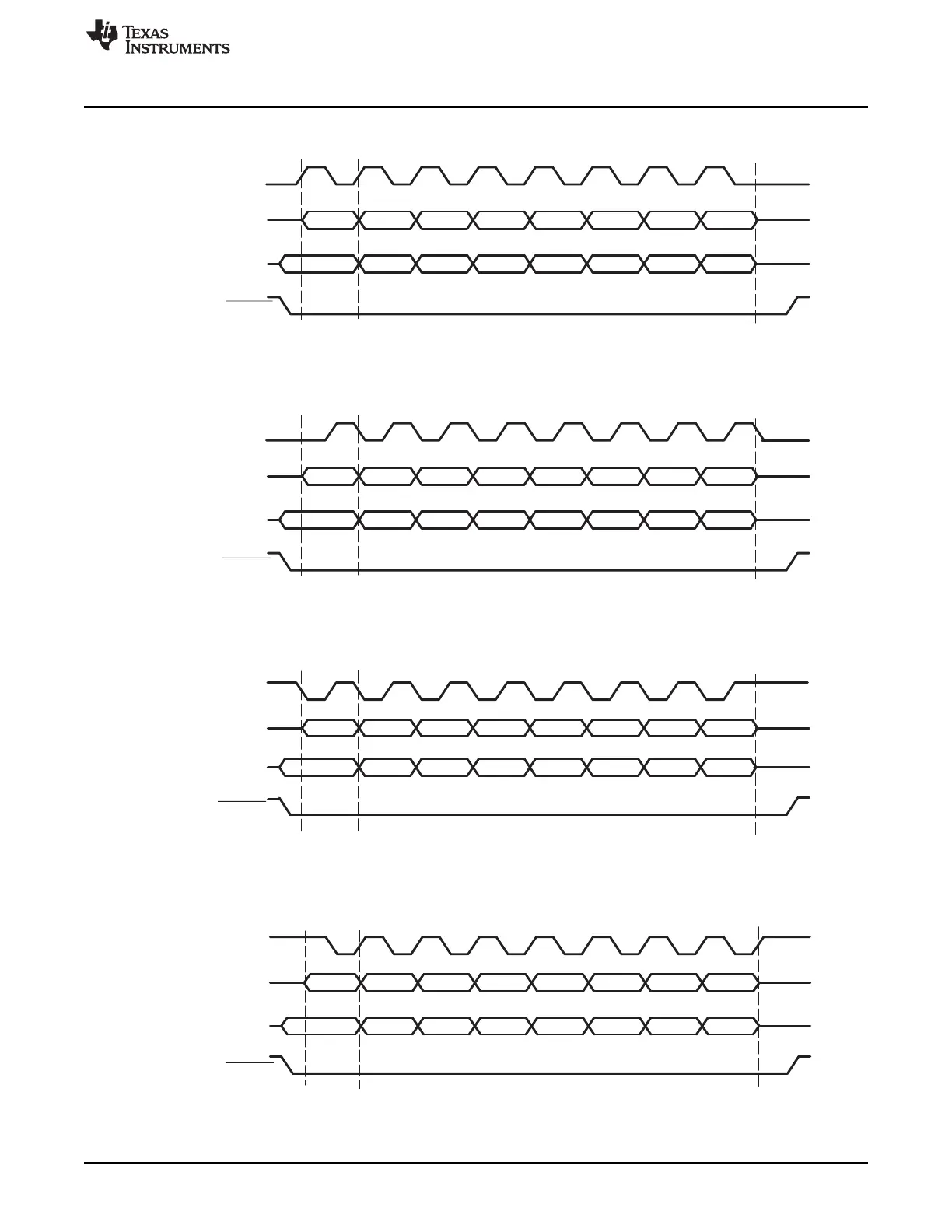

B1B2B4 B3 B0B5B6B7

B0B1B2

B3B4

B5

B6

B7

FSX/SPISTE

CLKX/SPICLK

DX or DR/SIMO

(from master)

DX or DR/SOMI

(from slave)

B1B2B4 B3 B0B5B6B7

B0

B1

B2

B3

B4B5B6

B7

FSX/SPISTE

CLKX/SPICLK

DX or DR/SIMO

(from master)

DX or DR/SOMI

(from slave)

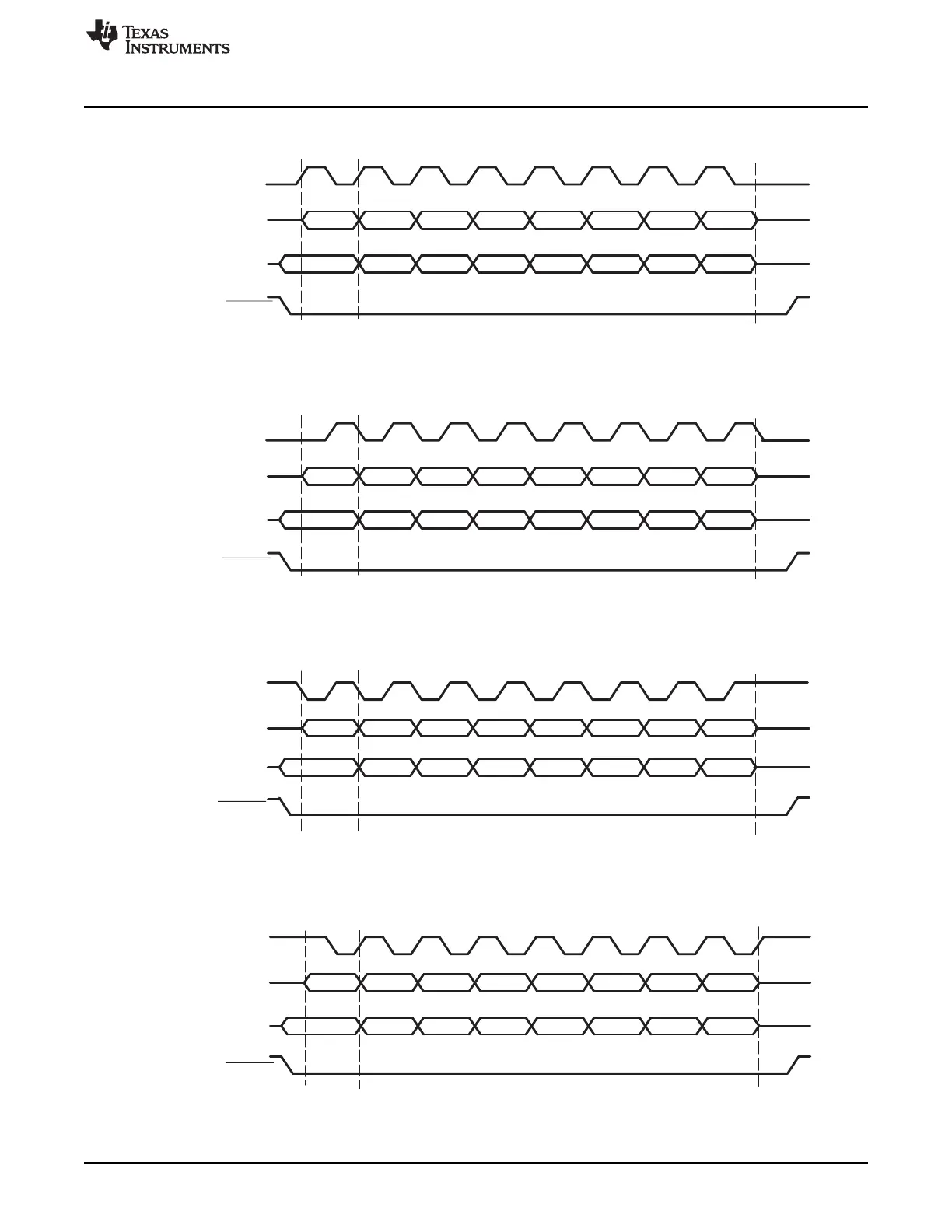

B1B2

B4

B3 B0B5B6

B7

B0

B1B2

B3B4B5B6B7

FSX/SPISTE

DX or DR/SIMO

(from master)

CLKX/SPICLK

DX or DR/SOMI

(from slave)

B1B2

B4

B3 B0B5B6

B7

B0

B1B2

B3B4B5B6B7

FSX/SPISTE

DX or DR/SIMO

(from master)

CLKX/SPICLK

DX or DR/SOMI

(from slave)

www.ti.com

SPI Operation Using the Clock Stop Mode

695

SPRUI07–March 2020

Submit Documentation Feedback

Copyright © 2020, Texas Instruments Incorporated

Multichannel Buffered Serial Port (McBSP)

Figure 12-37. SPI Transfer With CLKSTP = 10b (No Clock Delay), CLKXP = 0, and CLKRP = 0

A If the McBSP is the SPI master (CLKXM = 1), SIMO = DX. If the McBSP is the SPI slave (CLKXM = 0), SIMO = DR.

B If the McBSP is the SPI master (CLKXM = 1), SOMI = DR. If the McBSP is the SPI slave (CLKXM = 0), SOMI = DX.

Figure 12-38. SPI Transfer With CLKSTP = 11b (Clock Delay), CLKXP = 0, CLKRP = 1

A If the McBSP is the SPI master (CLKXM = 1), SIMO = DX. If the McBSP is the SPI slave (CLKXM = 0), SIMO = DR.

B If the McBSP is the SPI master (CLKXM = 1), SOMI = DR. If the McBSP is the SPI slave (CLKXM = 0), SOMI = DX.

Figure 12-39. SPI Transfer With CLKSTP = 10b (No Clock Delay), CLKXP = 1, and CLKRP = 0

A If the McBSP is the SPI master (CLKXM = 1), SIMO = DX. If the McBSP is the SPI slave (CLKXM = 0), SIMO = DR.

B If the McBSP is the SPI master (CLKXM = 1), SOMI = DR. If the McBSP is the SPI slave (CLKXM = 0), SOMI = DX.

Figure 12-40. SPI Transfer With CLKSTP = 11b (Clock Delay), CLKXP = 1, CLKRP = 1

A If the McBSP is the SPI master (CLKXM = 1), SIMO=DX. If the McBSP is the SPI slave (CLKXM = 0), SIMO = DR.

B If the McBSP is the SPI master (CLKXM = 1), SOMI=DR. If the McBSP is the SPI slave (CLKXM = 0), SOMI = DX.

Loading...

Loading...