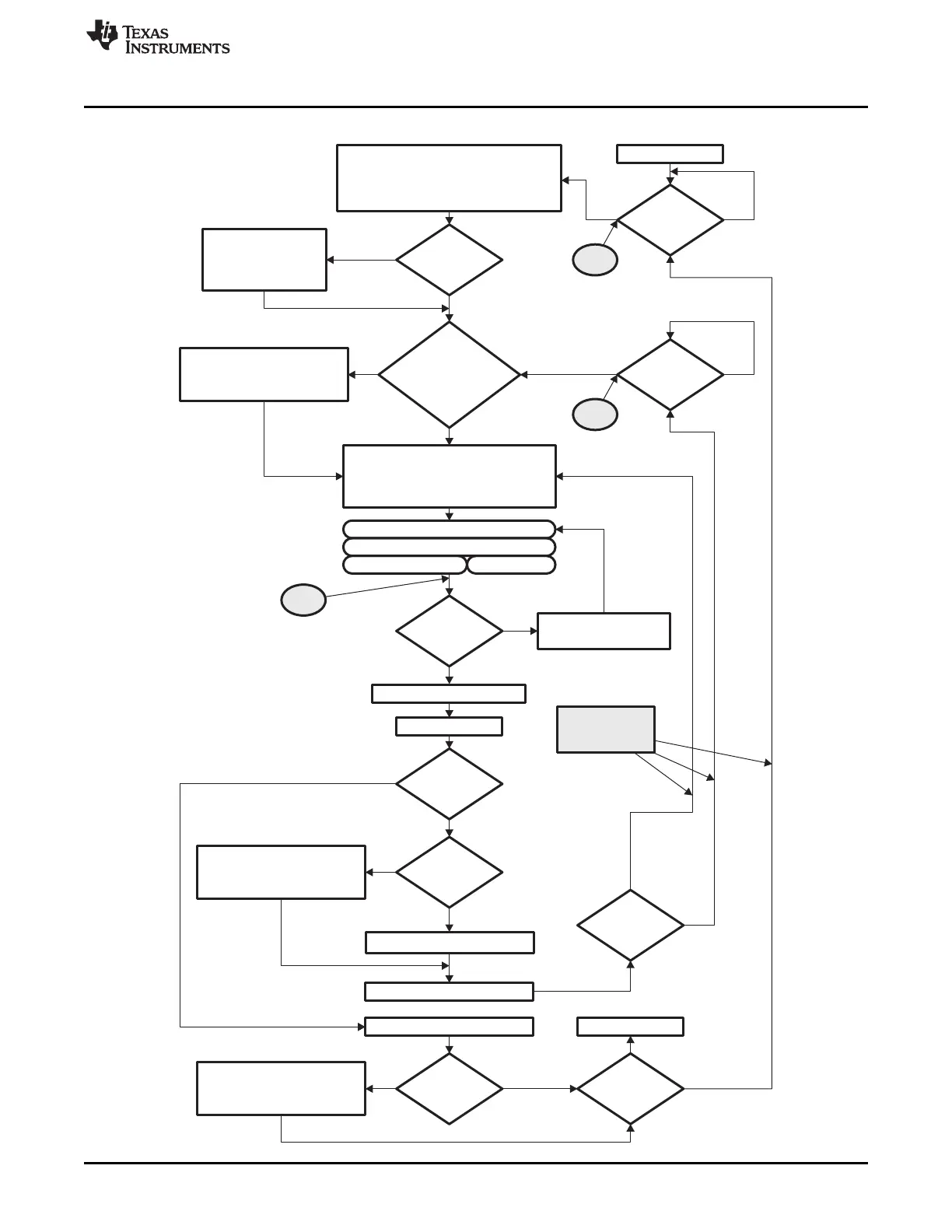

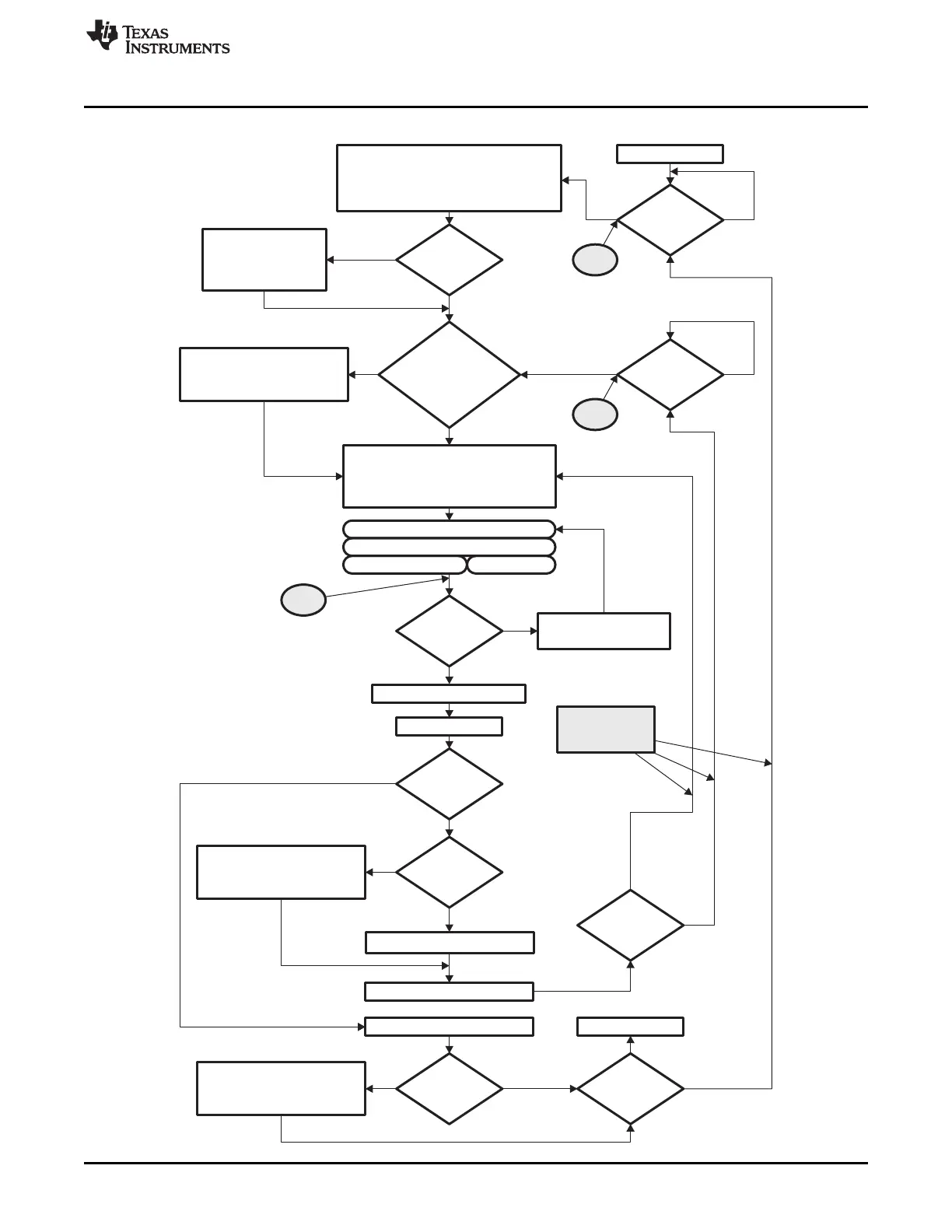

Copy all addr shadow registers

to Active Set

TRANSFER_COUNT = TRANSFER_SIZE

WRAP_COUNT = WRAP_SIZE

TRANSFERSTS = 1

CHINTMODE

== 0

?

Yes

No

Generate DMACHx

interrupt to CPU

at beginning of

transfer (if enabled)

Peripheral

int

?

No

Yes

HALT

here

SYNCE == 1 &

SYNCFLG == 1 &

WRAP_COUNT !=

WRAP_SIZE

?

Yes

No

WRAP_COUNT = WRAP_SIZE

ADDR = BEG_ADDR

SYNCERR = 1

BURST_COUNT = BURST_SIZE

BURSTSTS = 1

Clear PERINTFLG bit

Clear SYNCFLG bit

Peripheral

int

?

No

Yes

HALT

here

Out active SRC_ADDR

Read data

Write data

Out active DST_ADDR

BURST_COUNT--

ADDR += BURST_STEP

BURST_

COUNT

== 0

?

No

BURSTSTS = 0

TRANSFER_

COUNT == 0

?

Yes

No

WRAP_

COUNT == 0

?

Yes

No

BEG_ADDR += WRAP_STEP

ADDR = BEG_ADDR

WRAP_COUNT = WRAP_SIZE

WRAP_COUNT--

TRANSFER_COUNT--

ONESHOT

== 1

?

Yes

No

No

CHINTMODE

== 1

?

Yes

TRANSFERSTS = 0

Generate DMACHx interrupt

to CPU at end of

transfer (if enabled)

CONTINUOUS

== 1

?

RUNSTS = 0

Yes

No

Points where state

machine branches

to next channel

HALT

here

RUNSTS = 1

Yes

ADDR += TRANSFER STEP

www.ti.com

Address Pointer and Transfer Control

507

SPRUI07–March 2020

Submit Documentation Feedback

Copyright © 2020, Texas Instruments Incorporated

Direct Memory Access (DMA) Module

Figure 8-5. DMA State Diagram

Loading...

Loading...