www.ti.com

SPI Registers

575

SPRUI07–March 2020

Submit Documentation Feedback

Copyright © 2020, Texas Instruments Incorporated

Serial Peripheral Interface (SPI)

9.5.2.9 SPIFFTX Register (Offset = Ah) [reset = A000h]

SPIFFTX is shown in Figure 9-16 and described in Table 9-15.

Return to the Summary Table.

SPIFFTX contains both control and status bits related to the output FIFO buffer. This includes FIFO reset

control, FIFO interrupt level control, FIFO level status, as well as FIFO interrupt enable and clear bits.

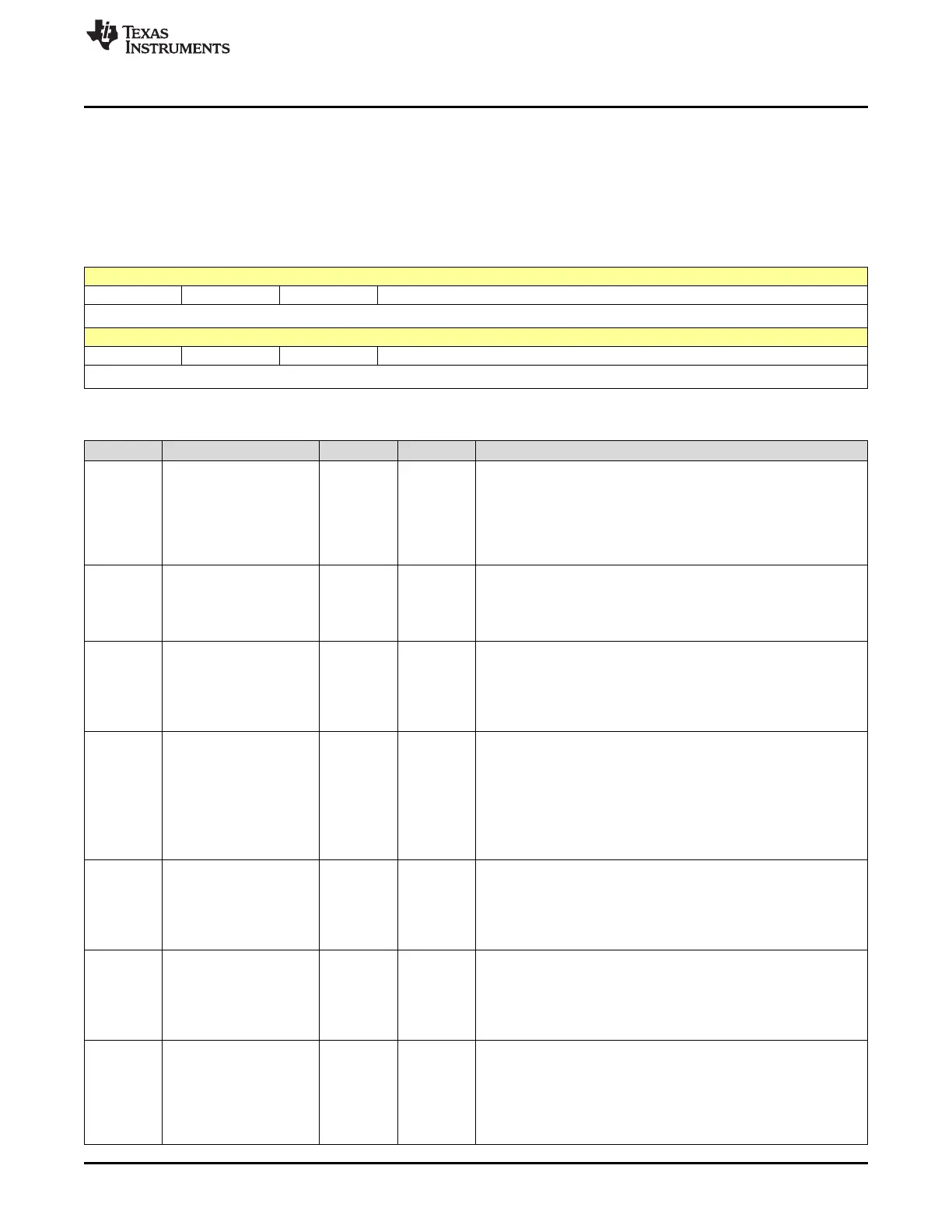

Figure 9-16. SPIFFTX Register

15 14 13 12 11 10 9 8

SPIRST SPIFFENA TXFIFO TXFFST

R/W-1h R/W-0h R/W-1h R-0h

7 6 5 4 3 2 1 0

TXFFINT TXFFINTCLR TXFFIENA TXFFIL

R-0h W-0h R/W-0h R/W-0h

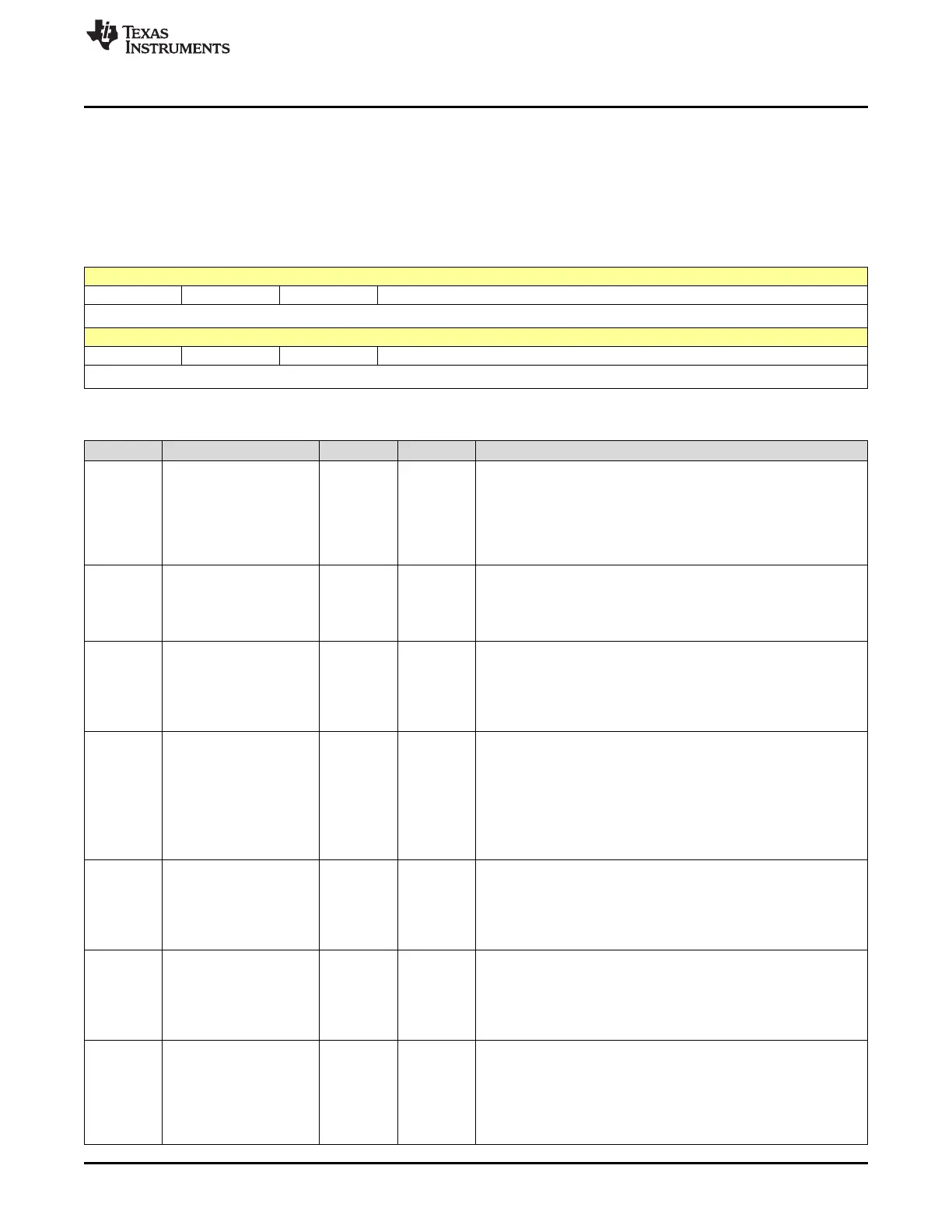

Table 9-15. SPIFFTX Register Field Descriptions

Bit Field Type Reset Description

15 SPIRST R/W 1h

SPI Reset

Reset type: SYSRSn

0h (R/W) = Write 0 to reset the SPI transmit and receive channels.

The SPI FIFO register configuration bits will be left as is.

1h (R/W) = SPI FIFO can resume transmit or receive. No effect to

the SPI registers bits.

14 SPIFFENA R/W 0h

SPI FIFO Enhancements Enable

Reset type: SYSRSn

0h (R/W) = SPI FIFO enhancements are disabled.

1h (R/W) = SPI FIFO enhancements are enabled.

13 TXFIFO R/W 1h

TX FIFO Reset

Reset type: SYSRSn

0h (R/W) = Write 0 to reset the FIFO pointer to zero, and hold in

reset.

1h (R/W) = Release transmit FIFO from reset.

12-8 TXFFST R 0h

Transmit FIFO Status

Reset type: SYSRSn

0h (R/W) = Transmit FIFO is empty.

1h (R/W) = Transmit FIFO has 1 word.

2h (R/W) = Transmit FIFO has 2 words.

10h (R/W) = Transmit FIFO has 16 words, which is the maximum.

1Fh (R/W) = Reserved.

7 TXFFINT R 0h

TX FIFO Interrupt Flag

Reset type: SYSRSn

0h (R/W) = TXFIFO interrupt has not occurred, This is a read-only

bit.

1h (R/W) = TXFIFO interrupt has occurred, This is a read-only bit.

6 TXFFINTCLR W 0h

TXFIFO Interrupt Clear

Reset type: SYSRSn

0h (R/W) = Write 0 has no effect on TXFIFINT flag bit, Bit reads

back a zero.

1h (R/W) = Write 1 to clear SPIFFTX[TXFFINT] flag.

5 TXFFIENA R/W 0h

TX FIFO Interrupt Enable

Reset type: SYSRSn

0h (R/W) = TX FIFO interrupt based on TXFFIL match (less than or

equal to) will be disabled.

1h (R/W) = TX FIFO interrupt based on TXFFIL match (less than or

equal to) will be enabled.

Loading...

Loading...