Borrow

Reset

Timer reload

SYSCLKOUT

TCR.4

(Timer start status)

TINT

16-bit timer divide-down

TDDRH:TDDR

32-bit timer period

PRDH:PRD

32-bit counter

TIMH:TIM

16-bit prescale counter

PSCH:PSC

Borrow

www.ti.com

Clocking and System Control

81

SPRUI07–March 2020

Submit Documentation Feedback

Copyright © 2020, Texas Instruments Incorporated

System Control and Interrupts

Table 1-30. Watchdog Control Register (WDCR) Field Descriptions (continued)

Bits Field Value Description

(1)

5-3 WDCHK Watchdog check.

0,0,0 You must ALWAYS write 1,0,1 to these bits whenever a write to this register is performed

unless the intent is to reset the device via software.

other Writing any other value causes an immediate device reset or watchdog interrupt to be taken.

Note that this will happen even if the watchdog module is disabled. These three bits always

read back as zero (0, 0, 0). This feature can be used to generate a software reset of the DSP.

2-0 WDPS Watchdog pre-scale. These bits configure the watchdog counter clock (WDCLK) rate relative

to OSCCLK/512:

000 WDCLK = OSCCLK/512/1 (default)

001 WDCLK = OSCCLK/512/1

010 WDCLK = OSCCLK/512/2

011 WDCLK = OSCCLK/512/4

100 WDCLK = OSCCLK/512/8

101 WDCLK = OSCCLK/512/16

110 WDCLK = OSCCLK/512/32

111 WDCLK = OSCCLK/512/64

When the XRS line is low, the WDFLAG bit is forced low. The WDFLAG bit is only set if a rising edge on

WDRST signal is detected (after synch and an 8192 SYSCLKOUT cycle delay) and the XRS signal is

high. If the XRS signal is low when WDRST goes high, then the WDFLAG bit remains at 0. In a typical

application, the WDRST signal connects to the XRS input. Hence to distinguish between a watchdog reset

and an external device reset, an external reset must be longer in duration then the watchdog pulse.

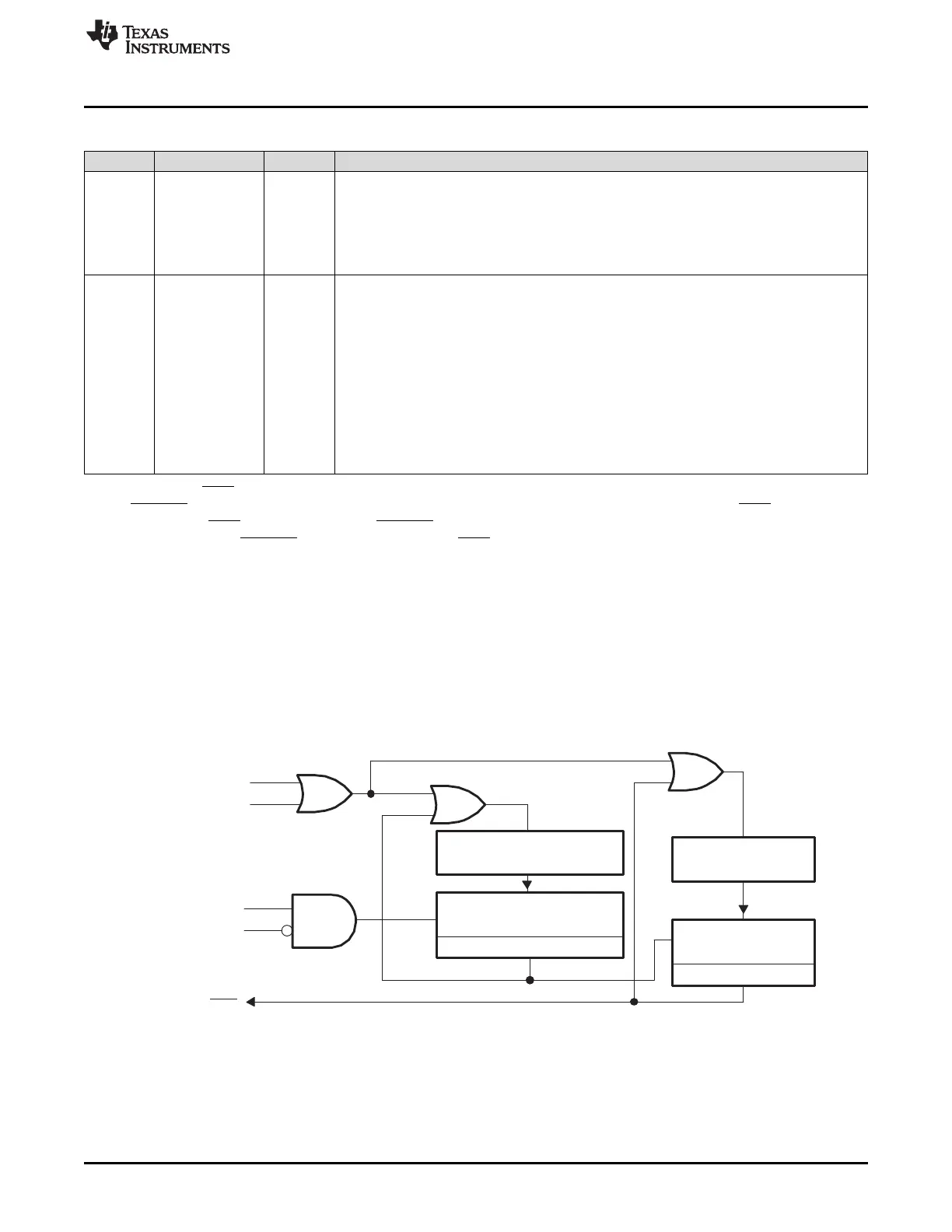

1.3.5 32-Bit CPU Timers 0/1/2

This section describes the three 32-bit CPU timers (Figure 1-31) (TIMER0/1/2).

CPU-Timer 0 and CPU-Timer 1 can be used in user applications. Timer 2 is reserved for DSP/BIOS. If the

application is not using DSP/BIOS, then Timer 2 can be used in the application.

The CPU-timer interrupt signals (TINT0, TINT1, TINT2) are connected as shown in Figure 1-32.

Figure 1-31. CPU Timers

Loading...

Loading...