From CPU or DMA controller

DXR1

To CPU or DMA controller

DRR1

16

16

DX

8

8

XSR1

Compress

Expand

DR

RBR1RSR1

(R/X)SYNCERR

D(R/X)

FS(R/X)

CLK(R/X)

C4C5C6C7B0B1B2B3B4B5B6B7A0

Frame synchronization ignored

Transmitter Configuration

www.ti.com

728

SPRUI07–March 2020

Submit Documentation Feedback

Copyright © 2020, Texas Instruments Incorporated

Multichannel Buffered Serial Port (McBSP)

Figure 12-52. Unexpected Frame-Synchronization Pulse With (R/X) FIG = 1

12.9.12 Transmit Companding Mode

Table 12-59. Register Bits Used to Set the Transmit Companding Mode

Register Bit Name Function Type

Reset

Value

XCR2 4-3 XCOMPAND Transmit companding mode R/W 00

Modes other than 00b are enabled only when the appropriate

XWDLEN is 000b, indicating 8-bit data.

XCOMPAND = 00b No companding, any size data, MSB

transmitted first

XCOMPAND = 01b No companding, 8-bit data, LSB

transmitted first (for details, see

Section 12.8.11.4, Option to Receive

LSB First)

XCOMPAND = 10b μ-law companding, 8-bit data, MSB

transmitted first

XCOMPAND = 11b A-law companding, 8-bit data, MSB

transmitted first

12.9.12.1 Companding

Companding (COMpressing and exPANDing) hardware allows compression and expansion of data in

either μ-law or A-law format. The companding standard employed in the United States and Japan is μ-law.

The European companding standard is referred to as A-law. The specifications for μ-law and A-law log

PCM are part of the CCITT G.711 recommendation.

A-law and μ-law allow 13 bits and 14 bits of dynamic range, respectively. Any values outside this range

are set to the most positive or most negative value. Thus, for companding to work best, the data

transferred to and from the McBSP via the CPU or DMA controller must be at least 16 bits wide.

The μ-law and A-law formats both encode data into 8-bit code words. Companded data is always 8 bits

wide; the appropriate word length bits (RWDLEN1, RWDLEN2, XWDLEN1, XWDLEN2) must therefore be

set to 0, indicating an 8-bit wide serial data stream. If companding is enabled and either of the frame

phases does not have an 8-bit word length, companding continues as if the word length is 8 bits.

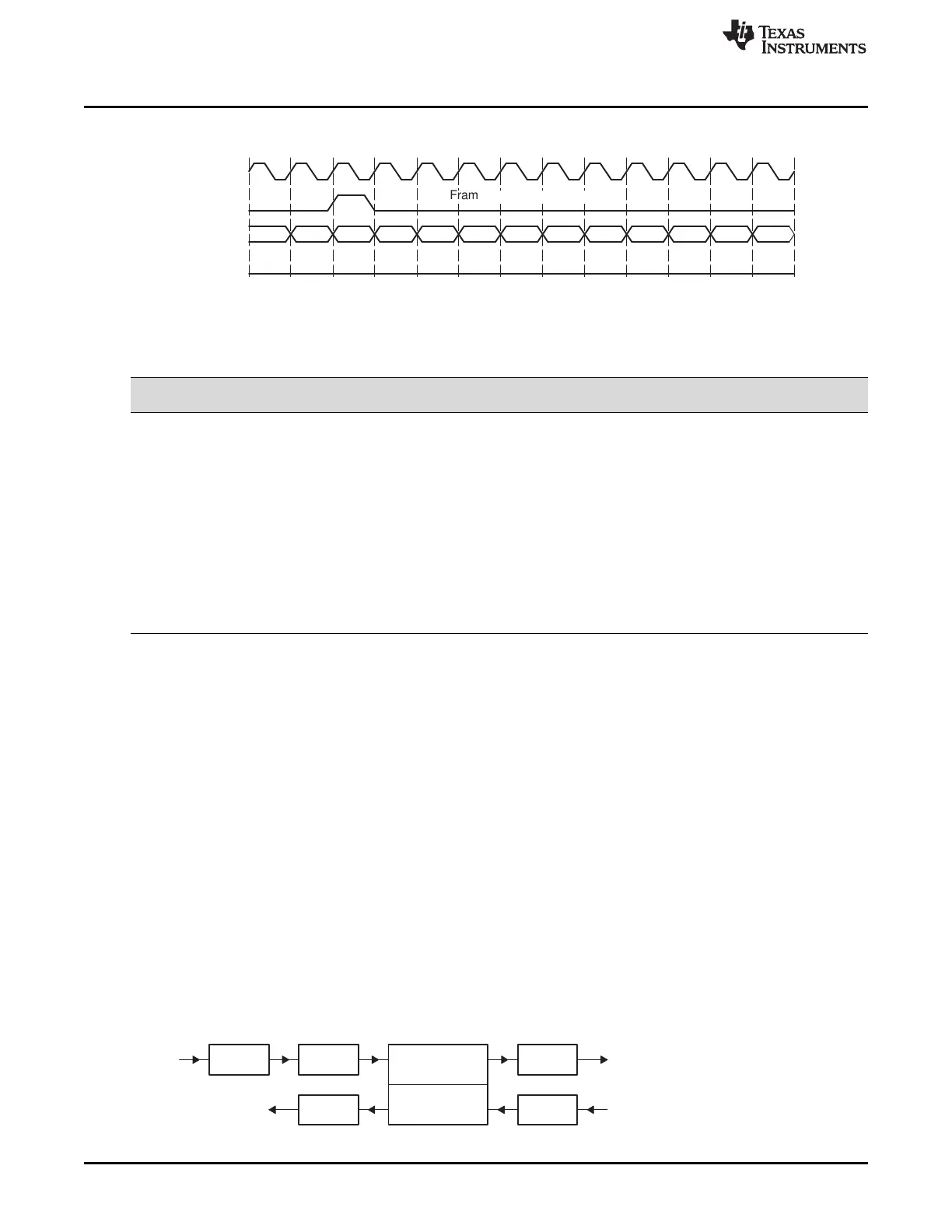

Figure 12-53 illustrates the companding processes. When companding is chosen for the transmitter,

compression occurs during the process of copying data from DXR1 to XSR1. The transmit data is

encoded according to the specified companding law (A-law or μ-law). When companding is chosen for the

receiver, expansion occurs during the process of copying data from RBR1 to DRR1. The receive data is

decoded to twos-complement format.

Figure 12-53. Companding Processes for Reception and for Transmission

Loading...

Loading...