www.ti.com

Clocking and System Control

75

SPRUI07–March 2020

Submit Documentation Feedback

Copyright © 2020, Texas Instruments Incorporated

System Control and Interrupts

Table 1-24. Low Power Modes (continued)

Mode Description

Do not enter HALT low power mode when the device is operating in limp mode (PLLSTS[MCLKSTS] = 1).

If you try to enter HALT mode when the device is already operating in limp mode then the device may not properly enter

HALT. The device may instead enter STANDBY mode or may hang and you may not be able to exit HALT mode. For

this reason, always check that the PLLSTS[MCLKSTS] bit = 0 before entering HALT mode.

When the selected external signal goes low, it is fed asynchronously to the LPM block. The oscillator is turned on and

begins to power up. You must hold the signal low long enough for the oscillator to complete power up. Once the

oscillator has stabilized, the PLL lock sequence is initiated. Once the PLL has locked, it feeds the CLKIN to the CPU at

which time the CPU responds to the WAKEINT interrupt if enabled.

The low-power modes are controlled by the LPMCR0 register (Figure 1-25).

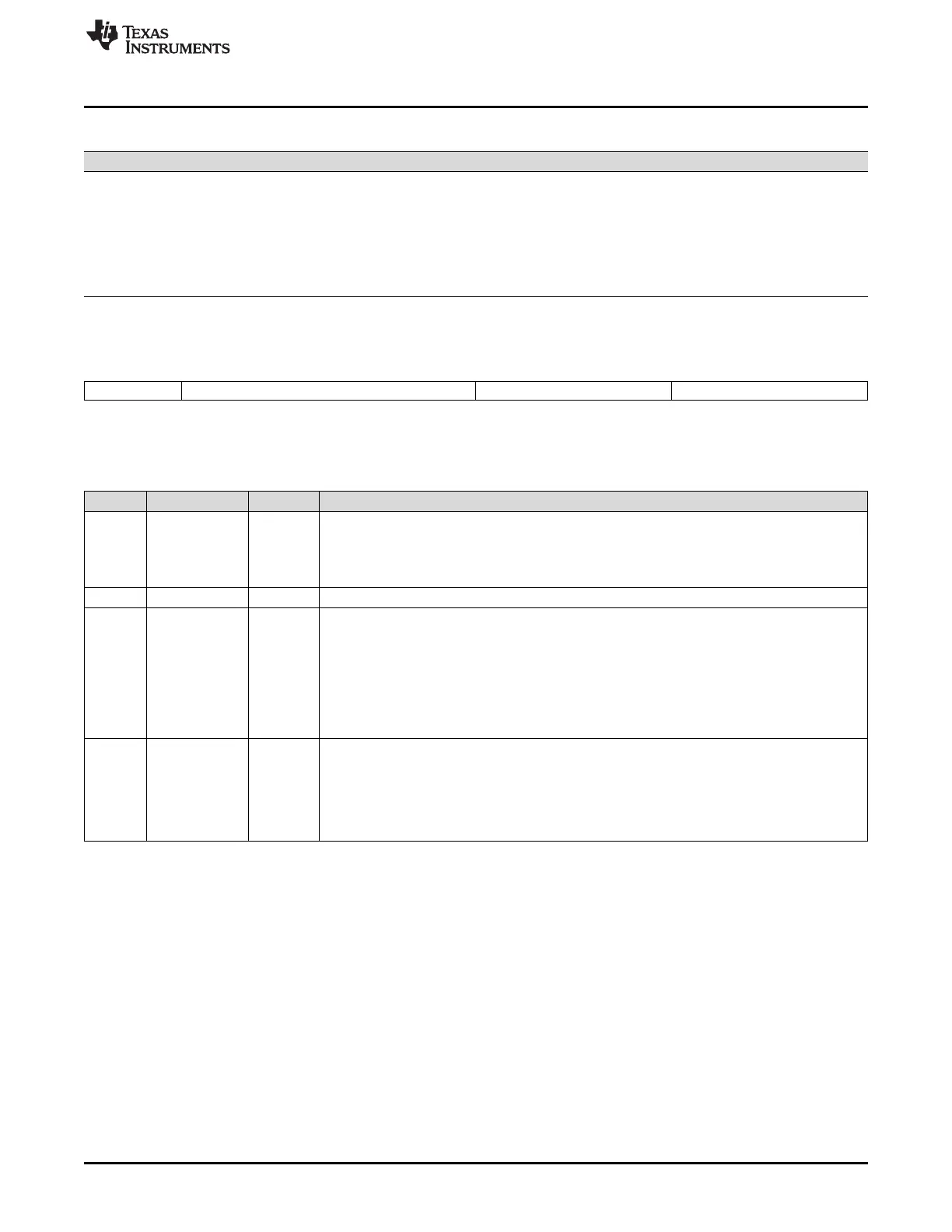

Figure 1-25. Low Power Mode Control 0 Register (LPMCR0)

15 14 8 7 2 1 0

WDINTE Reserved QUALSTDBY LPM

R/W-0 R-0 R/W-1 R/W-0

LEGEND: R/W = Read/Write; R = Read only; -n = value after reset

(1)

This register is EALLOW protected. See Section 1.5.2 for more information.

(2)

The low power mode bits (LPM) only take effect when the IDLE instruction is executed. Therefore, you must set the LPM bits to the

appropriate mode before executing the IDLE instruction.

(3)

If you try to enter HALT mode when the device is already operating in limp mode then the device may not properly enter HALT. The

device may instead enter STANDBY mode or may hang and you may not be able to exit HALT mode. For this reason, always check that

the PLLSTS[MCLKSTS] bit = 0 before entering HALT mode.

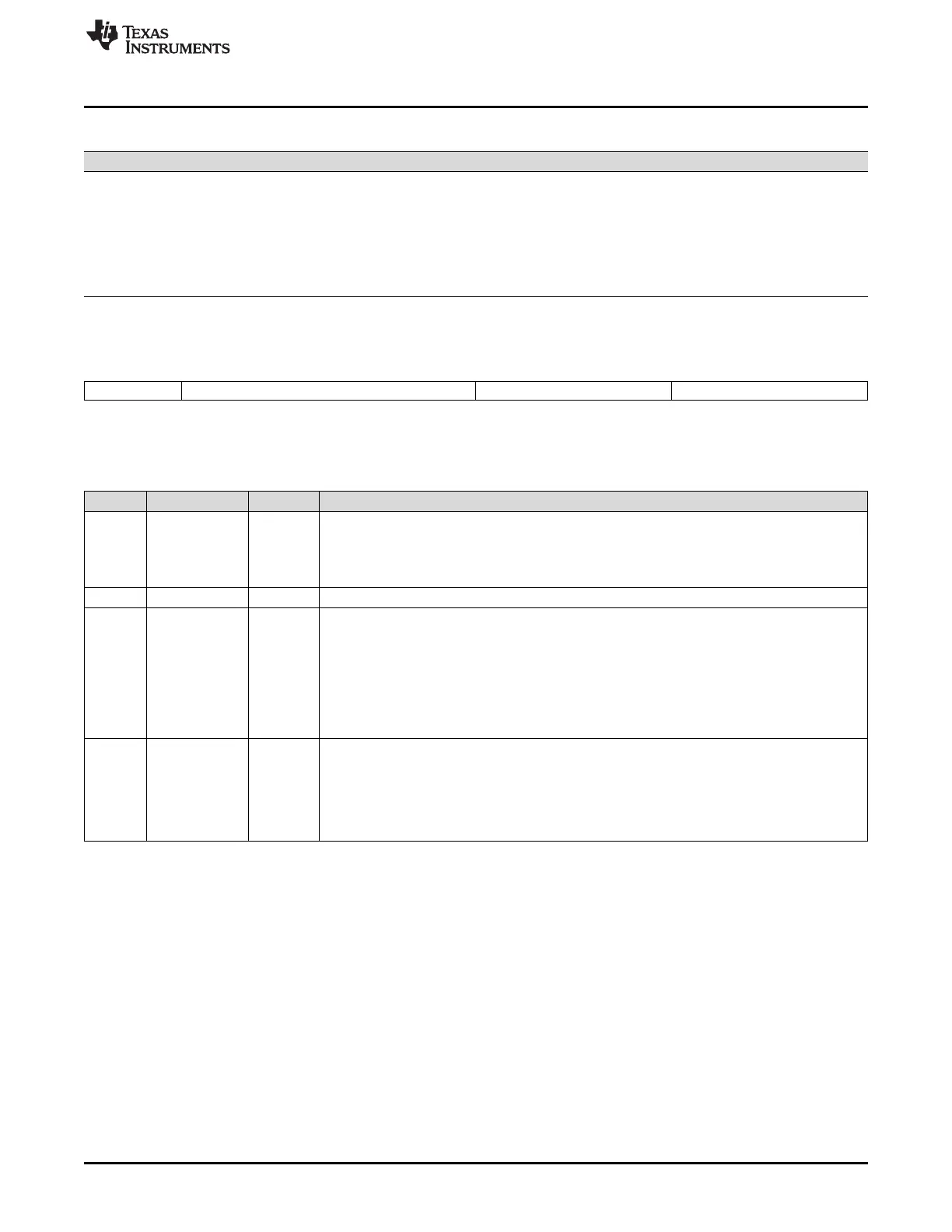

Table 1-25. Low Power Mode Control 0 Register (LPMCR0) Field Descriptions

Bits Field Value Description

(1)

15 WDINTE Watchdog interrupt enable

0 The watchdog interrupt is not allowed to wake the device from STANDBY. (default)

1

The watchdog is allowed to wake the device from STANDBY. The watchdog interrupt must also

be enabled in the SCSR Register.

14-8 Reserved Reserved

7-2 QUALSTDBY Select number of OSCCLK clock cycles to qualify the selected GPIO inputs that wake the device

from STANDBY mode. This qualification is only used when in STANDBY mode. The GPIO

signals that can wake the device from STANDBY are specified in the GPIOLPMSEL register.

000000 2 OSCCLKs (default)

000001 3 OSCCLKs

. . . . . .

111111 65 OSCCLKs

1-0 LPM

(2)

These bits set the low power mode for the device.

00 Set the low power mode to IDLE (default)

01 Set the low power mode to STANDBY

10 Set the low power mode to HALT

(3)

11 Set the low power mode to HALT

(3)

Loading...

Loading...