www.ti.com

SCI Registers

599

SPRUI07–March 2020

Submit Documentation Feedback

Copyright © 2020, Texas Instruments Incorporated

Serial Communications Interface (SCI)

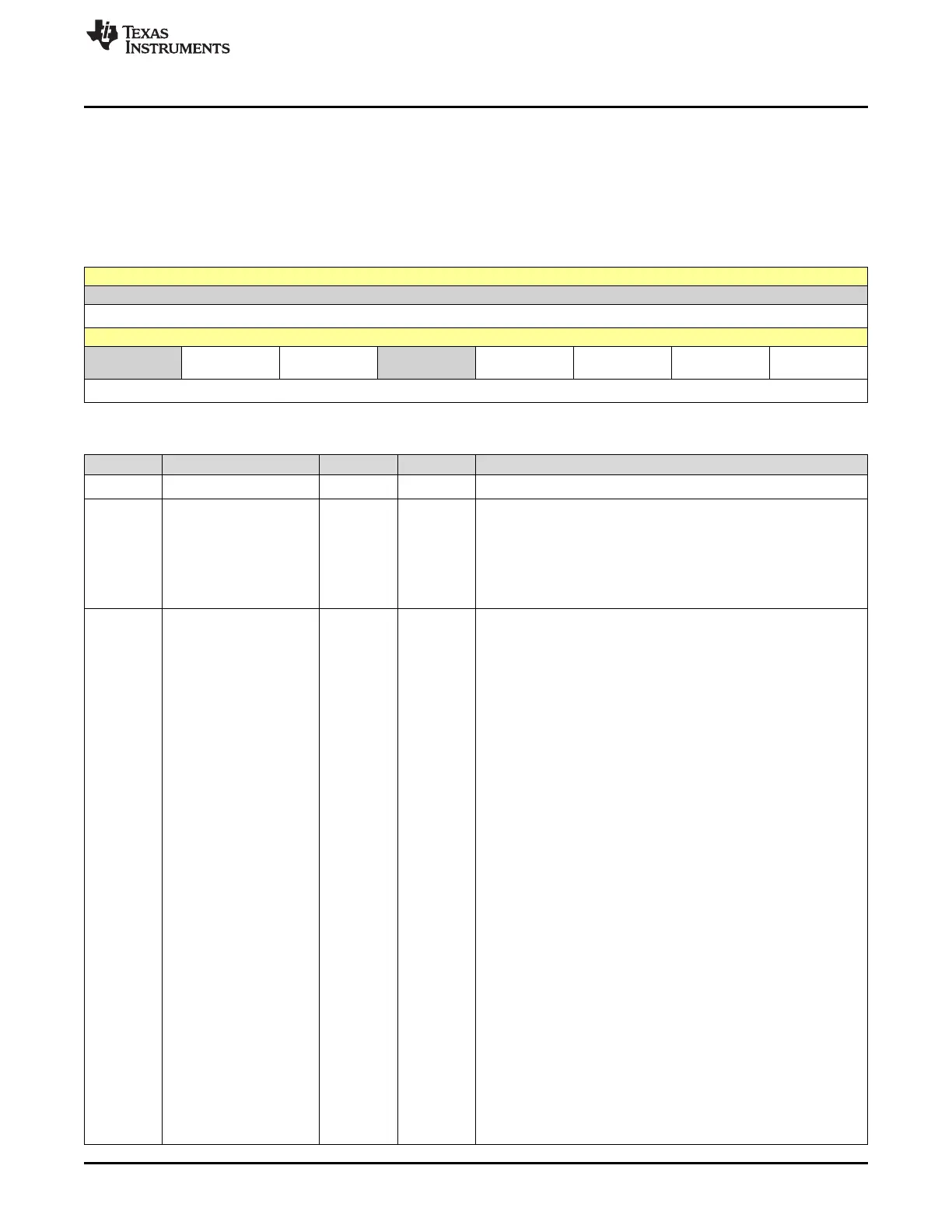

10.14.2.2 SCICTL1 Register (Offset = 1h) [reset = 0h]

SCICTL1 is shown in Figure 10-12 and described in Table 10-8.

Return to the Summary Table.

SCICTL1 controls the receiver/transmitter enable, TXWAKE and SLEEP functions, and the SCI software

reset.

Figure 10-12. SCICTL1 Register

15 14 13 12 11 10 9 8

RESERVED

R-0h

7 6 5 4 3 2 1 0

RESERVED RXERRINTEN

A

SWRESET RESERVED TXWAKE SLEEP TXENA RXENA

R-0h R/W-0h R/W-0h R-0h R/W-0h R/W-0h R/W-0h R/W-0h

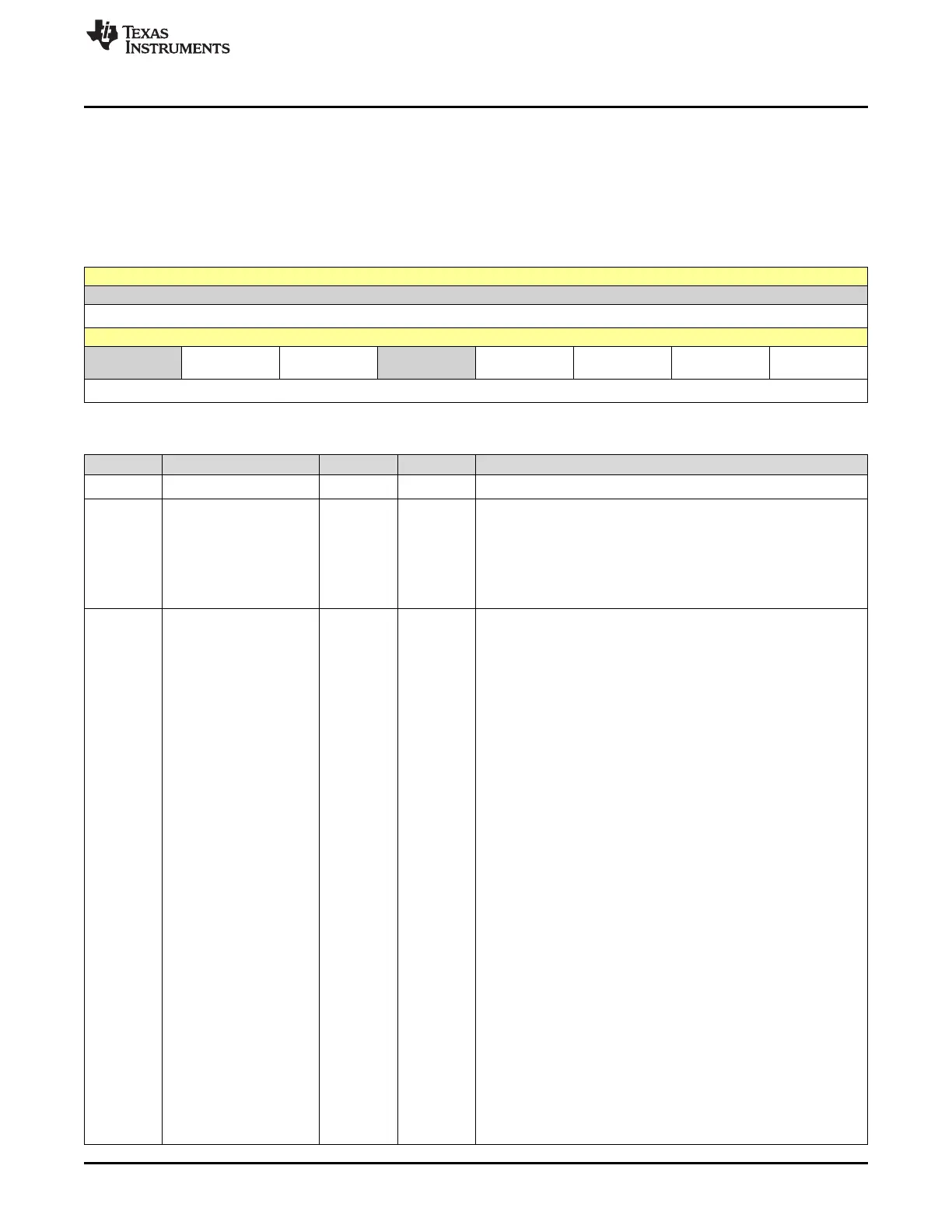

Table 10-8. SCICTL1 Register Field Descriptions

Bit Field Type Reset Description

15-7 RESERVED R 0h

Reserved

6 RXERRINTENA R/W 0h

SCI receive error interrupt enable.

Setting this bit enables an interrupt if the RX ERROR bit (SCIRXST,

bit 7) becomes set because of errors occurring.

Reset type: SYSRSn

0h (R/W) = Receive error interrupt disabled

1h (R/W) = Receive error interrupt enabled

5 SWRESET R/W 0h

SCI software reset (active low).

Writing a 0 to this bit initializes the SCI state machines and operating

flags (registers SCICTL2 and SCIRXST) to the reset condition. The

SW RESET bit does not affect any of the configuration bits.

All affected logic is held in the specified reset state until a 1 is written

to SW RESET (the bit values following a reset are shown beneath

each register diagram in this section). Thus, after a system reset, re-

enable the SCI by writing a 1 to this bit. Clear this bit after a receiver

break detect (BRKDT flag, bit SCIRXST, bit 5).

SW RESET affects the operating flags of the SCI, but it neither

affects the configuration bits nor restores the reset values. Once SW

RESET is asserted, the flags are frozen until the bit is deasserted.

The affected flags are as follows:

Value After SW SCI Flag Register Bit

RESET

1 TXRDY SCICTL2, bit 7

1 TX EMPTY SCICTL2, bit 6

0 RXWAKE SCIRXST, bit 1

0 PE SCIRXST, bit 2

0 OE SCIRXST, bit 3

0 FE SCIRXST, bit 4

0 BRKDT SCIRXST, bit 5

0 RXRDY SCIRXST, bit 6

0 RX ERROR SCIRXST, bit 7

Reset type: SYSRSn

0h (R/W) = Writing a 0 to this bit initializes the SCI state machines

and operating flags (registers SCICTL2 and SCIRXST) to the reset

condition.

1h (R/W) = After a system reset, re-enable the SCI by writing a 1

to this bit.

Loading...

Loading...