SCI Registers

www.ti.com

600

SPRUI07–March 2020

Submit Documentation Feedback

Copyright © 2020, Texas Instruments Incorporated

Serial Communications Interface (SCI)

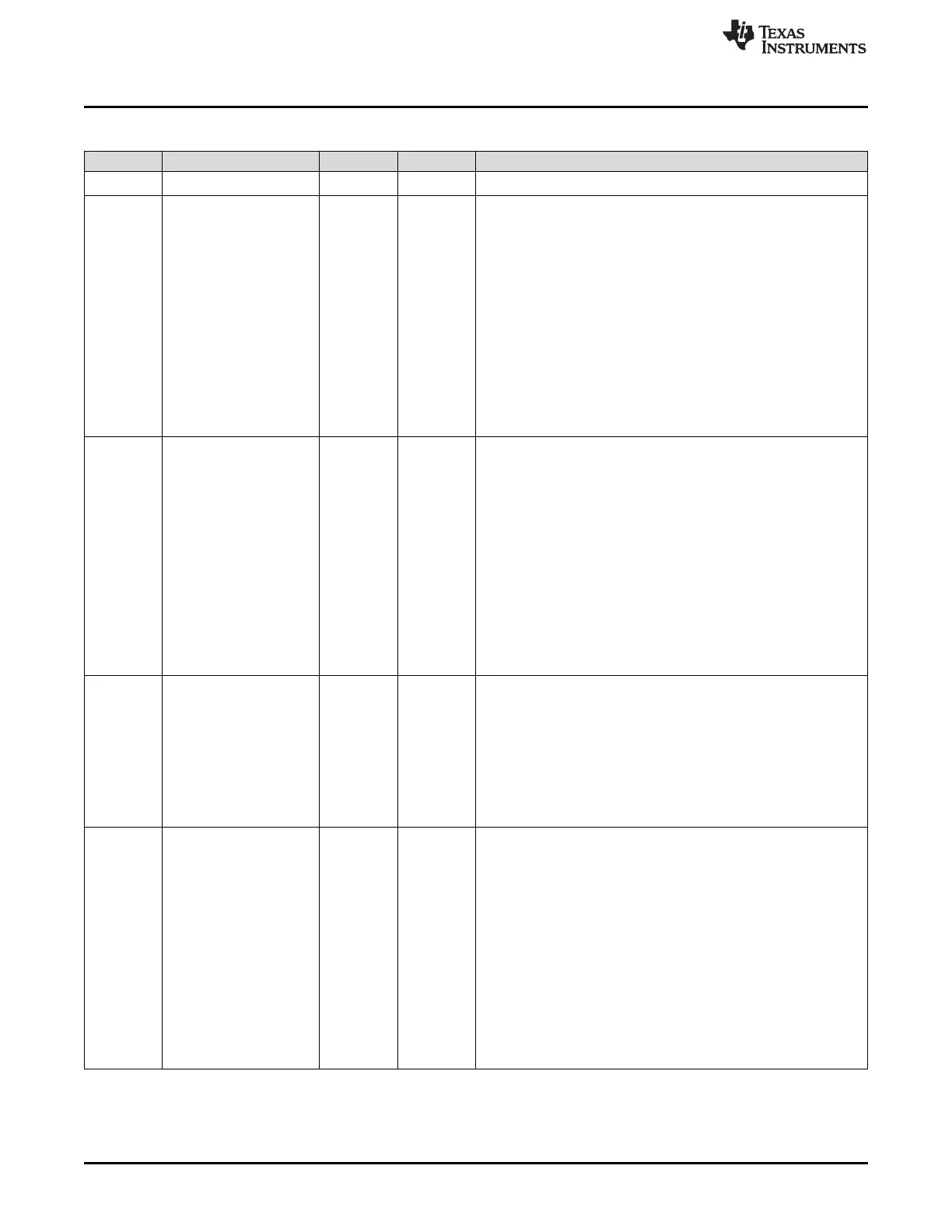

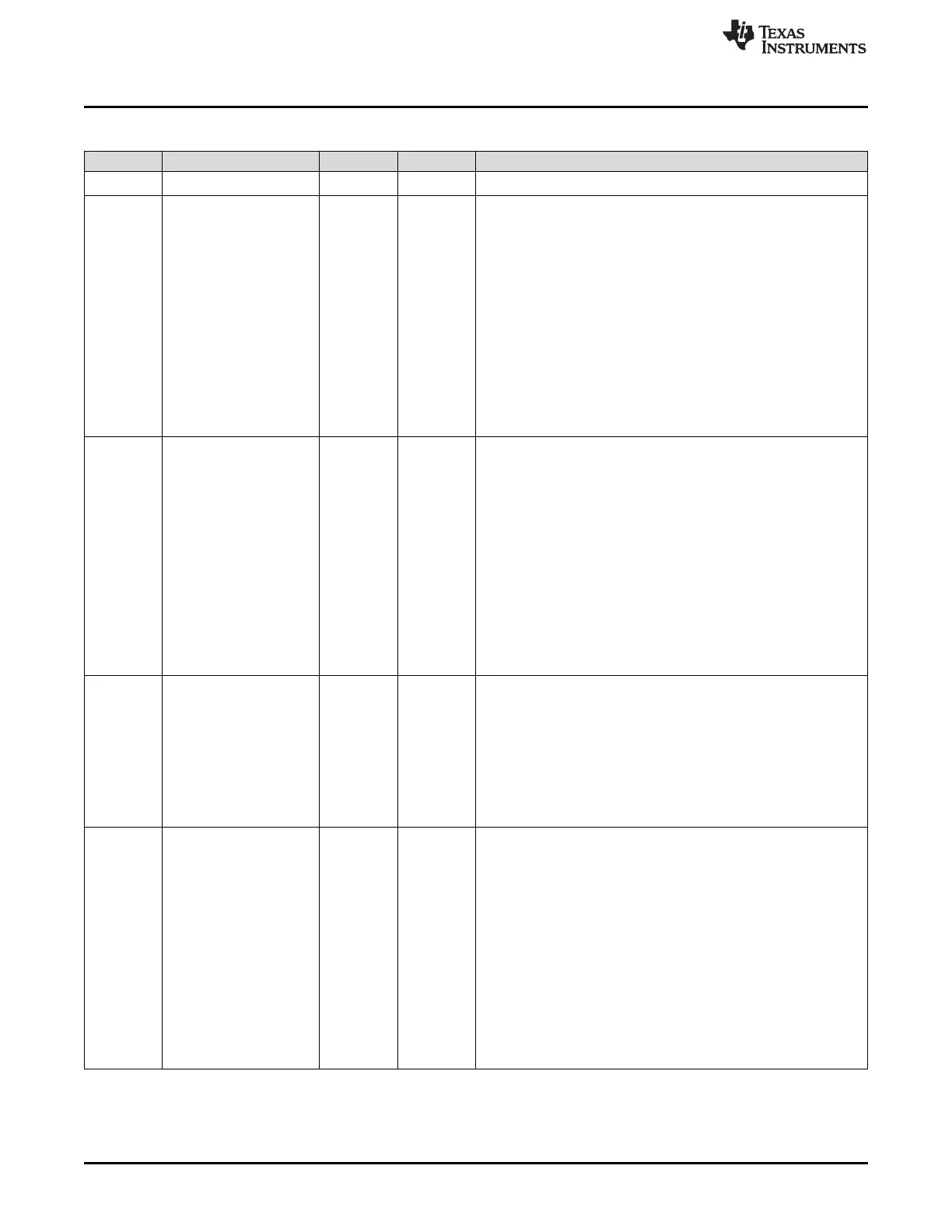

Table 10-8. SCICTL1 Register Field Descriptions (continued)

Bit Field Type Reset Description

4 RESERVED R 0h

Reserved

3 TXWAKE R/W 0h

SCI transmitter wake-up method select.

The TXWAKE bit controls selection of the data-transmit feature,

depending on which transmit mode (idle-line or address-bit) is

specified at the ADDR/IDLE MODE bit (SCICCR, bit 3)

Reset type: SYSRSn

0h (R/W) = Transmit feature is not selected. In idle-line mode: write

a 1 to TXWAKE, then write data to register SCITXBUF to generate

an idle period of 11 data bits In address-bit mode: write a 1 to

TXWAKE, then write data to SCITXBUF to set the address bit for

that frame to 1

1h (R/W) = Transmit feature selected is dependent on the mode,

idle-line or address-bit: TXWAKE is not cleared by the SW RESET

bit (SCICTL1, bit 5)

it is cleared by a system reset or the transfer of TXWAKE to the

WUT flag.

2 SLEEP R/W 0h

SCI sleep.

The TXWAKE bit controls selection of the data-transmit feature,

depending on which transmit mode (idle-line or address-bit) is

specified at the ADDR/IDLE MODE bit (SCICCR, bit 3). In a

multiprocessor configuration, this bit controls the receiver sleep

function. Clearing this bit brings the SCI out of the sleep mode.

The receiver still operates when the SLEEP bit is set

however, operation does not update the receiver buffer ready bit

(SCIRXST, bit 6, RXRDY) or the error status bits (SCIRXST, bit 5-2:

BRKDT, FE, OE, and PE) unless the address byte is detected.

SLEEP is not cleared when the address byte is detected.

Reset type: SYSRSn

0h (R/W) = Sleep mode disabled

1h (R/W) = Sleep mode enabled

1 TXENA R/W 0h

SCI transmitter enable.

Data is transmitted through the SCITXD pin only when TXENA is

set. If reset, transmission is halted but only after all data previously

written to SCITXBUF has been sent. Data written into SCITXBUF

when TXENA is disabled will not be transmitted even if the TXENA is

enabled later.

Reset type: SYSRSn

0h (R/W) = Transmitter disabled

1h (R/W) = Transmitter enabled

0 RXENA R/W 0h

SCI receiver enable.

Data is received on the SCIRXD pin and is sent to the receiver shift

register and then the receiver buffers. This bit enables or disables

the receiver (transfer to the buffers).

Clearing RXENA stops received characters from being transferred to

the two receiver buffers and also stops the generation of receiver

interrupts. However, the receiver shift register can continue to

assemble characters. Thus, if RXENA is set during the reception of a

character, the complete character will be transferred into the receiver

buffer registers, SCIRXEMU and SCIRXBUF.

Reset type: SYSRSn

0h (R/W) = Prevent received characters from transfer into the

SCIRXEMU and SCIRXBUF receiver buffers

1h (R/W) = Send received characters to SCIRXEMU and

SCIRXBUF

Loading...

Loading...