D(R/X)

FS(R/X)

CLK(R/X)

C6C7B0B1B2B3B4B5B6B7A0A1A2

Maximum Frame Frequency +

Clock Frequency

Number of Bits Per Frame

Frame Frequency +

Clock Frequency

Number of Clock Cycles Between Frame- Sync Pulses

www.ti.com

McBSP Operation

665

SPRUI07–March 2020

Submit Documentation Feedback

Copyright © 2020, Texas Instruments Incorporated

Multichannel Buffered Serial Port (McBSP)

12.3.3.5 Ignoring Frame-Synchronization Pulses

The McBSP can be configured to ignore transmit and/or receive frame-synchronization pulses. To have

the receiver or transmitter recognize frame-synchronization pulses, clear the appropriate frame-

synchronization ignore bit (RFIG = 0 for the receiver, XFIG = 0 for the transmitter). To have the receiver or

transmitter ignore frame-synchronization pulses until the desired frame length or number of words is

reached, set the appropriate frame-synchronization ignore bit (RFIG = 1 for the receiver, XFIG = 1 for the

transmitter). For more details on unexpected frame-synchronization pulses, see one of the following

topics:

• Unexpected Receive Frame-Synchronization Pulse (see Section 12.5.3)

• Unexpected Transmit Frame-Synchronization Pulse (see Section 12.5.6)

You can also use the frame-synchronization ignore function for data packing (for more details, see

Section 12.11.2).

12.3.3.6 Frame Frequency

The frame frequency is determined by the period between frame-synchronization pulses and is defined as

shown by Example 1.

Example 1: McBSP Frame Frequency

The frame frequency can be increased by decreasing the time between frame-synchronization pulses

(limited only by the number of bits per frame). As the frame transmit frequency increases, the inactivity

period between the data packets for adjacent transfers decreases to zero.

12.3.3.7 Maximum Frame Frequency

The minimum number of clock cycles between frame synchronization pulses is equal to the number of bits

transferred per frame. The maximum frame frequency is defined as shown by Example 2.

Example 2: McBSP Maximum Frame Frequency

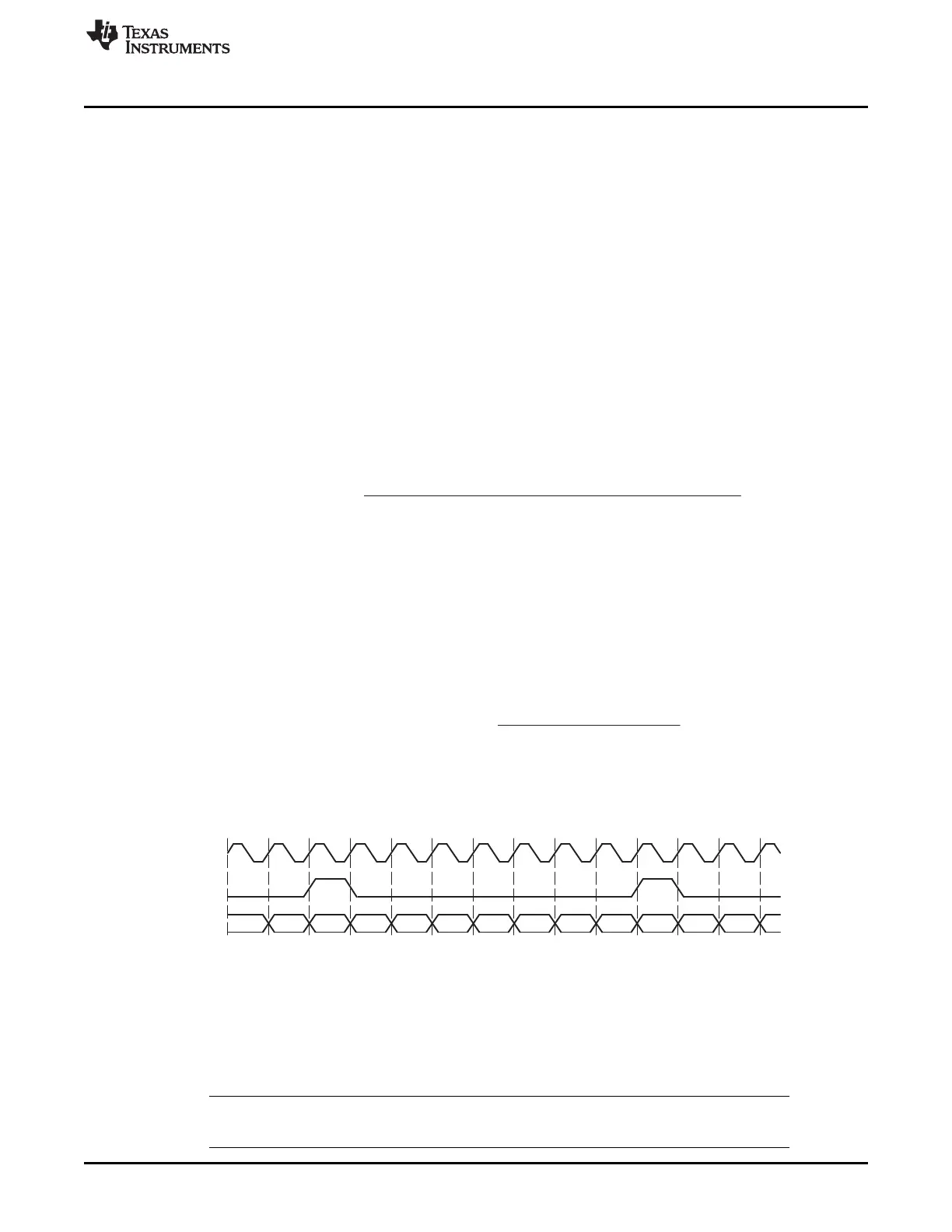

Figure 12-8 shows the McBSP operating at maximum packet frequency. At maximum packet frequency,

the data bits in consecutive packets are transmitted contiguously with no inactivity between bits.

Figure 12-8. McBSP Operating at Maximum Packet Frequency

If there is a 1-bit data delay as shown in this figure, the frame-synchronization pulse overlaps the last bit

transmitted in the previous frame. Effectively, this permits a continuous stream of data, making frame-

synchronization pulses redundant. Theoretically, only an initial frame-synchronization pulse is required to

initiate a multipacket transfer.

The McBSP supports operation of the serial port in this fashion by ignoring the successive frame-

synchronization pulses. Data is clocked into the receiver or clocked out of the transmitter during every

clock cycle.

NOTE: For XDATDLY = 0 (0-bit data delay), the first bit of data is transmitted asynchronously to the

internal transmit clock signal (CLKX). For more details, see Section 12.9.13.

Loading...

Loading...