Current data retransmitted

New data received

(R/X)SYNCERR

DX

DR

FS(R/X)

CLK(R/X)

C6C7B0

B2B3B4B5B7 B6B6B7A0 B1

D6D7C0C1C2C3C4C5C6C7B6B7A0

Frame synchronization aborts current transfer

www.ti.com

Transmitter Configuration

727

SPRUI07–March 2020

Submit Documentation Feedback

Copyright © 2020, Texas Instruments Incorporated

Multichannel Buffered Serial Port (McBSP)

12.9.11 Enable/Disable the Transmit Frame-Synchronization Ignore Function

Table 12-58. Register Bit Used to Enable/Disable the Transmit Frame-Synchronization Ignore

Function

Register Bit Name Function Type

Reset

Value

XCR2 2 XFIG Transmit frame-synchronization ignore R/W 0

XFIG = 0 An unexpected transmit frame-synchronization

pulse causes the McBSP to restart the frame

transfer.

XFIG = 1 The McBSP ignores unexpected transmit frame-

synchronization pulses.

12.9.11.1 Unexpected Frame-Synchronization Pulses and Frame-Synchronization Ignore

If a frame-synchronization pulse starts the transfer of a new frame before the current frame is fully

transmitted, this pulse is treated as an unexpected frame-synchronization pulse.

When XFIG = 1, normal transmission continues with unexpected frame-synchronization signals ignored.

When XFIG = 0 and an unexpected frame-synchronization pulse occurs, the serial port:

1. Aborts the present transmission

2. Sets XSYNCERR to 1 in SPCR2

3. Reinitiates transmission of the current word that was aborted

For more details about the frame-synchronization error condition, see Section 12.5.6.

12.9.11.2 Examples Showing the Effects of XFIG

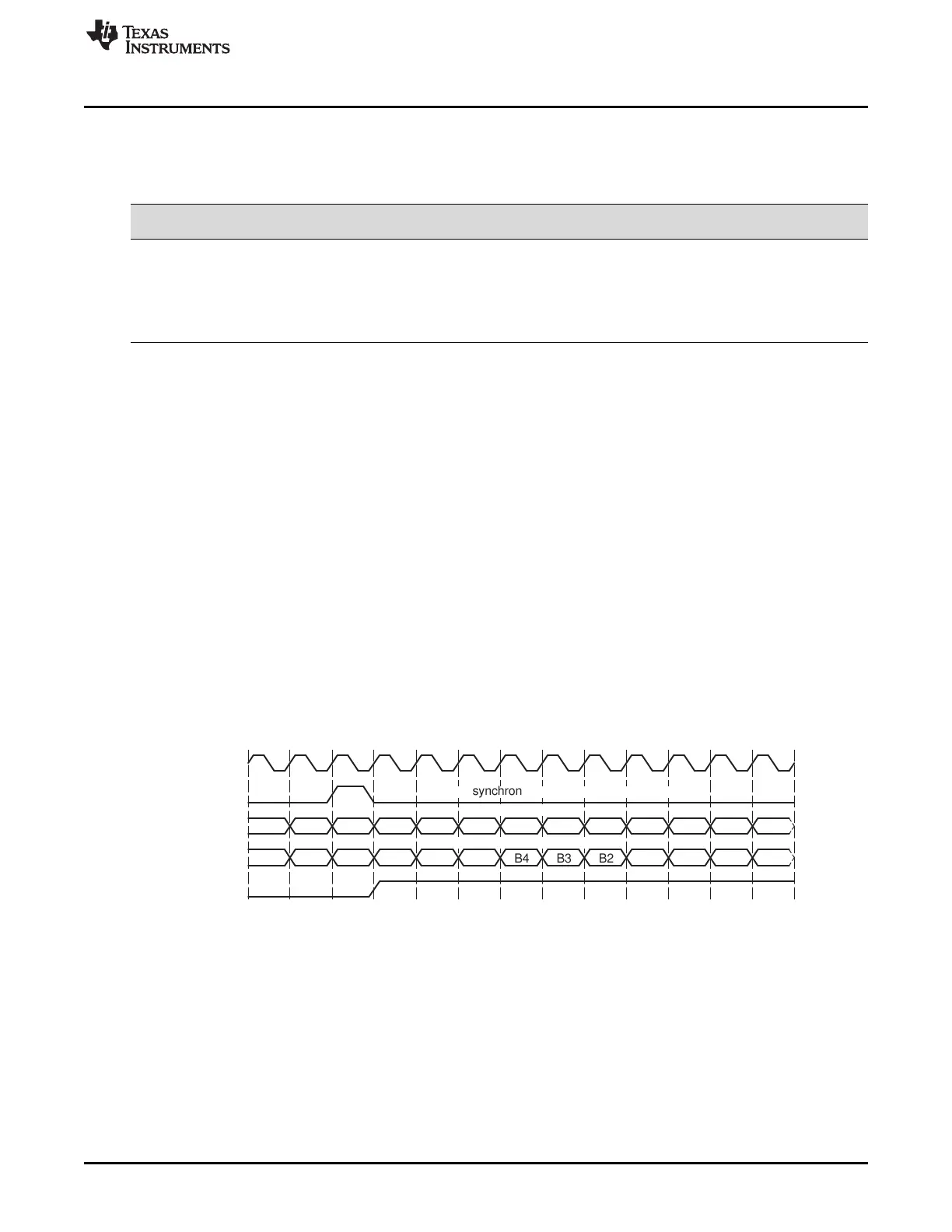

Figure 12-51 shows an example in which word B is interrupted by an unexpected frame-synchronization

pulse when (R/X)FIG = 0. In the case of transmission, the transmission of B is aborted (B is lost). This

condition is a transmit synchronization error, which sets the XSYNCERR bit. No new data has been

written to DXR[1,2]; therefore, the McBSP transmits B again.

Figure 12-51. Unexpected Frame-Synchronization Pulse With (R/X) FIG = 0

In contrast with Figure 12-51, Figure 12-52 shows McBSP operation when unexpected frame-

synchronization signals are ignored (when (R/X)FIG = 1). Here, the transfer of word B is not affected by

an unexpected frame-synchronization pulse.

Loading...

Loading...