www.ti.com

I2C Registers

641

SPRUI07–March 2020

Submit Documentation Feedback

Copyright © 2020, Texas Instruments Incorporated

Inter-Integrated Circuit Module (I2C)

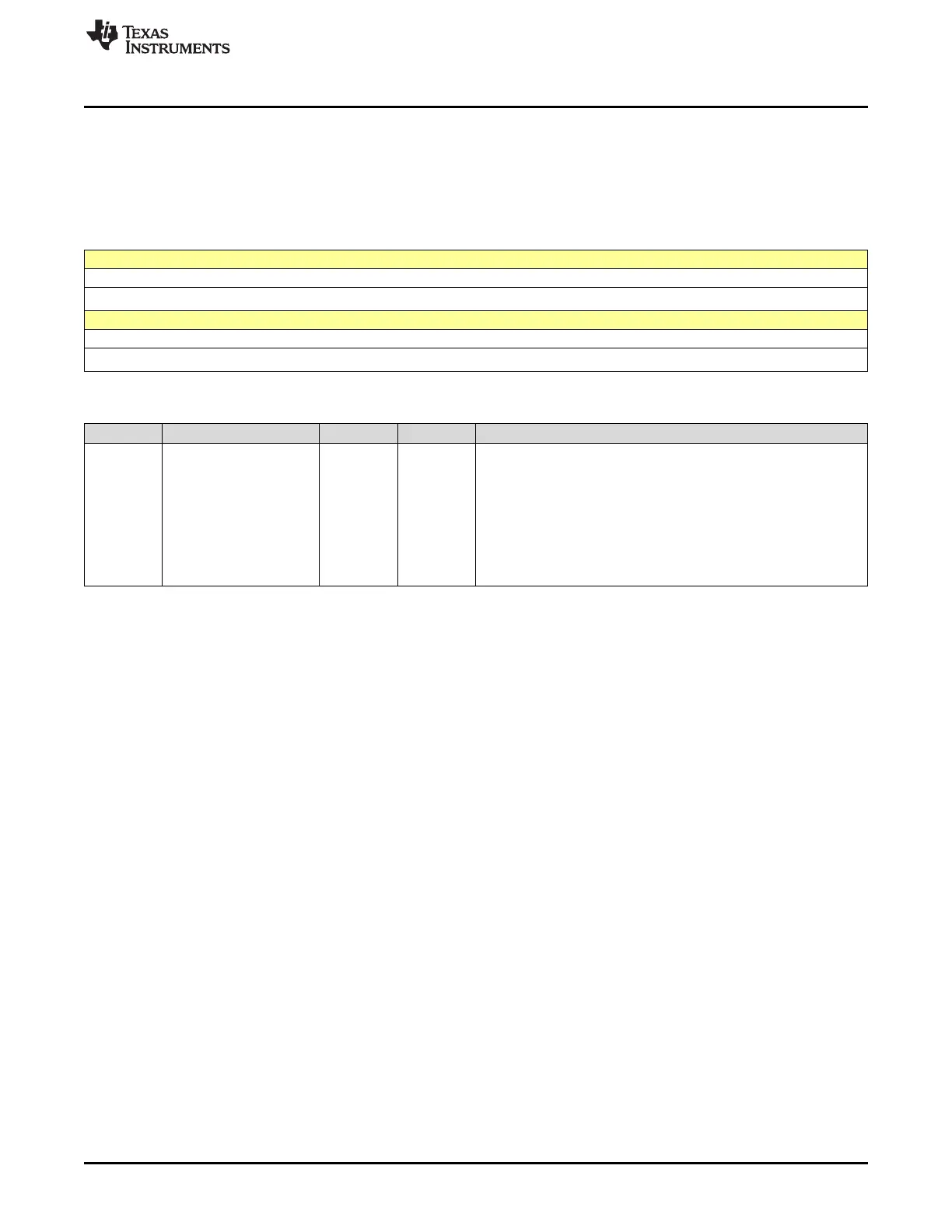

11.6.2.5 I2CCLKH Register (Offset = 4h) [reset = 0h]

I2CCLKH is shown in Figure 11-22 and described in Table 11-14.

Return to the Summary Table.

I2C Clock high-time divider

Figure 11-22. I2CCLKH Register

15 14 13 12 11 10 9 8

I2CCLKH

R/W-0h

7 6 5 4 3 2 1 0

I2CCLKH

R/W-0h

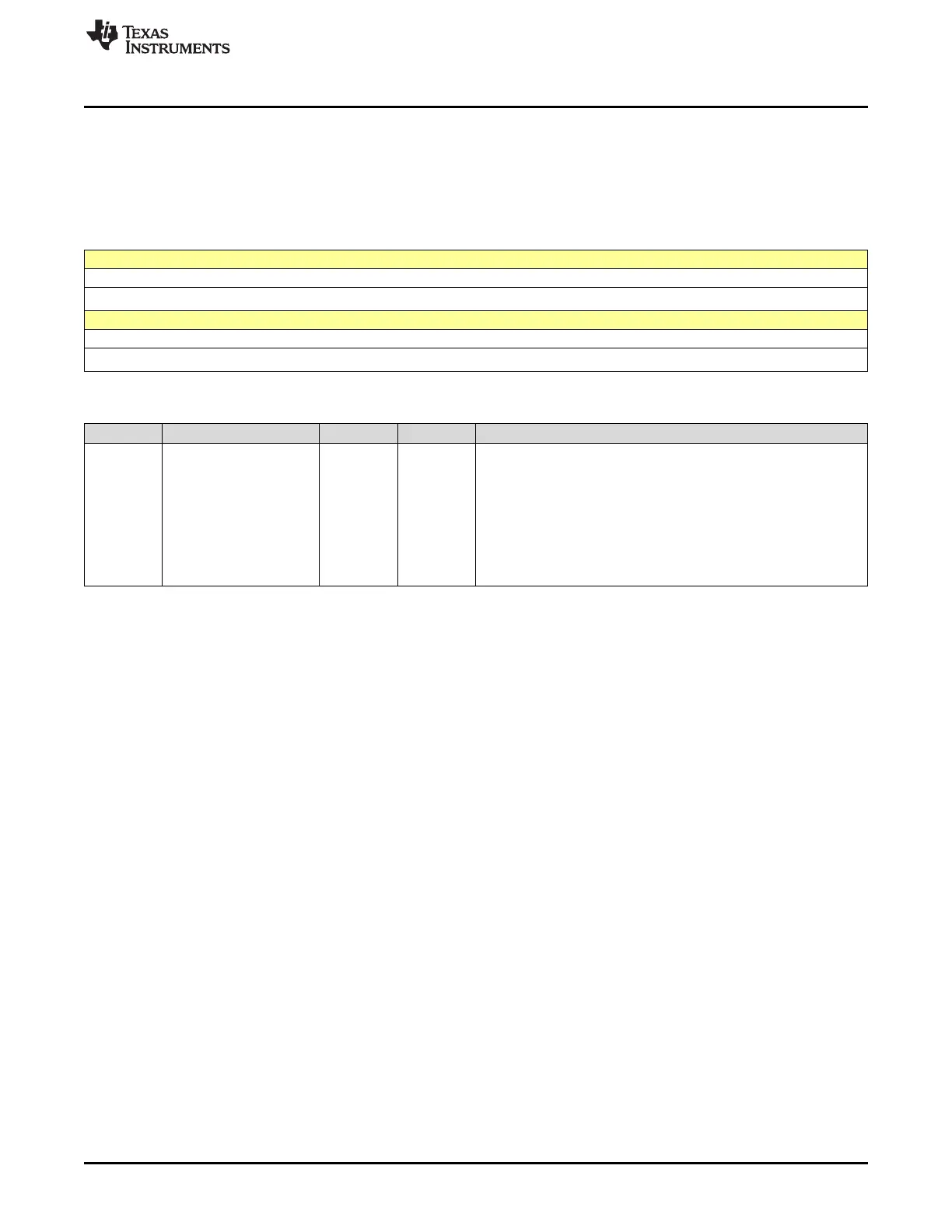

Table 11-14. I2CCLKH Register Field Descriptions

Bit Field Type Reset Description

15-0 I2CCLKH R/W 0h

Clock high-time divide-down value.

To produce the high time duration of the master clock, the period of

the module clock is multiplied by (ICCL + d). d is an adjustment

factor based on the prescaler. See the Clock Divider Registers

section of the Introduction for details.

Note: These bits must be set to a non-zero value for proper I2C

clock generation.

Reset type: SYSRSn

Loading...

Loading...