www.ti.com

ADC Interface

465

SPRUI07–March 2020

Submit Documentation Feedback

Copyright © 2020, Texas Instruments Incorporated

Analog-to-Digital Converter (ADC)

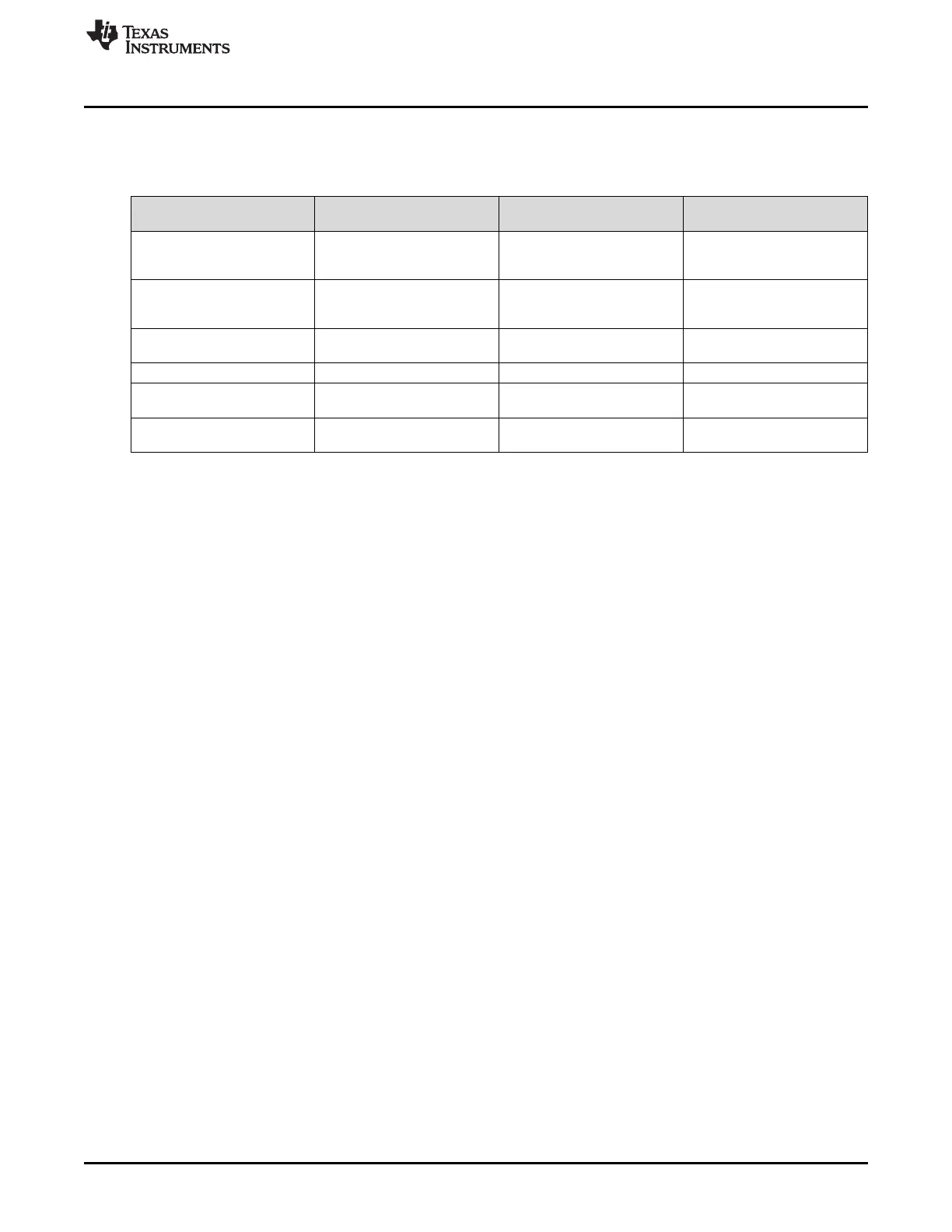

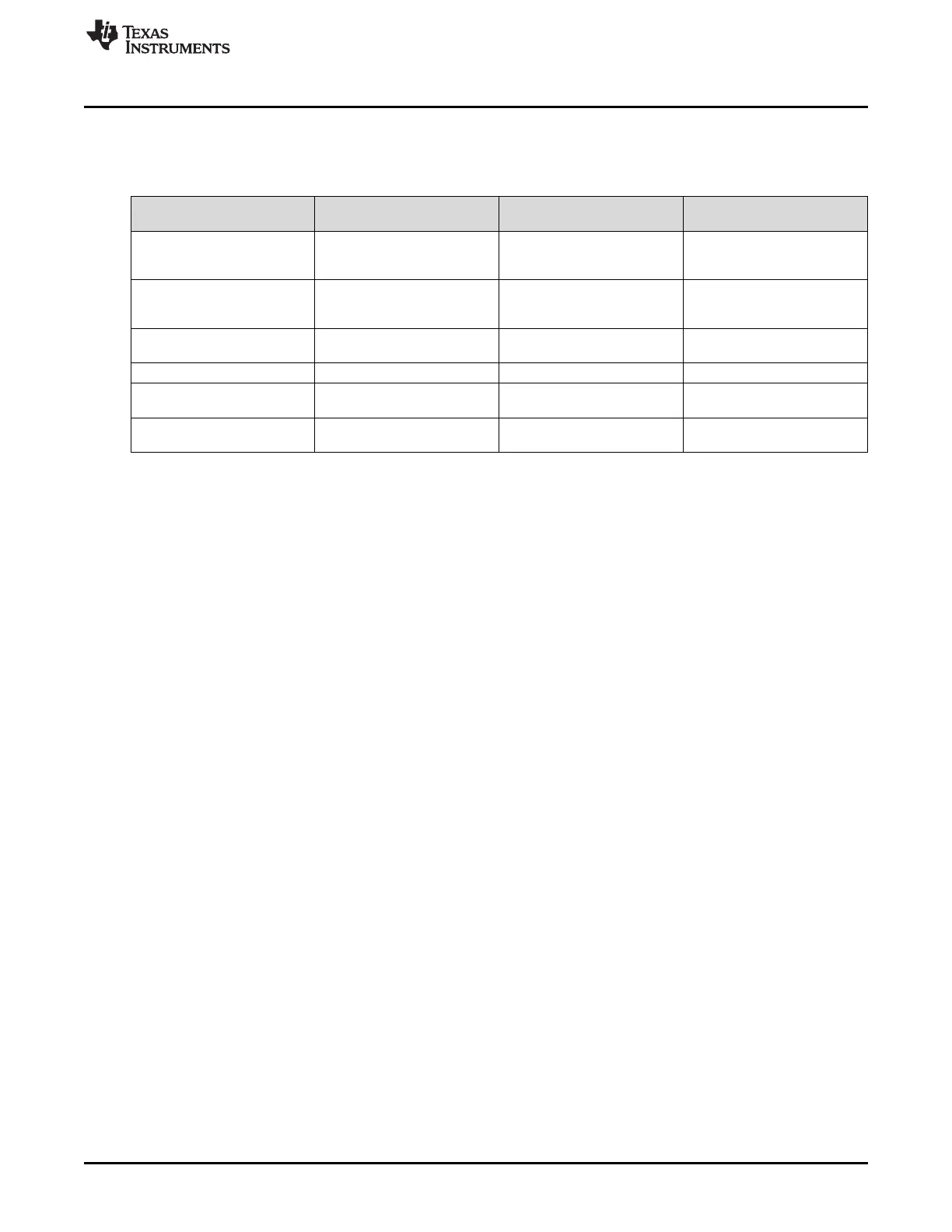

The sequencer operation for both 8-state and 16-state modes is almost identical; the few differences are

highlighted in Table 7-5.

Table 7-5. Comparison of Single and Cascaded Operating Modes

Feature

Single 8-state sequencer #1

(SEQ1)

Single 8-state

sequencer #2 (SEQ2)

Cascaded 16-state

sequencer (SEQ)

Start-of-conversion (SOC)

triggers

ePWMx SOCA, software,

external pin

ePWMx SOCB, software ePWMx SOCA, ePWMx

SOCB, software,

external pin

Maximum number of

autoconversions

(that is, sequence length)

8 8 16

Autostop at end-of-

sequence (EOS)

Yes Yes Yes

Arbitration priority High Low Not applicable

ADC conversion result register

locations

0 to 7 8 to 15 0 to 15

ADCCHSELSEQn bit field

assignment

CONV00 to CONV07 CONV08 to CONV15 CONV00 to CONV15

For convenience, the sequencer states will be subsequently referred to as:

• For SEQ1: CONV00 to CONV07

• For SEQ2: CONV08 to CONV15

• For Cascaded SEQ: CONV00 to CONV15

The analog input channel selected for each sequenced conversion is defined by CONVxx bit fields in the

ADC input channel select sequencing control registers (ADCCHSELSEQn). CONVxx is a 4-bit field that

specifies any one of the 16 channels for conversion. Since a maximum of 16 conversions in a sequence is

possible when using the sequencers in cascaded mode, 16 such 4-bit fields (CONV00 - CONV15) are

available and are spread across four 16-bit registers (ADCCHSELSEQ1 - ADCCHSELSEQ4). The

CONVxx bits can have any value from 0 to 15. The analog channels can be chosen in any desired order

and the same channel may be selected multiple times.

Loading...

Loading...