XINTF Registers

www.ti.com

852

SPRUI07–March 2020

Submit Documentation Feedback

Copyright © 2020, Texas Instruments Incorporated

External Interface (XINTF)

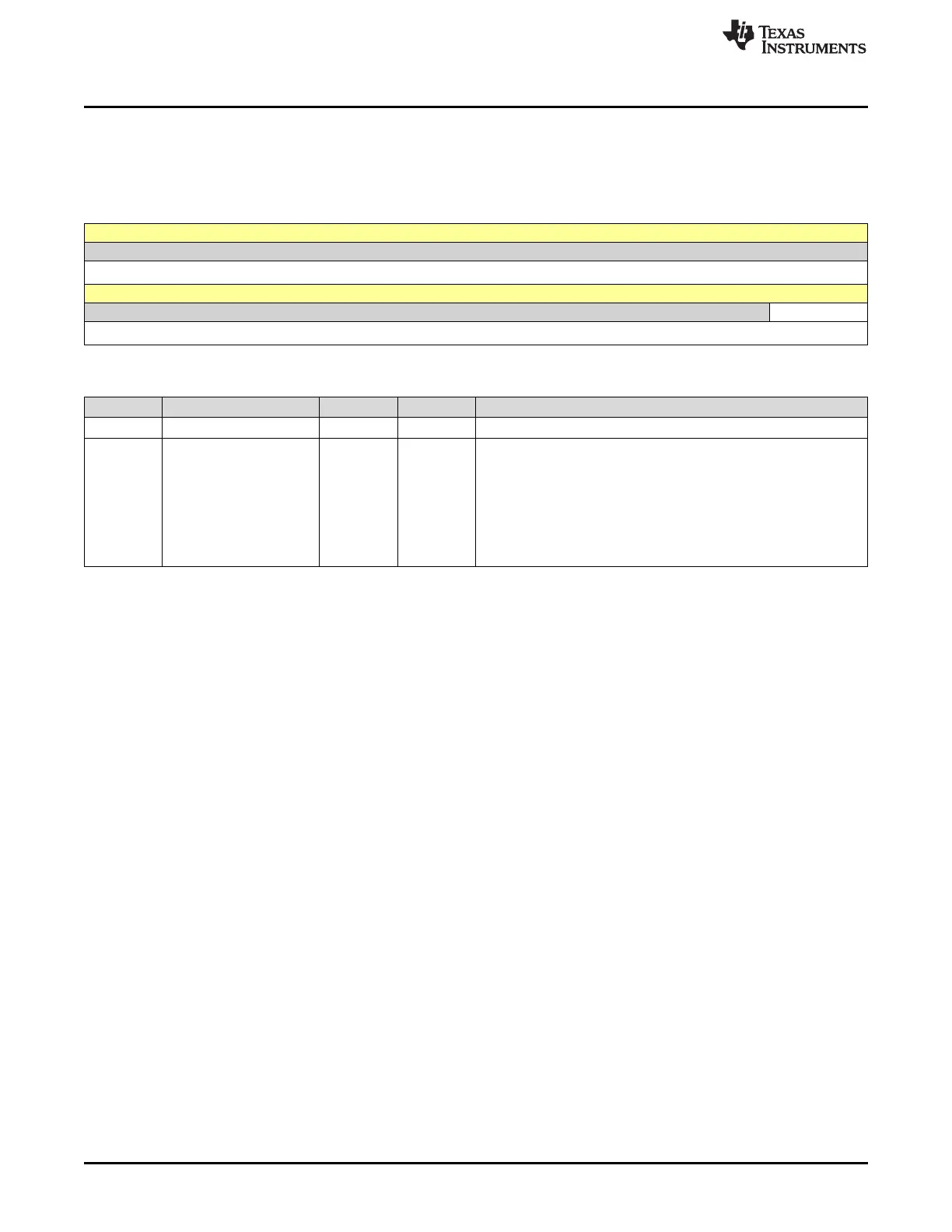

14.6.1 XRESET Register (Offset = 83Dh) [reset = 0h]

XRESET is shown in Figure 14-6 and described in Table 14-8.

This register is EALLOW protected.

Figure 14-6. XRESET Register

15 14 13 12 11 10 9 8

RESERVED

R-0h

7 6 5 4 3 2 1 0

RESERVED XHARDRESET

R-0h R/W-0h

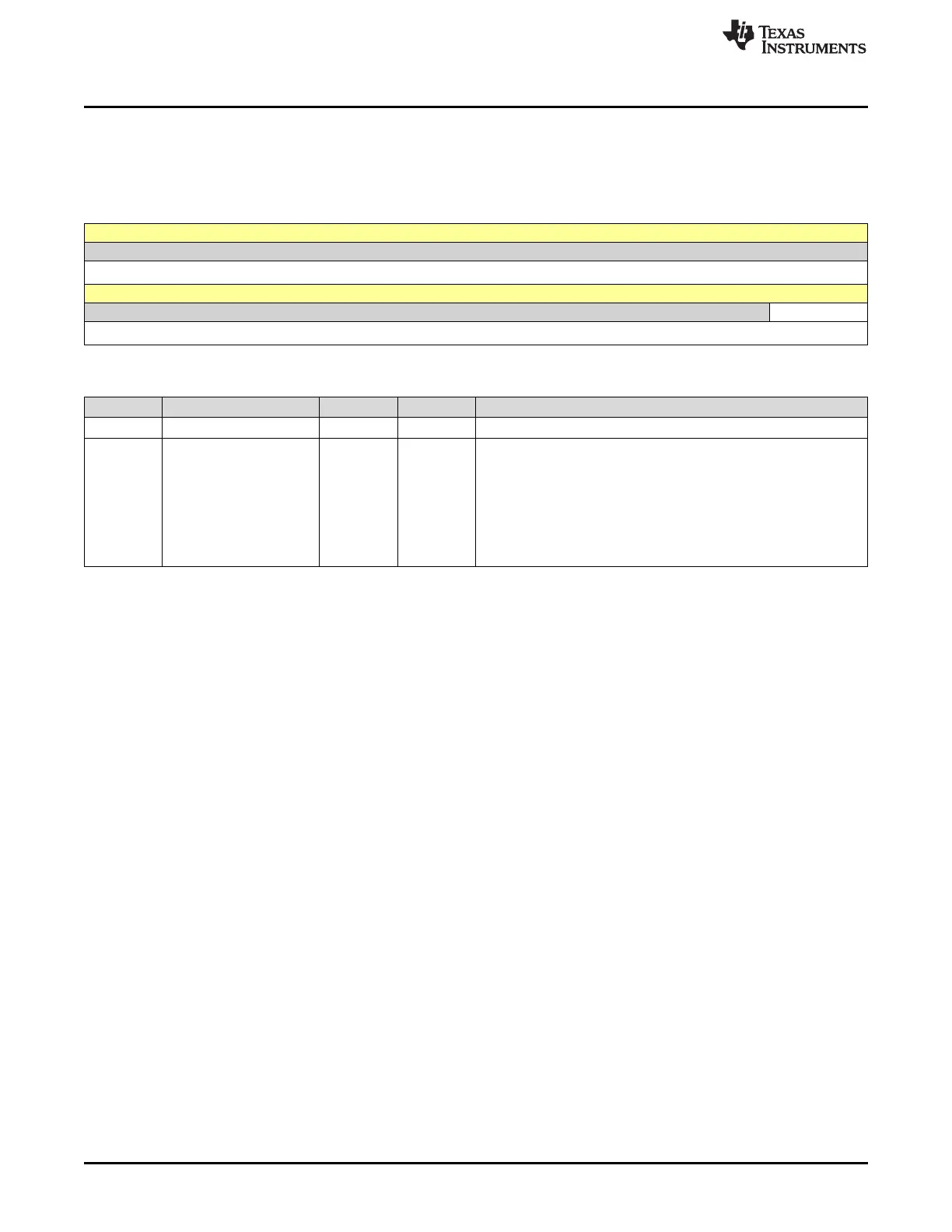

Table 14-8. XRESET Register Field Descriptions

Bit Field Type Reset Description

15-1 RESERVED R 0h

0 XHARDRESET R/W 0h

A hard reset may be used in cases where the CPU detects the

XREADY signal is stuck low during a DMA transfer.

0h = Writing a 0 has no effect. This bit always reads back a 0.

1h = Force an XINTF hard reset. The XTIMING, XBANK, and

XINTCNF2 registers will return to their default state and all XINTF

signals will go to their inactive state. Any pending access will be lost

including data in the write buffer. Any stall condition to DMA will be

released.

Loading...

Loading...