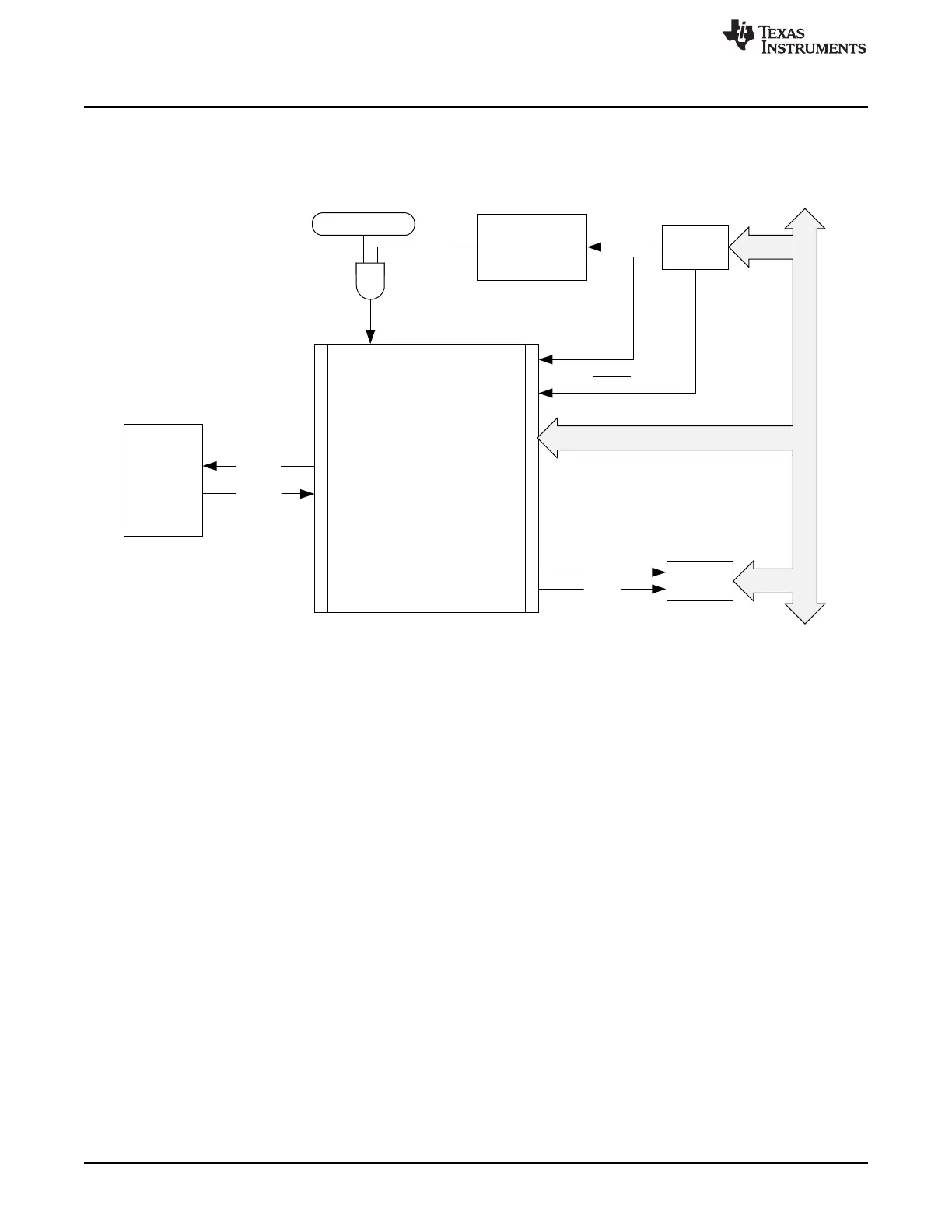

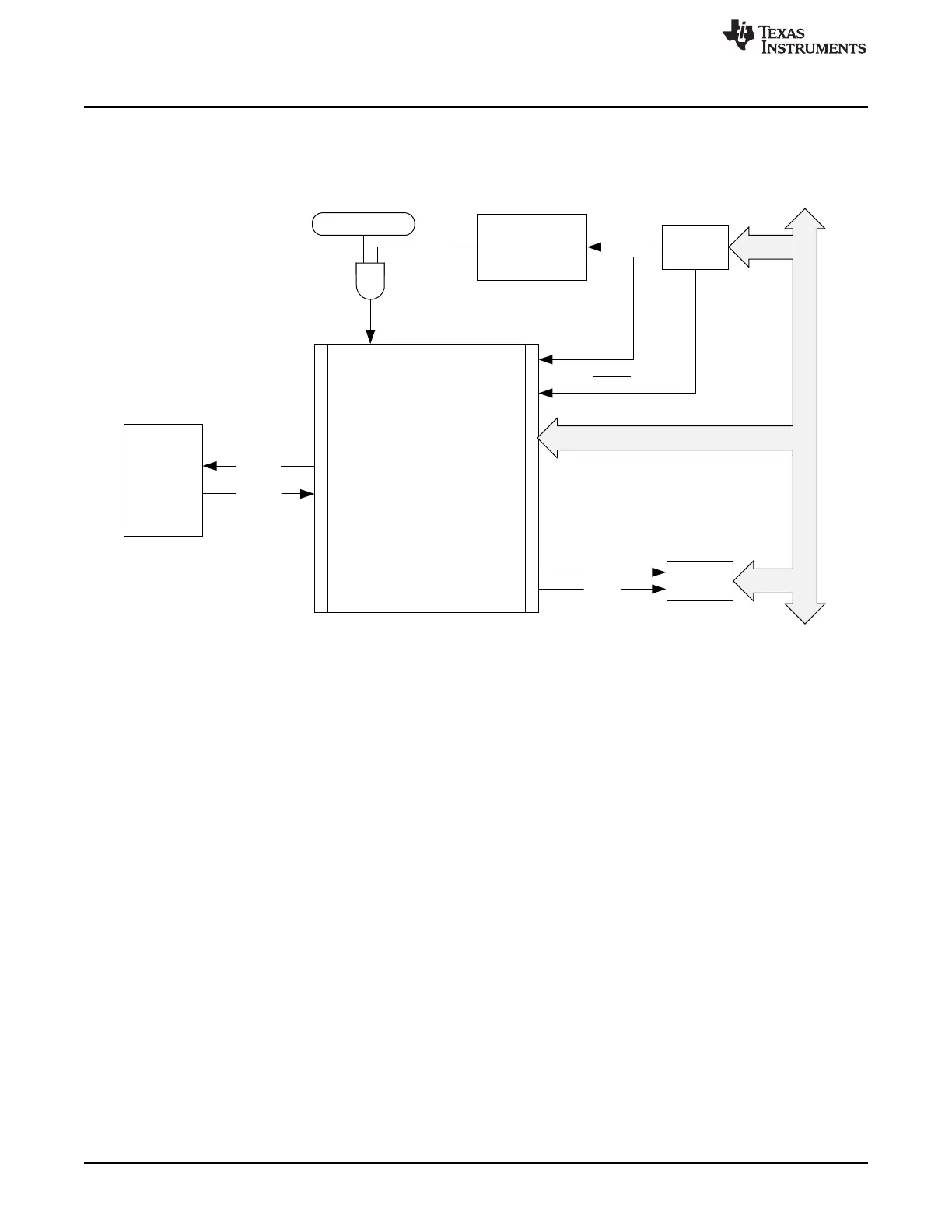

SCITXD

SCIRXD

SCI

Low Speed

Prescaler

PIE

LSPCLK SYSCLK

SYSRS

RXINT

TXINT

Peripheral Bus

CPU

PCLKCR7

GPIO

MUX

Bit

Clock

Introduction

www.ti.com

582

SPRUI07–March 2020

Submit Documentation Feedback

Copyright © 2020, Texas Instruments Incorporated

Serial Communications Interface (SCI)

10.1 Introduction

The SCI interfaces are shown in Figure 10-1.

Figure 10-1. SCI CPU Interface

Features of the SCI module include:

• Two external pins:

– SCITXD: SCI transmit-output pin

– SCIRXD: SCI receive-input pin

Both pins can be used as GPIO if not used for SCI.

• Baud rate programmable to 64K different rates

• Data-word format

– One start bit

– Data-word length programmable from one to eight bits

– Optional even/odd/no parity bit

– One or two stop bits

– An extra bit to distinguish addresses from data (address bit mode only)

• Four error-detection flags: parity, overrun, framing, and break detection

• Two wake-up multiprocessor modes: idle-line and address bit

• Half- or full-duplex operation

• Double-buffered receive and transmit functions

• Transmitter and receiver operations can be accomplished through interrupt-driven or polled algorithms

with status flags.

• Separate enable bits for transmitter and receiver interrupts (except BRKDT)

• NRZ (non-return-to-zero) format

Loading...

Loading...