Flash and OTP Memory Blocks

www.ti.com

46

SPRUI07–March 2020

Submit Documentation Feedback

Copyright © 2020, Texas Instruments Incorporated

System Control and Interrupts

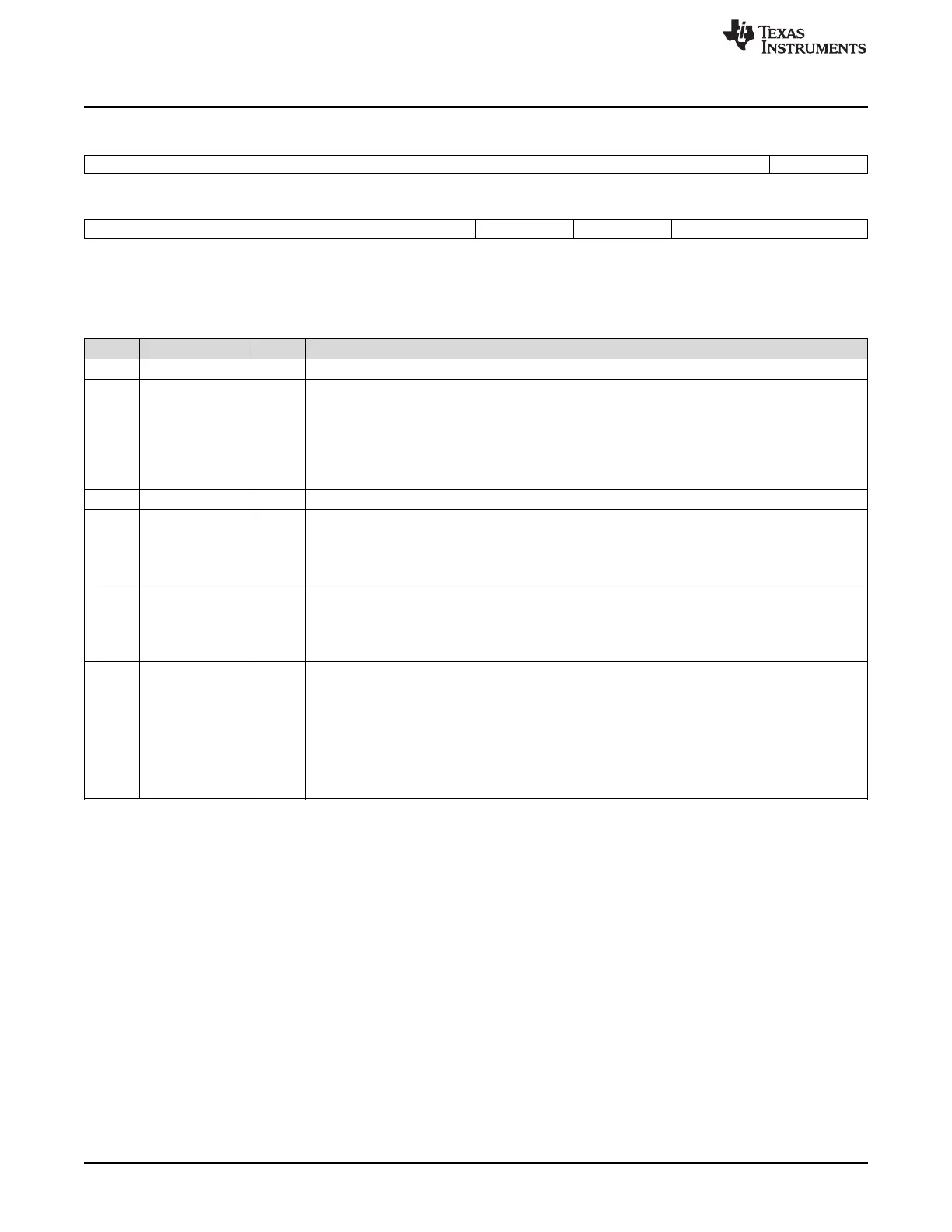

Figure 1-6. Flash Status Register (FSTATUS)

15 9 8

Reserved 3VSTAT

R-0 R/W1C-0

7 4 3 2 1 0

Reserved ACTIVEWAITS STDBYWAITS PWRS

R-0 R-0 R-0 R-0

LEGEND: R/W = Read/Write; R = Read only; W1C = Write 1 to clear; -n = value after reset

(1)

This register is EALLOW protected. See Section 1.5.2 for more information.

(2)

This register is protected by the Code Security Module (CSM). See Section 1.2 for more information.

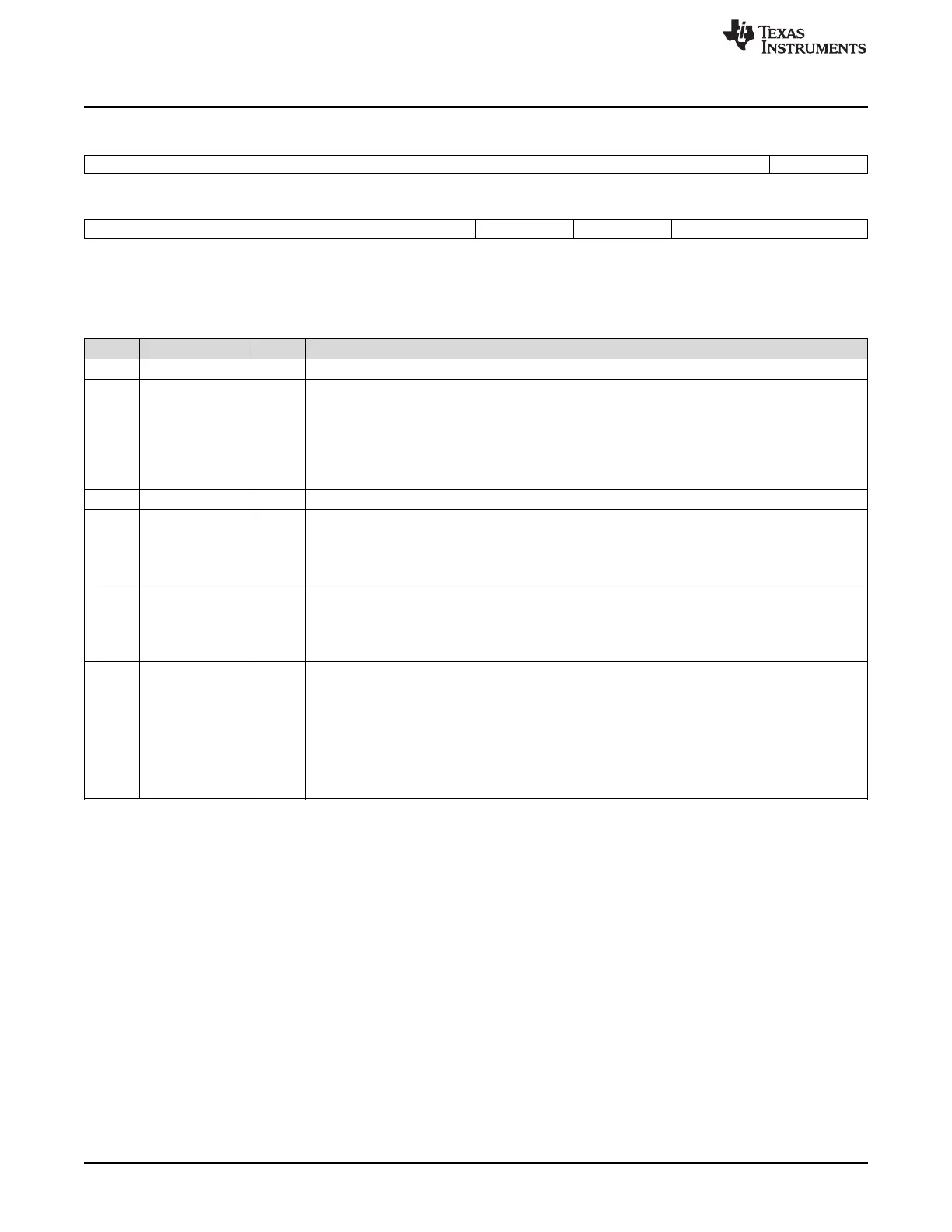

Table 1-4. Flash Status Register (FSTATUS) Field Descriptions

Bit Field Value Description

(1) (2)

15-9 Reserved Reserved

8 3VSTAT Flash Voltage (V

DD3VFL

) Status Latch Bit. When set, this bit indicates that the 3VSTAT signal from

the pump module went to a high level. This signal indicates that the flash 3.3-V supply went out of

the allowable range.

0 Writes of 0 are ignored.

1 When this bit reads 1, it indicates that the flash 3.3-V supply went out of the allowable range.

Clear this bit by writing a 1.

7-4 Reserved Reserved

3 ACTIVEWAITS Bank and Pump Standby To Active Wait Counter Status Bit. This bit indicates whether the

respective wait counter is timing out an access.

0 The counter is not counting.

1 The counter is counting.

2 STDBYWAITS Bank and Pump Sleep To Standby Wait Counter Status Bit. This bit indicates whether the

respective wait counter is timing out an access.

0 The counter is not counting.

1 The counter is counting.

1-0 PWRS Power Modes Status Bits. These bits indicate which power mode the flash/OTP is currently in.

The PWRS bits are set to the new power mode only after the appropriate timing delays have

expired.

00 Pump and bank in sleep mode (lowest power)

01 Pump and bank in standby mode

10 Reserved

11 Pump and bank active and in read mode (highest power)

Loading...

Loading...