SPI Registers

www.ti.com

568

SPRUI07–March 2020

Submit Documentation Feedback

Copyright © 2020, Texas Instruments Incorporated

Serial Peripheral Interface (SPI)

9.5.2.3 SPISTS Register (Offset = 2h) [reset = 0h]

SPISTS is shown in Figure 9-10 and described in Table 9-9.

Return to the Summary Table.

SPISTS contrains interrupt and status bits.

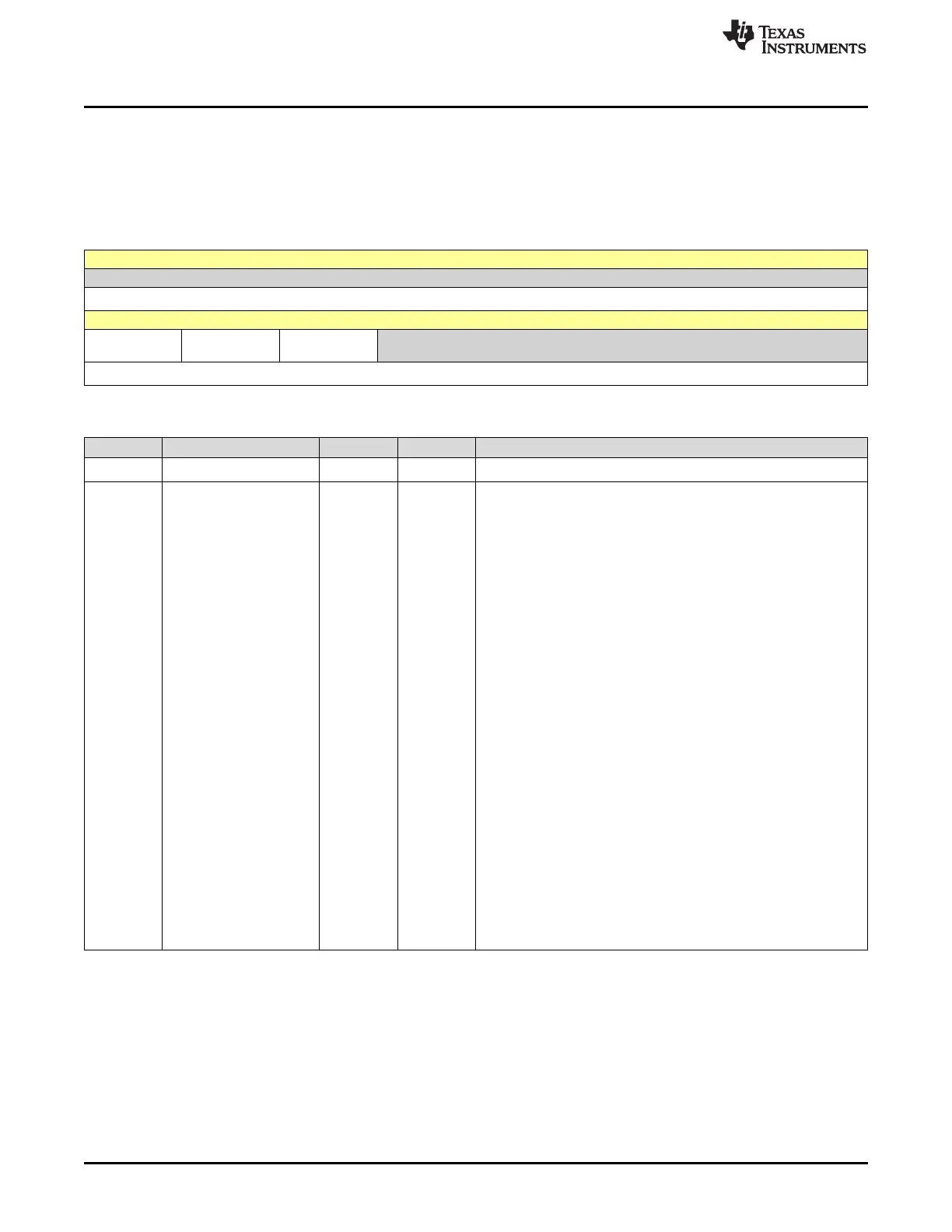

Figure 9-10. SPISTS Register

15 14 13 12 11 10 9 8

RESERVED

R-0h

7 6 5 4 3 2 1 0

OVERRUN_FL

AG

INT_FLAG BUFFULL_FLA

G

RESERVED

W1C-0h RC-0h R-0h R-0h

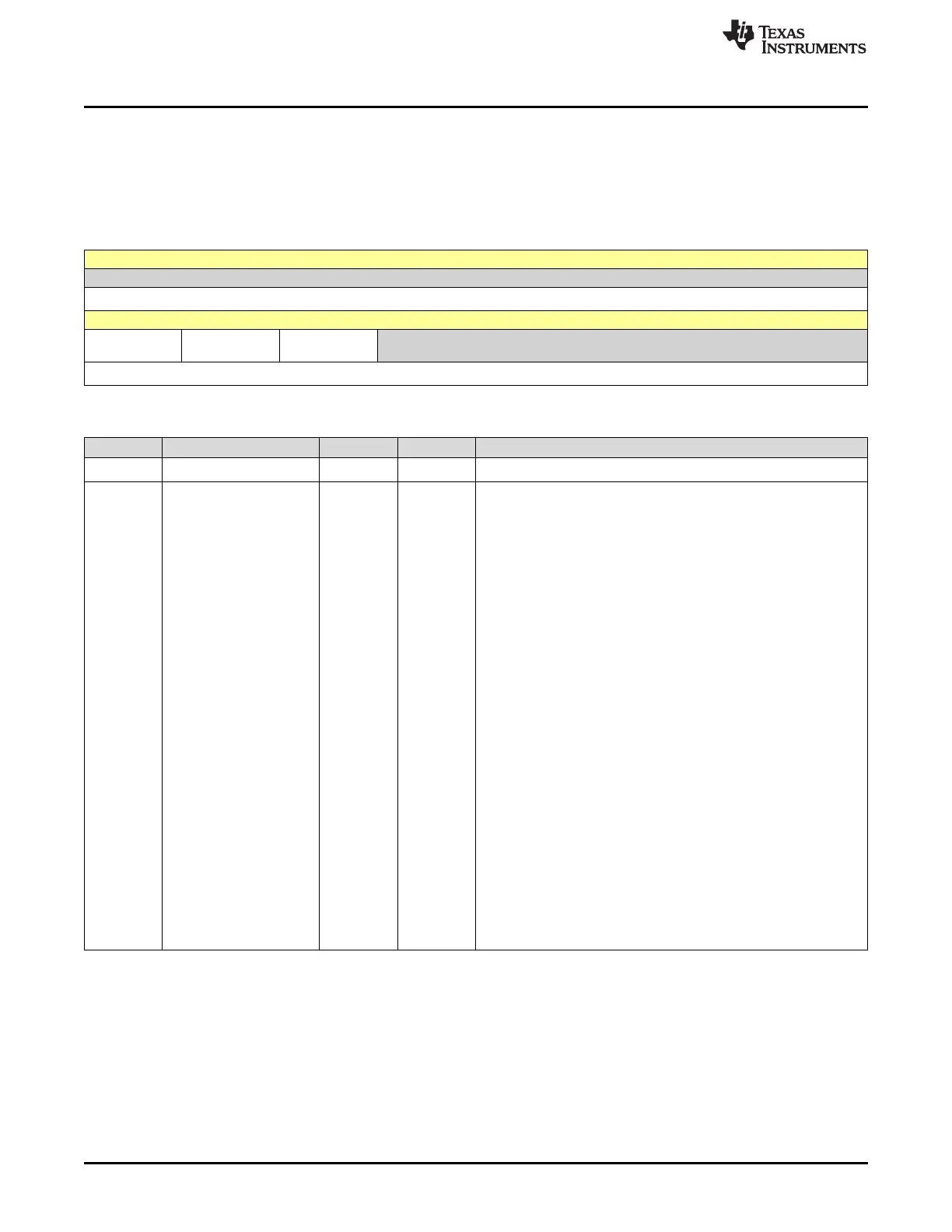

Table 9-9. SPISTS Register Field Descriptions

Bit Field Type Reset Description

15-8 RESERVED R 0h

Reserved

7 OVERRUN_FLAG W1C 0h

SPI Receiver Overrun Flag

This bit is a read/clear-only flag. The SPI hardware sets this bit when

a receive or transmit operation completes before the previous

character has been read from the buffer. The bit is cleared in one of

three ways:

- Writing a 1 to this bit

- Writing a 0 to SPI SW RESET (SPICCR.7)

- Resetting the system

If the OVERRUN INT ENA bit (SPICTL.4) is set, the SPI requests

only one interrupt upon the first occurrence of setting the RECEIVER

OVERRUN Flag bit. Subsequent overruns will not request additional

interrupts if this flag bit is already set. This means that in order to

allow new overrun interrupt requests the user must clear this flag bit

by writing a 1 to SPISTS.7 each time an overrun condition occurs. In

other words, if the RECEIVER OVERRUN Flag bit is left set (not

cleared) by the interrupt service routine, another overrun interrupt

will not be immediately re-entered when the interrupt service routine

is exited.

Reset type: SYSRSn

0h (R/W) = A receive overrun condition has not occurred.

1h (R/W) = The last received character has been overwritten and

therefore lost (when the SPIRXBUF was overwritten by the SPI

module before the previous character was read by the user

application).

Writing a '1' will clear this bit. The RECEIVER OVERRUN Flag bit

should be cleared during the interrupt service routine because the

RECEIVER OVERRUN Flag bit and SPI INT FLAG bit (SPISTS.6)

share the same interrupt vector. This will alleviate any possible

doubt as to the source of the interrupt when the next byte is

received.

Loading...

Loading...