www.ti.com

SPI Registers

567

SPRUI07–March 2020

Submit Documentation Feedback

Copyright © 2020, Texas Instruments Incorporated

Serial Peripheral Interface (SPI)

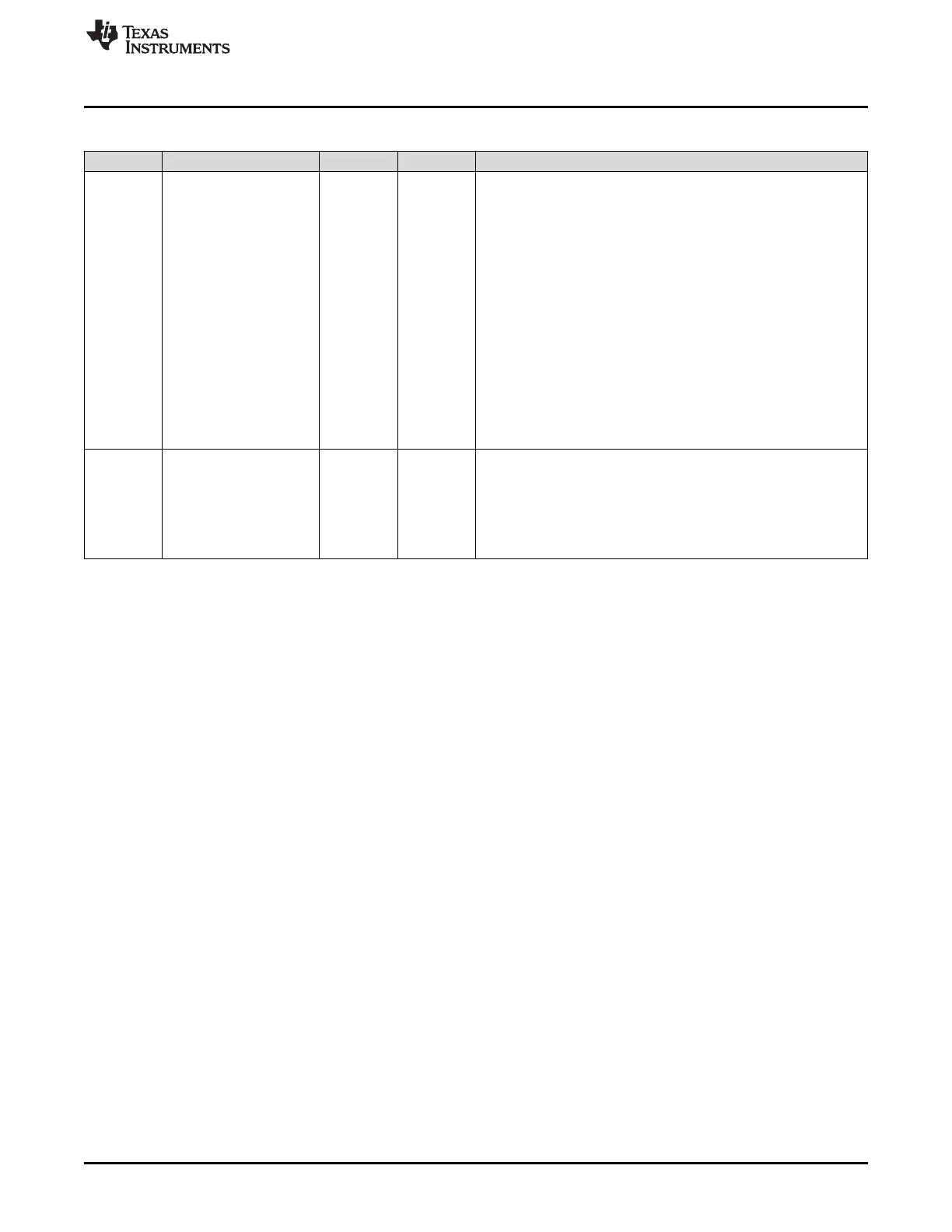

Table 9-8. SPICTL Register Field Descriptions (continued)

Bit Field Type Reset Description

1 TALK R/W 0h

Transmit Enable

The TALK bit can disable data transmission (master or slave) by

placing the serial data output in the high-impedance state. If this bit

is disabled during a transmission, the transmit shift register

continues to operate until the previous character is shifted out. When

the TALK bit is disabled, the SPI is still able to receive characters

and update the status flags. TALK is cleared (disabled) by a system

reset.

Reset type: SYSRSn

0h (R/W) = Disables transmission:

- Slave mode operation: If not previously configured as a general-

purpose I/O pin, the SPISOMI pin will be put in the high-impedance

state.

- Master mode operation: If not previously configured as a general-

purpose I/O pin, the SPISIMO pin will be put in the high-impedance

state.

1h (R/W) = Enables transmission For the 4-pin option, ensure to

enable the receiver's SPISTEn input pin.

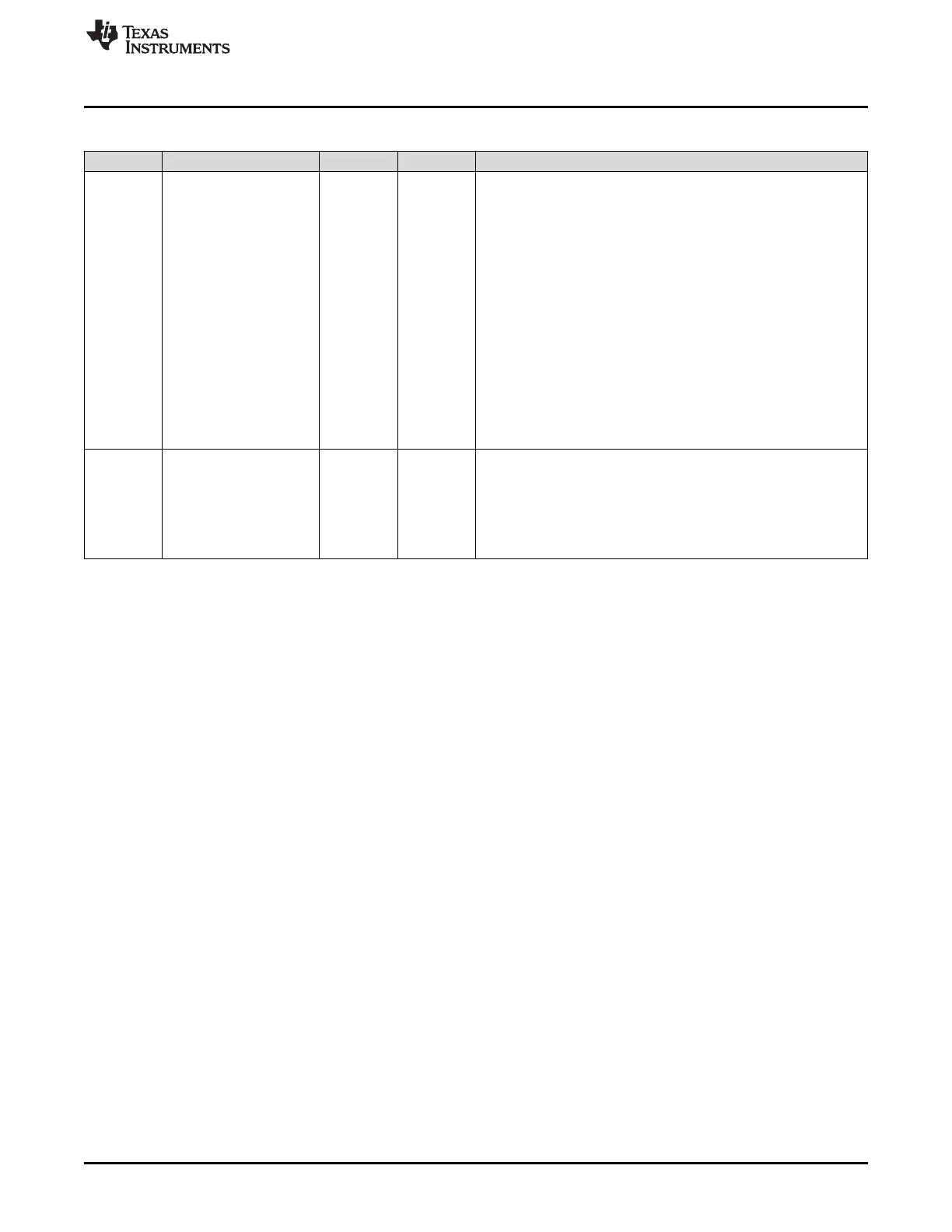

0 SPIINTENA R/W 0h

SPI Interrupt Enable

This bit controls the SPI's ability to generate a transmit/receive

interrupt. The SPI INT FLAG bit (SPISTS.6) is unaffected by this bit.

Reset type: SYSRSn

0h (R/W) = Disables the interrupt.

1h (R/W) = Enables the interrupt.

Loading...

Loading...