www.ti.com

eCAN Registers

809

SPRUI07–March 2020

Submit Documentation Feedback

Copyright © 2020, Texas Instruments Incorporated

Controller Area Network (CAN)

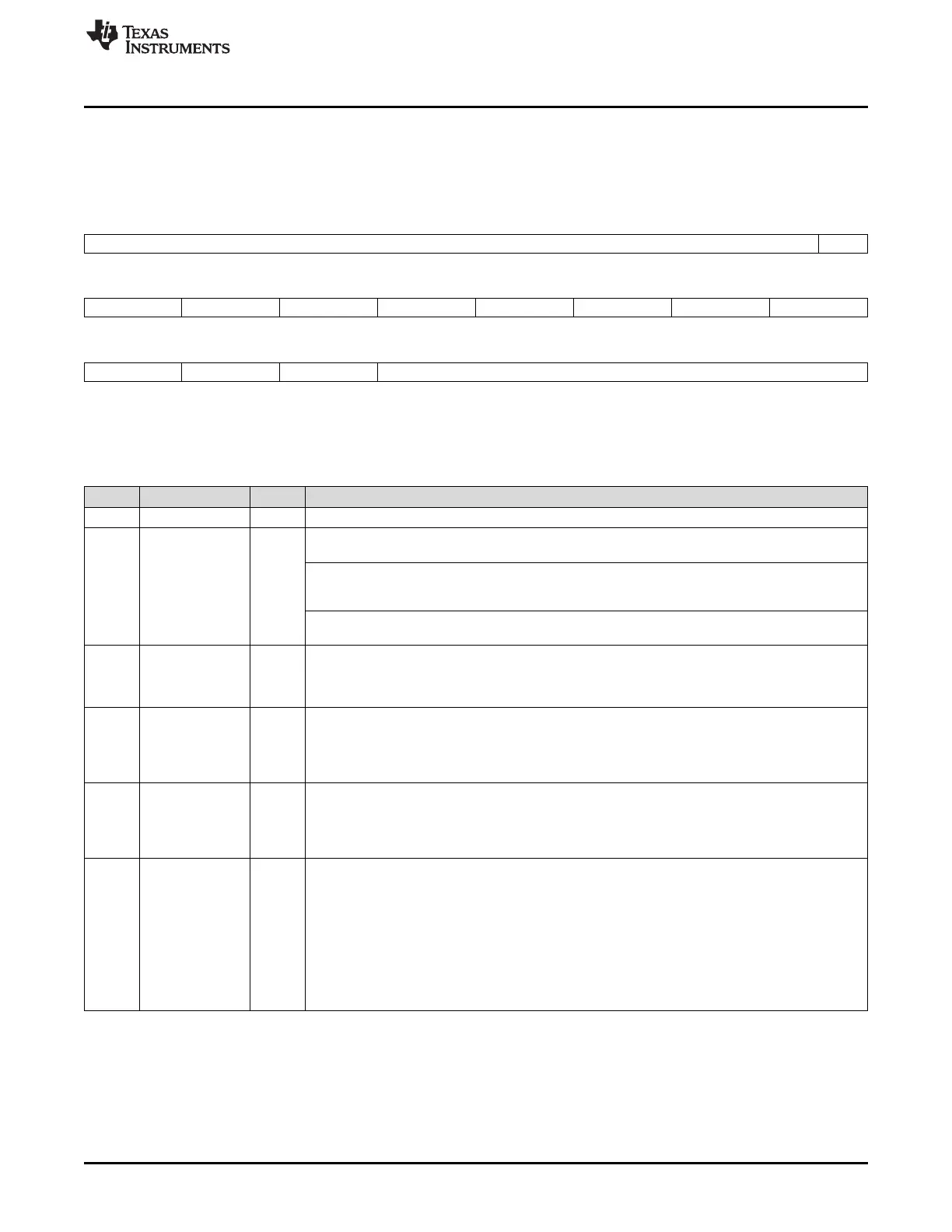

13.8.11 Master Control Register (CANMC)

This register is used to control the settings of the CAN module. Some bits of the CANMC register are

EALLOW protected. For read/write operations, only 32-bit access is supported.

Figure 13-20. Master Control Register (CANMC)

31 17 16

Reserved SUSP

R-0 R/W-0

15 14 13 12 11 10 9 8

MBCC TCC SCB CCR PDR DBO WUBA CDR

R/WP-0 SP-x R/WP-0 R/WP-1 R/WP-0 R/WP-0 R/WP-0 R/WP-0

7 6 5 4 0

ABO STM SRES MBNR

R/WP-0 R/WP-0 R/S-0 R/W-0

LEGEND: R = Read, WP = Write in EALLOW mode only, S = Set in EALLOW mode only; -n = value after reset; x = Indeterminate

Note: eCAN only, reserved in the SCC

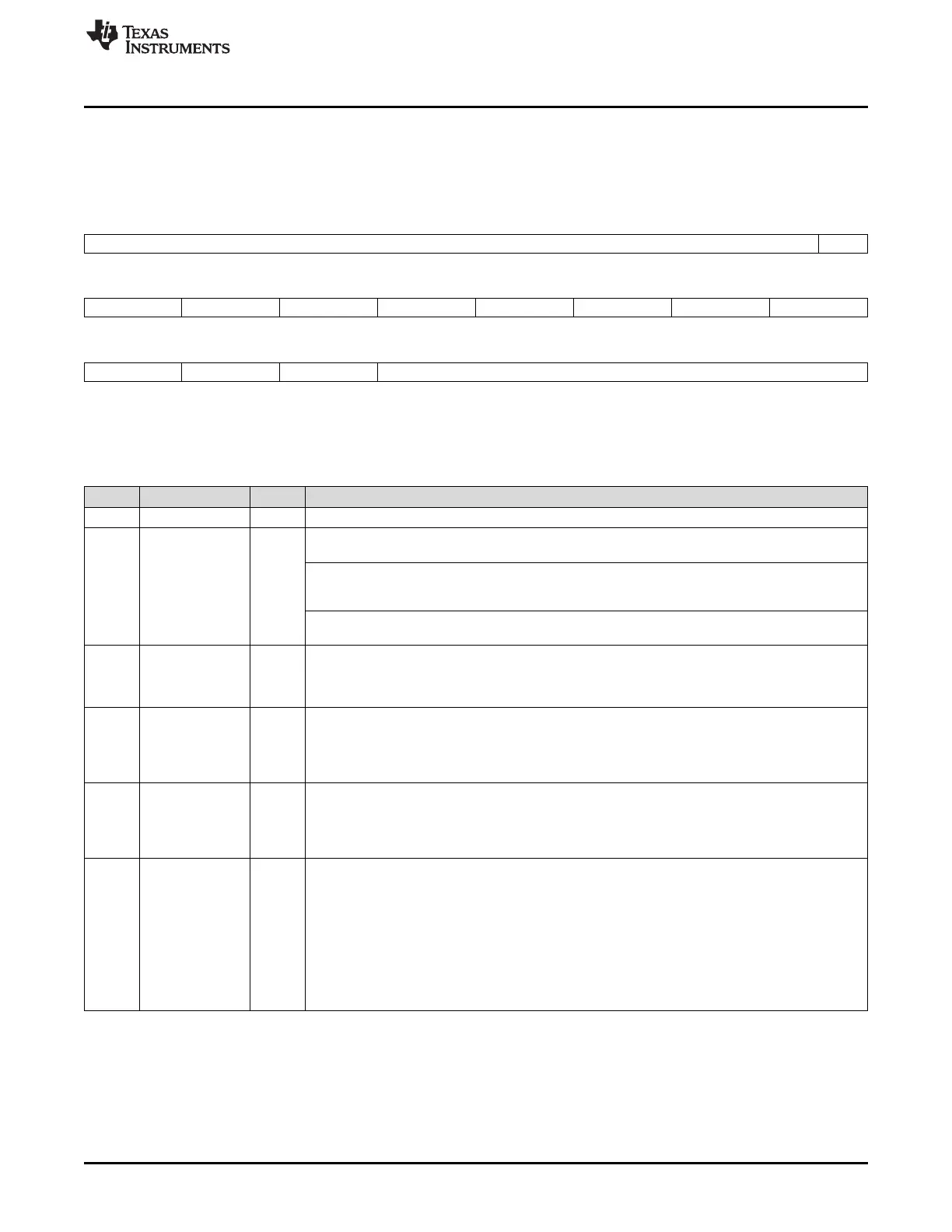

Table 13-19. Master Control Register (CANMC) Field Descriptions

Bit Field Value Description

31:17 Reserved Reads are undefined and writes have no effect.

16 SUSP SUSPEND. This bit determines the action of the CAN module in SUSPEND (emulation stop such

as breakpoint or single stepping).

1 FREE mode. The peripheral continues to run in SUSPEND. The node would participate in CAN

communication normally (sending acknowledge, generating error frames, transmitting/receiving

data) while in SUSPEND.

0 SOFT mode. The peripheral shuts down during SUSPEND after the current transmission is

complete.

15 MBCC Mailbox timestamp counter clear bit. This bit is reserved in SCC mode and it is EALLOW protected.

1 The time stamp counter is reset to 0 after a successful transmission or reception of mailbox 16.

0 The time stamp counter is not reset.

14 TCC Time stamp counter MSB clear bit. This bit is reserved in SCC mode and it is EALLOW protected.

1 The MSB of the time stamp counter is reset to 0. The TCC bit is reset after one clock cycle by the

internal logic.

0 The time stamp counter is not changed.

13 SCB SCC compatibility bit. This bit is EALLOW protected.

1 Select eCAN mode.

0 The eCAN is in SCC mode. Only mailboxes 15 to 0 can be used. Timestamping feature is not

available.

12 CCR Change-configuration request. This bit is EALLOW protected.

1 The CPU requests write access to the configuration register CANBTC and the acceptance mask

registers (CANGAM, LAM[0], and LAM[3]) of the SCC. After setting this bit, the CPU must wait until

the CCE flag of CANES register is at 1 before proceeding to configure the CANBTC register.

The CCR bit will also be set upon a bus-off condition, if the ABO bit is not set. The BO condition

can be exited by clearing this bit (after 128 * 11 consecutive recessive bits on the bus).

0 The CPU requests normal operation. This can be done only after the configuration register

CANBTC was set to the allowed values. It also exits the bus-off state after the obligatory bus-off

recovery sequence.

Loading...

Loading...