www.ti.com

I2C Registers

655

SPRUI07–March 2020

Submit Documentation Feedback

Copyright © 2020, Texas Instruments Incorporated

Inter-Integrated Circuit Module (I2C)

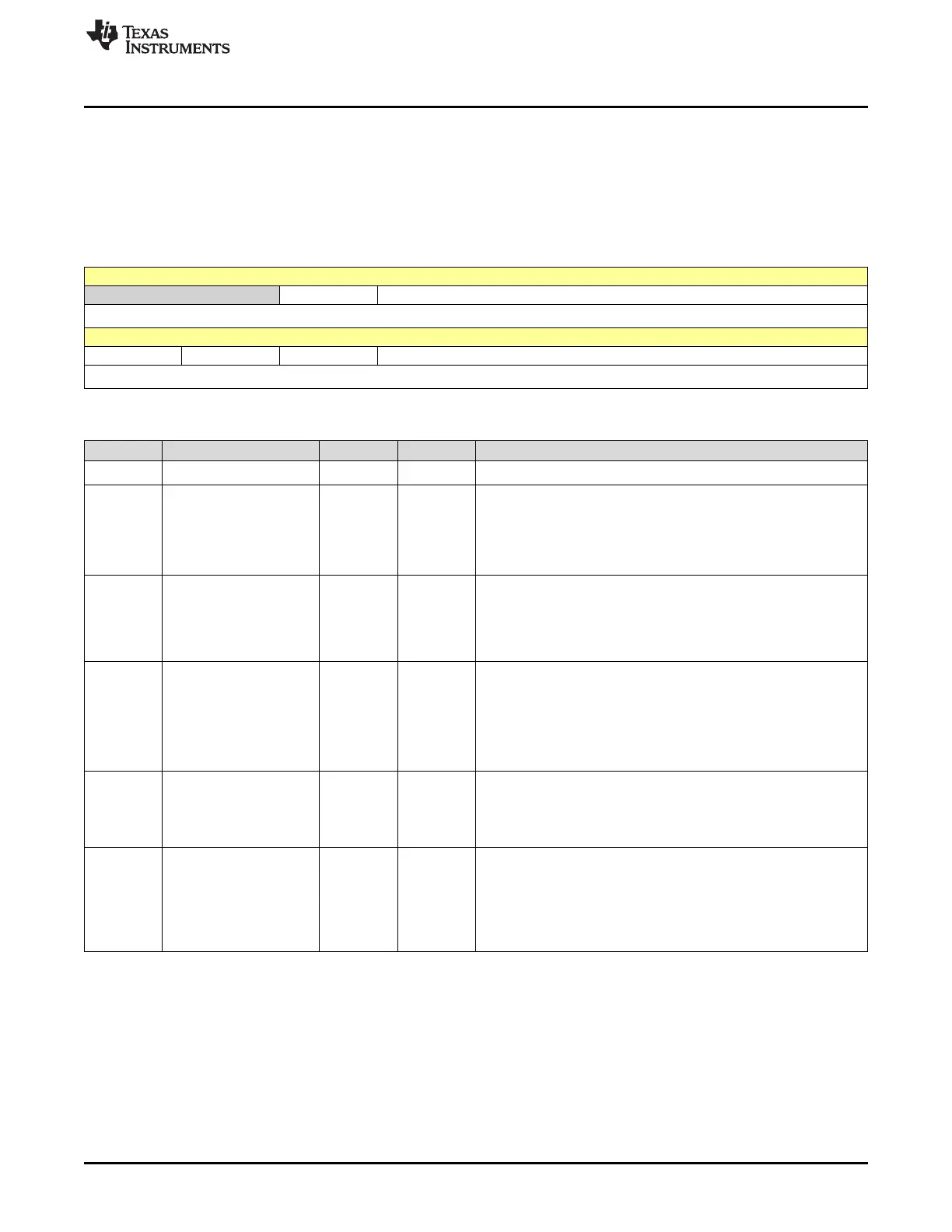

11.6.2.15 I2CFFRX Register (Offset = 21h) [reset = 0h]

I2CFFRX is shown in Figure 11-32 and described in Table 11-24.

Return to the Summary Table.

The I2C receive FIFO register (I2CFFRX) is a 16-bit register that contains the control and status bits for

the receive FIFO mode of operation on the I2C peripheral.

Figure 11-32. I2CFFRX Register

15 14 13 12 11 10 9 8

RESERVED RXFFRST RXFFST

R-0h R/W-0h R-0h

7 6 5 4 3 2 1 0

RXFFINT RXFFINTCLR RXFFIENA RXFFIL

R-0h R-0/W1S-0h R/W-0h R/W-0h

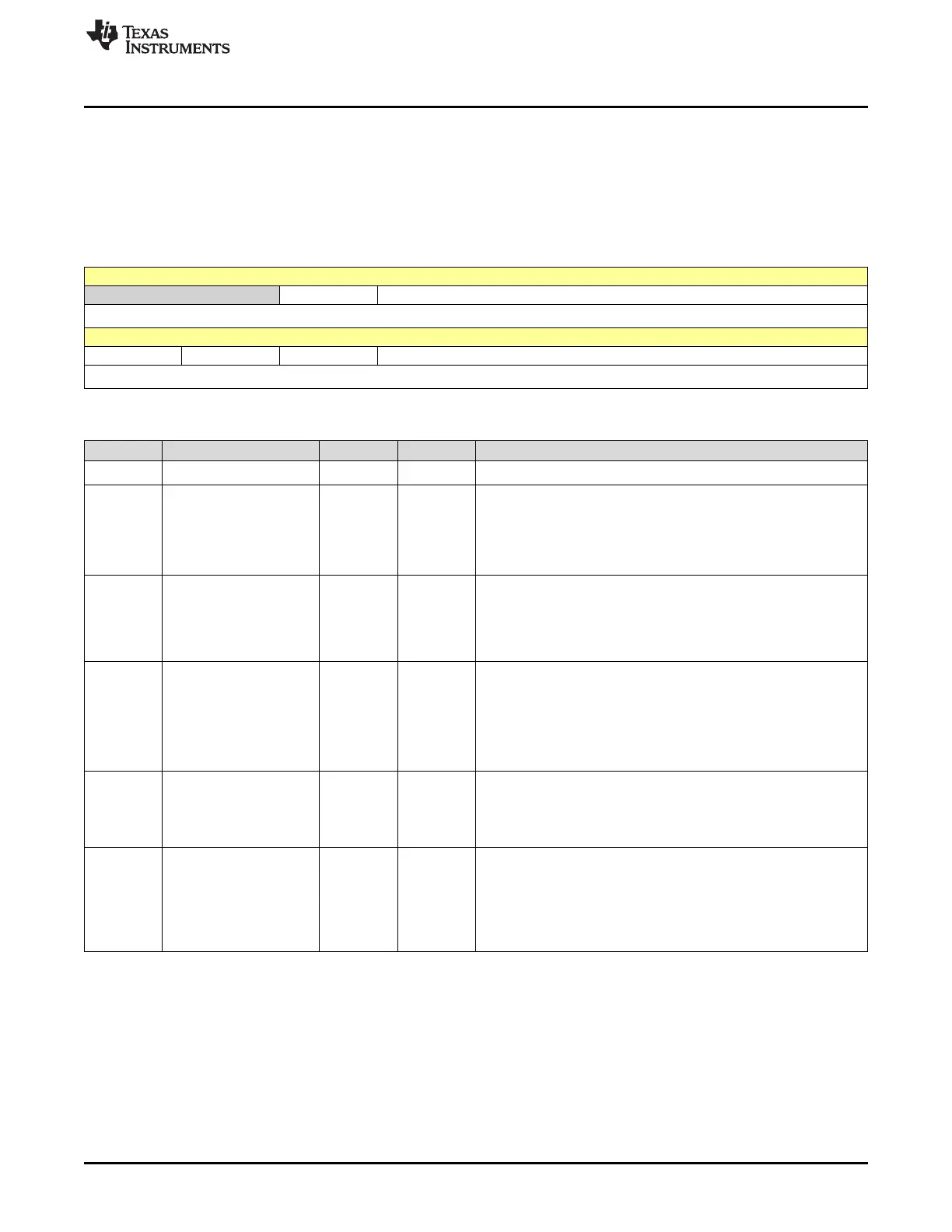

Table 11-24. I2CFFRX Register Field Descriptions

Bit Field Type Reset Description

15-14 RESERVED R 0h

Reserved

13 RXFFRST R/W 0h

I2C receive FIFO reset bit

Reset type: SYSRSn

0h (R/W) = Reset the receive FIFO pointer to 0000 and hold the

receive FIFO in the reset state.

1h (R/W) = Enable the receive FIFO operation.

12-8 RXFFST R 0h

Contains the status of the receive FIFO:

xxxxx Receive FIFO contains xxxxx bytes

00000 Receive FIFO is empty.

Reset type: SYSRSn

7 RXFFINT R 0h

Receive FIFO interrupt flag.

This bit cleared by a CPU write of a 1 to the RXFFINTCLR bit. If the

RXFFIENA bit is set, this bit will generate an interrupt when it is set

Reset type: SYSRSn

0h (R/W) = Receive FIFO interrupt condition has not occurred.

1h (R/W) = Receive FIFO interrupt condition has occurred.

6 RXFFINTCLR R-0/W1S 0h

Receive FIFO interrupt flag clear bit.

Reset type: SYSRSn

0h (R/W) = Writes of zeros have no effect. Reads return a zero.

1h (R/W) = Writing a 1 to this bit clears the RXFFINT flag.

5 RXFFIENA R/W 0h

Receive FIFO interrupt enable bit.

Reset type: SYSRSn

0h (R/W) = Disabled. RXFFINT flag does not generate an interrupt

when set.

1h (R/W) = Enabled. RXFFINT flag does generate an interrupt

when set.

Loading...

Loading...