I2C Registers

www.ti.com

656

SPRUI07–March 2020

Submit Documentation Feedback

Copyright © 2020, Texas Instruments Incorporated

Inter-Integrated Circuit Module (I2C)

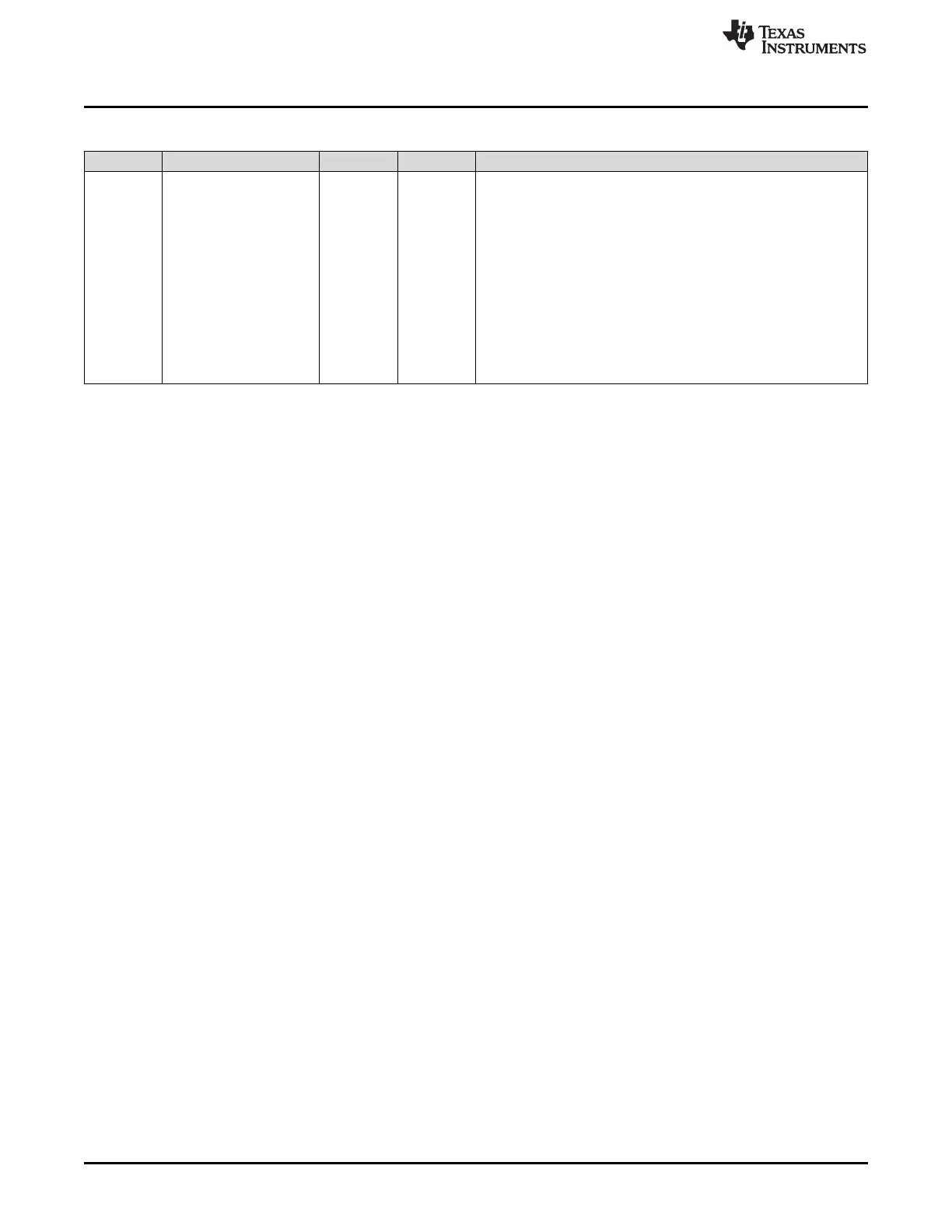

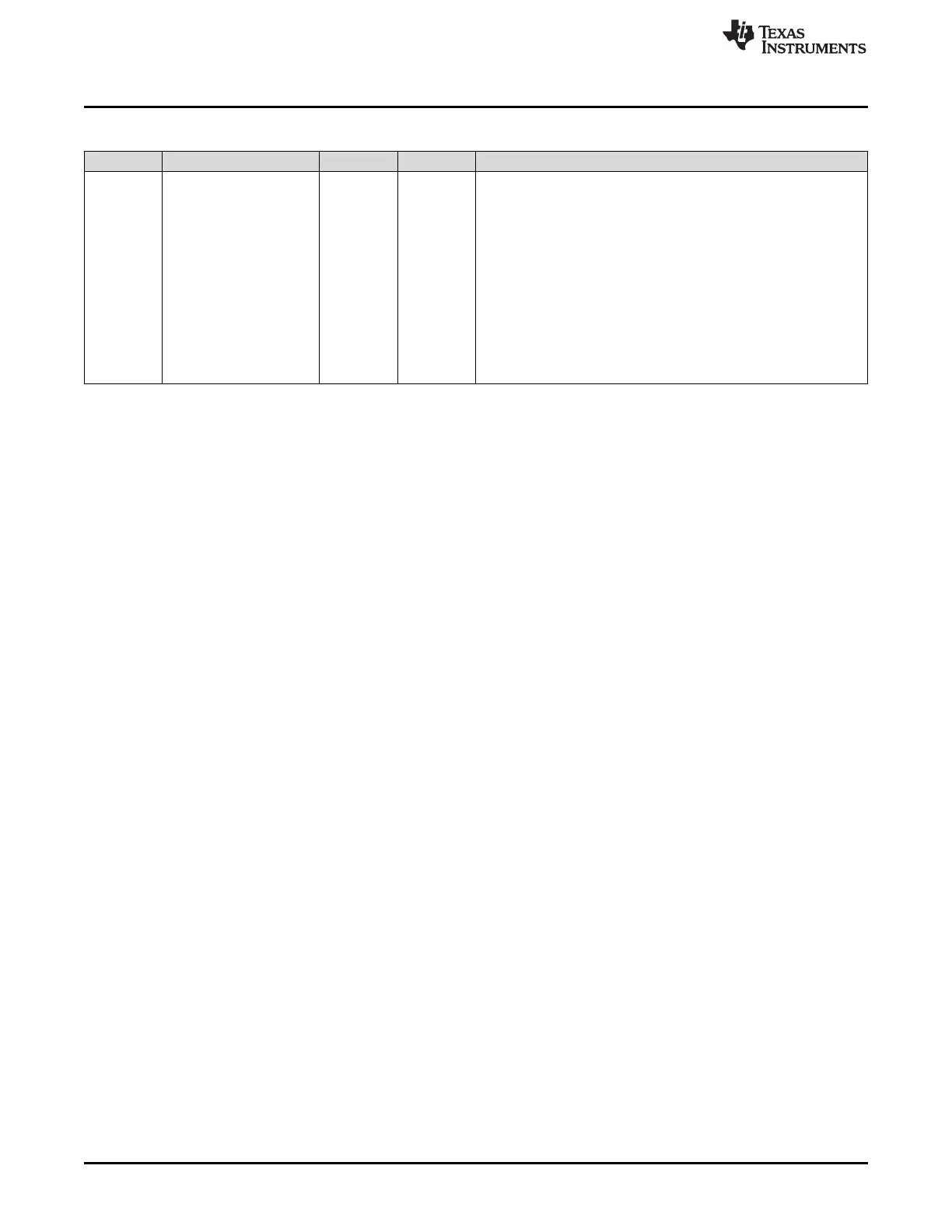

Table 11-24. I2CFFRX Register Field Descriptions (continued)

Bit Field Type Reset Description

4-0 RXFFIL R/W 0h

Receive FIFO interrupt level.

These bits set the status level that will set the receive interrupt flag.

When the RXFFST4-0 bits reach a value equal to or greater than

these bits, the RXFFINT flag is set. This will generate an interrupt if

the RXFFIENA bit is set.

Note: Since these bits are reset to zero, the receive FIFO interrupt

flag will be set if the receive FIFO operation is enabled and the I2C

is taken out of reset. This will generate a receive FIFO interrupt if

enabled. To avoid this, modify these bits on the same instruction as

or prior to setting the RXFFRST bit. Because the I2C on this device

has a 16-level receive FIFO, these bits cannot be configured for an

interrupt of more than 16 FIFO levels.

Reset type: SYSRSn

Loading...

Loading...