I2C Registers

www.ti.com

636

SPRUI07–March 2020

Submit Documentation Feedback

Copyright © 2020, Texas Instruments Incorporated

Inter-Integrated Circuit Module (I2C)

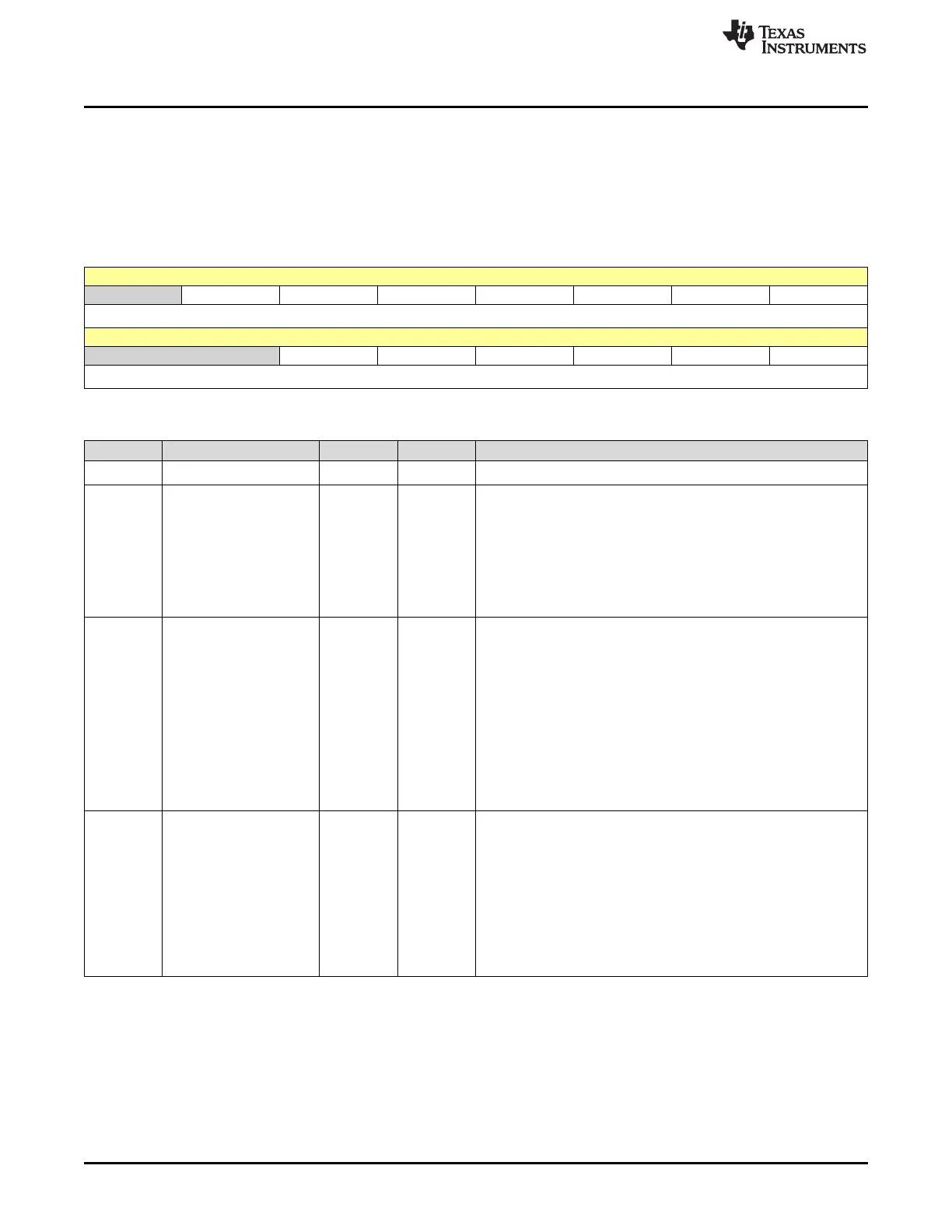

11.6.2.3 I2CSTR Register (Offset = 2h) [reset = 410h]

I2CSTR is shown in Figure 11-20 and described in Table 11-12.

Return to the Summary Table.

The I2C status register (I2CSTR) is a 16-bit register used to determine which interrupt has occurred and to

read status information.

Figure 11-20. I2CSTR Register

15 14 13 12 11 10 9 8

RESERVED SDIR NACKSNT BB RSFULL XSMT AAS AD0

R-0h R/W1C-0h R/W1C-0h R-0h R-0h R-1h R-0h R-0h

7 6 5 4 3 2 1 0

RESERVED SCD XRDY RRDY ARDY NACK ARBL

R/W-0h R/W1C-0h R-1h R/W1C-0h R/W1C-0h R/W1C-0h R/W1C-0h

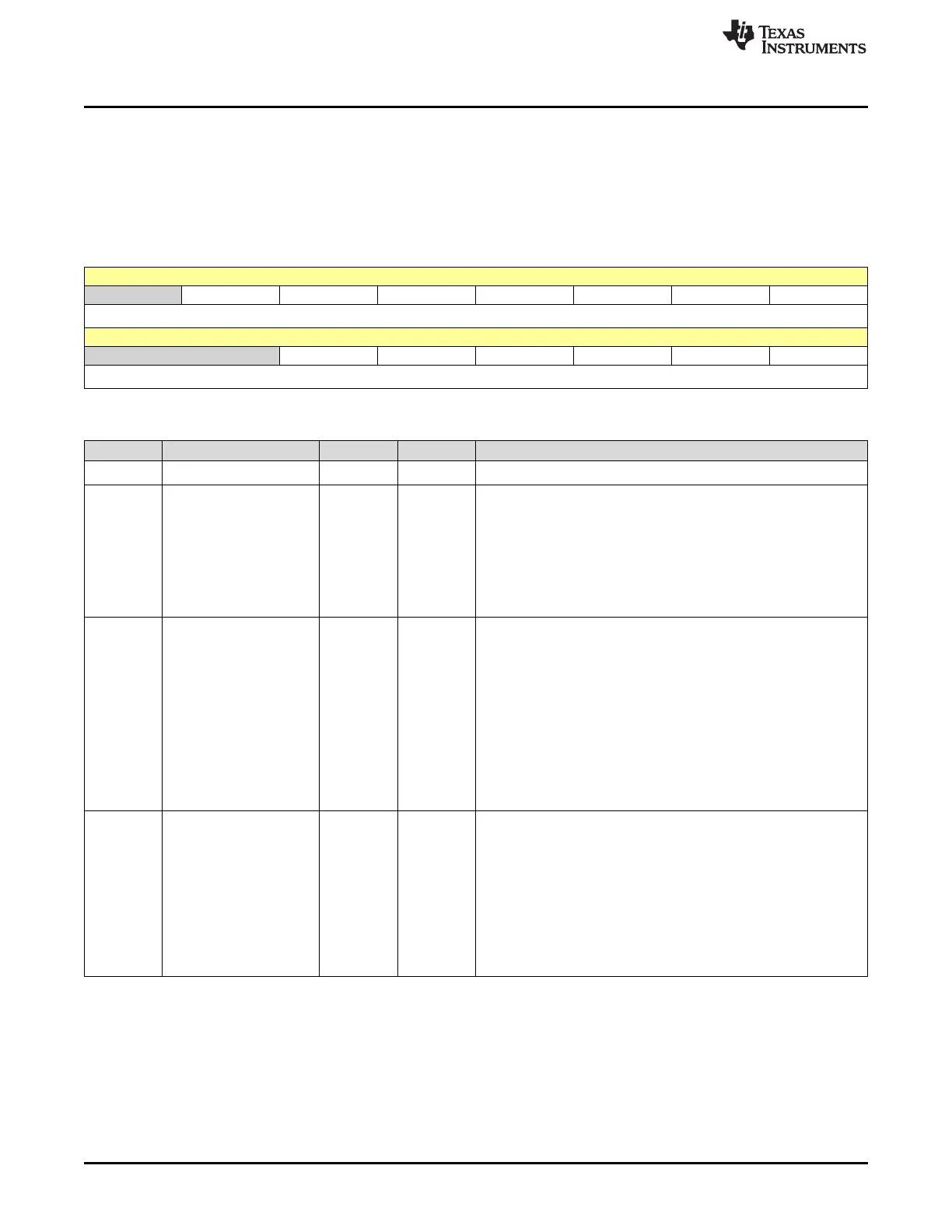

Table 11-12. I2CSTR Register Field Descriptions

Bit Field Type Reset Description

15 RESERVED R 0h

Reserved

14 SDIR R/W1C 0h

Slave direction bit

Reset type: SYSRSn

0h (R/W) = I2C is not addressed as a slave transmitter. SDIR is

cleared by one of the following events:

- It is manually cleared. To clear this bit, write a 1 to it.

- Digital loopback mode is enabled.

- A START or STOP condition occurs on the I2C bus.

1h (R/W) = I2C is addressed as a slave transmitter.

13 NACKSNT R/W1C 0h

NACK sent bit.

This bit is used when the I2C module is in the receiver mode. One

instance in which NACKSNT is affected is when the NACK mode is

used (see the description for NACKMOD in

Reset type: SYSRSn

0h (R/W) = NACK not sent. NACKSNT bit is cleared by any one of

the following events:

- It is manually cleared. To clear this bit, write a 1 to it.

- The I2C module is reset (either when 0 is written to the IRS bit of

I2CMDR or when the whole device is reset).

1h (R/W) = NACK sent: A no-acknowledge bit was sent during the

acknowledge cycle on the I2C-bus.

12 BB R 0h

Bus busy bit.

BB indicates whether the I2C-bus is busy or is free for another data

transfer. See the paragraph following the table for more information

Reset type: SYSRSn

0h (R/W) = Bus free. BB is cleared by any one of the following

events:

- The I2C module receives or transmits a STOP bit (bus free).

- The I2C module is reset.

1h (R/W) = Bus busy: The I2C module has received or transmitted

a START bit on the bus.

Loading...

Loading...