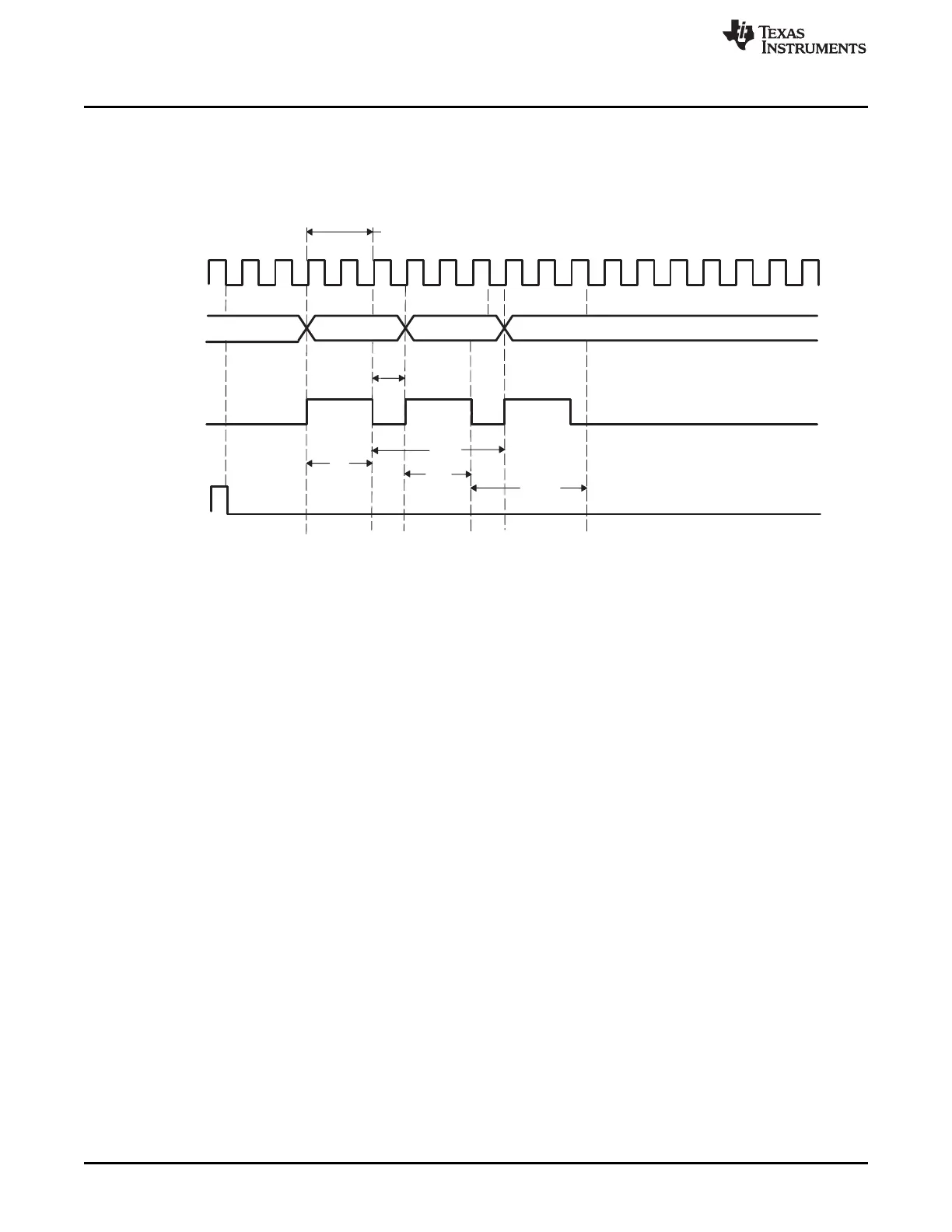

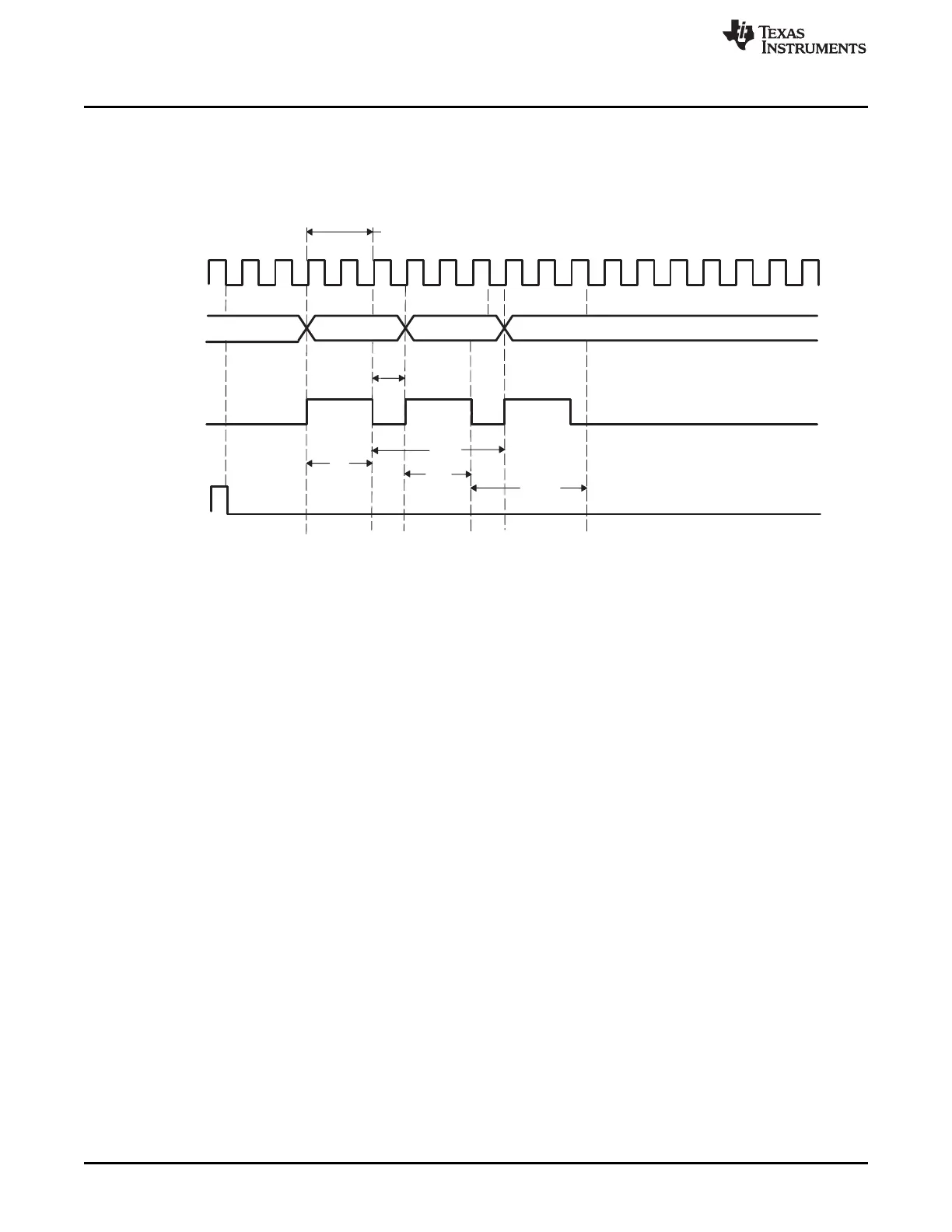

Variable−width

acquisition window

ADC

Clock

[C0NV##] [C0NV##]

(A) (A)

S

C1

ADC SOC

trigger

S

Channel

Select

SH Clock

[C0NV##+1]

(A)

C1

S

OFF

(B)

ADC Interface

www.ti.com

466

SPRUI07–March 2020

Submit Documentation Feedback

Copyright © 2020, Texas Instruments Incorporated

Analog-to-Digital Converter (ADC)

7.3.2.1 Sequential Sampling Mode

Figure 7-10 shows the timing of sequential sampling mode. In this example, the ACQ_PS bits are set to

0001b.

Figure 7-10. Sequential Sampling Mode (SMODE = 0)

A ADC channel address contained in [CONV##] 4-bit register.

B S

OFF

in sequential sampling mode is 1 ADC clock to allow for S/H circuit availability until the sampled voltage is

passed to the converter.

Legend:

C1 Time from end of acquisition window until result register update

S Acquisition window

S

OFF

Acquisition HOLD OFF

Loading...

Loading...