SCI Registers

www.ti.com

608

SPRUI07–March 2020

Submit Documentation Feedback

Copyright © 2020, Texas Instruments Incorporated

Serial Communications Interface (SCI)

10.14.2.8 SCIRXBUF Register (Offset = 7h) [reset = 0h]

SCIRXBUF is shown in Figure 10-18 and described in Table 10-14.

Return to the Summary Table.

When the current data received is shifted from RXSHF to the receiver buffer, flag bit RXRDY is set and

the data is ready to be read. If the RXBKINTENA bit (SCICTL2.1) is set, this shift also causes an interrupt.

When SCIRXBUF is read, the RXRDY flag is reset. SCIRXBUF is cleared by a system reset.

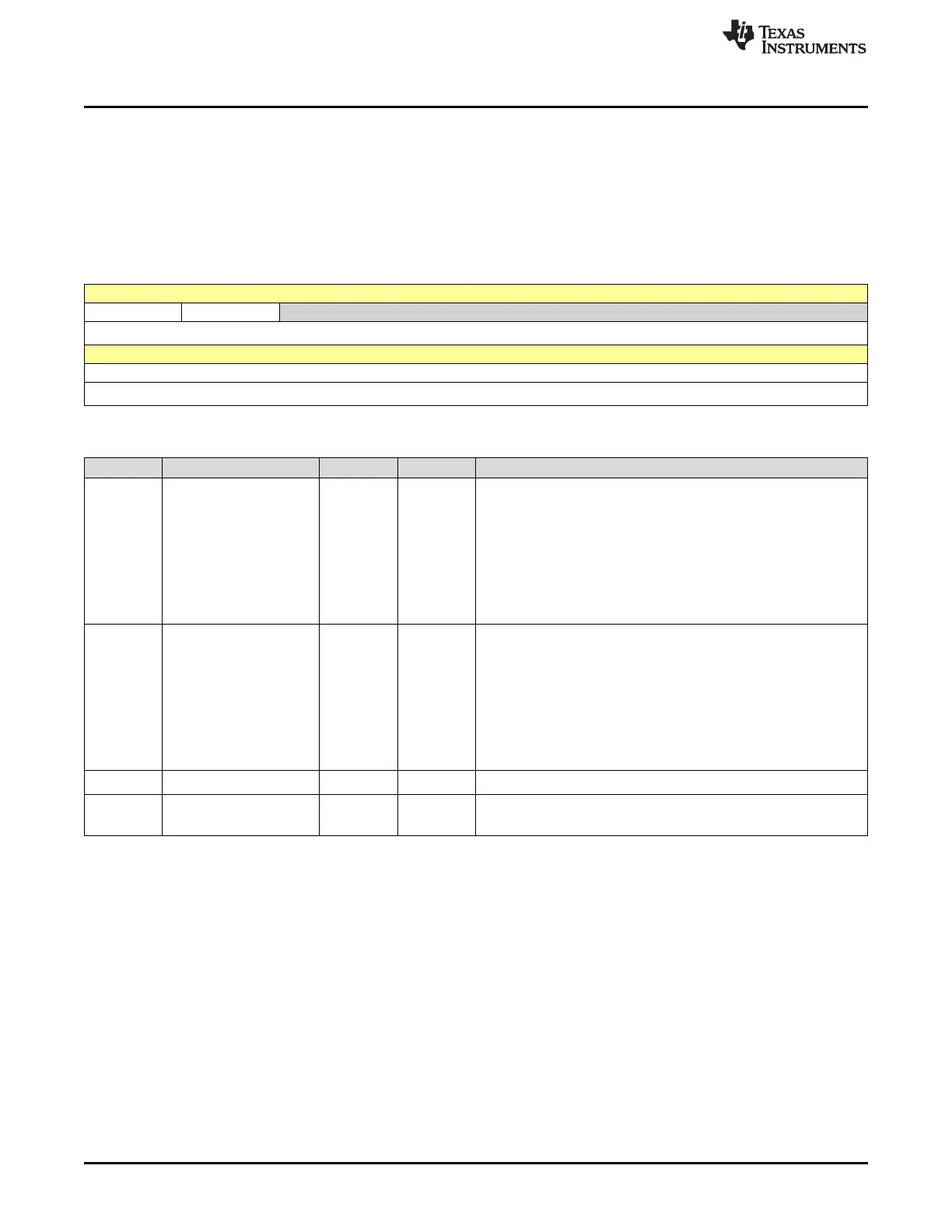

Figure 10-18. SCIRXBUF Register

15 14 13 12 11 10 9 8

SCIFFFE SCIFFPE RESERVED

R-0h R-0h R-0h

7 6 5 4 3 2 1 0

SAR

R-0h

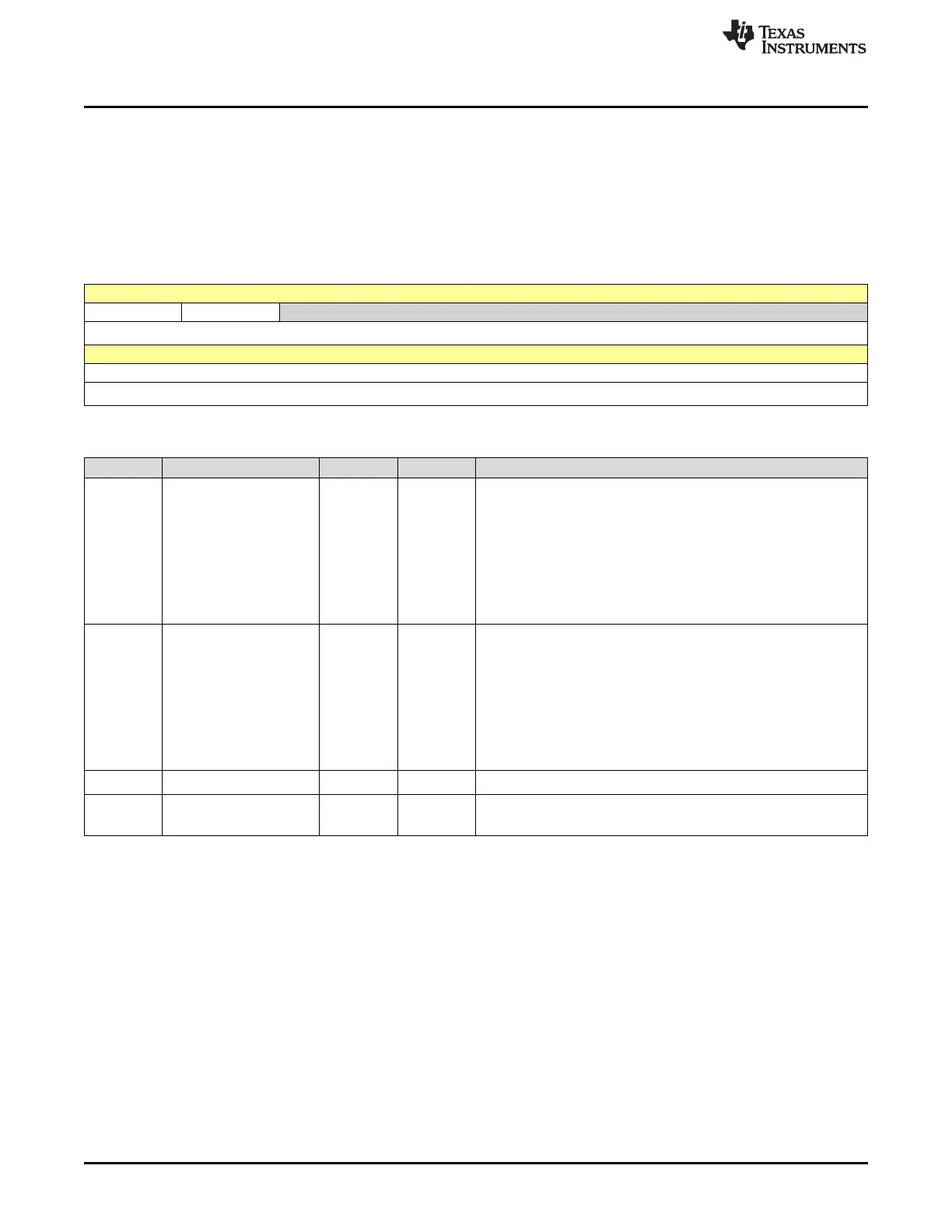

Table 10-14. SCIRXBUF Register Field Descriptions

Bit Field Type Reset Description

15 SCIFFFE R 0h

SCIFFFE. SCI FIFO Framing error flag bit (applicable only if the

FIFO is enabled)

Reset type: SYSRSn

0h (R/W) = No frame error occurred while receiving the character,

in bits 7-0. This bit is associated with the character on the top of

the FIFO.

1h (R/W) = A frame error occurred while receiving the character in

bits 7-0. This bit is associated with the character on the top of the

FIFO.

14 SCIFFPE R 0h

SCIFFPE. SCI FIFO parity error flag bit (applicable only if the FIFO

is enabled)

Reset type: SYSRSn

0h (R/W) = No parity error occurred while receiving the character,

in bits 7-0. This bit is associated with the character on the top of

the FIFO.

1h (R/W) = A parity error occurred while receiving the character in

bits 7-0. This bit is associated with the character on the top of the

FIFO.

13-8 RESERVED R 0h

Reserved

7-0 SAR R 0h

Receive Character bits

Reset type: SYSRSn

Loading...

Loading...