www.ti.com

SPI Registers

577

SPRUI07–March 2020

Submit Documentation Feedback

Copyright © 2020, Texas Instruments Incorporated

Serial Peripheral Interface (SPI)

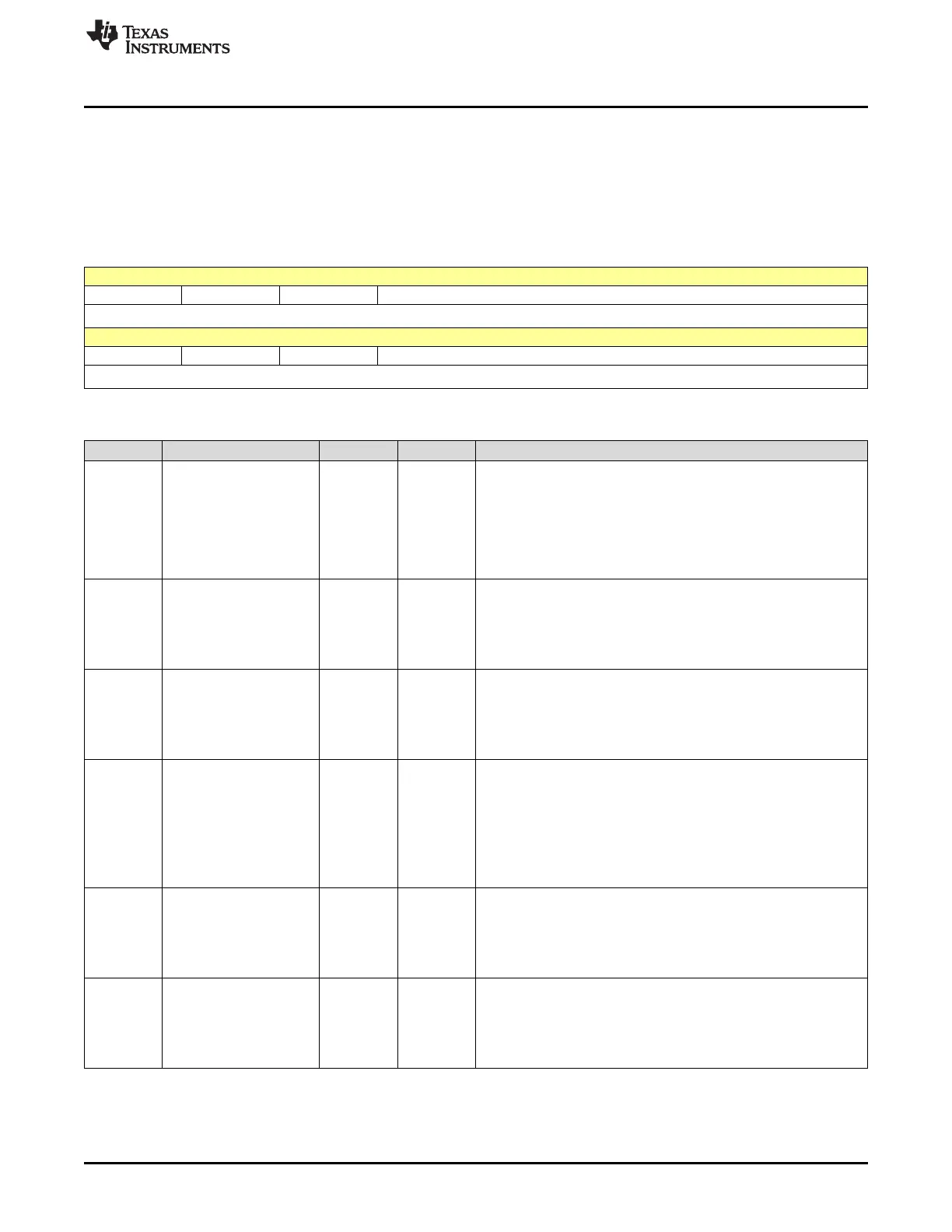

9.5.2.10 SPIFFRX Register (Offset = Bh) [reset = 201Fh]

SPIFFRX is shown in Figure 9-17 and described in Table 9-16.

Return to the Summary Table.

SPIFFRX contains both control and status bits related to the input FIFO buffer. This includes FIFO reset

control, FIFO interrupt level control, FIFO level status, as well as FIFO interrupt enable and clear bits.

Figure 9-17. SPIFFRX Register

15 14 13 12 11 10 9 8

RXFFOVF RXFFOVFCLR RXFIFORESET RXFFST

R-0h W-0h R/W-1h R-0h

7 6 5 4 3 2 1 0

RXFFINT RXFFINTCLR RXFFIENA RXFFIL

R-0h W-0h R/W-0h R/W-1Fh

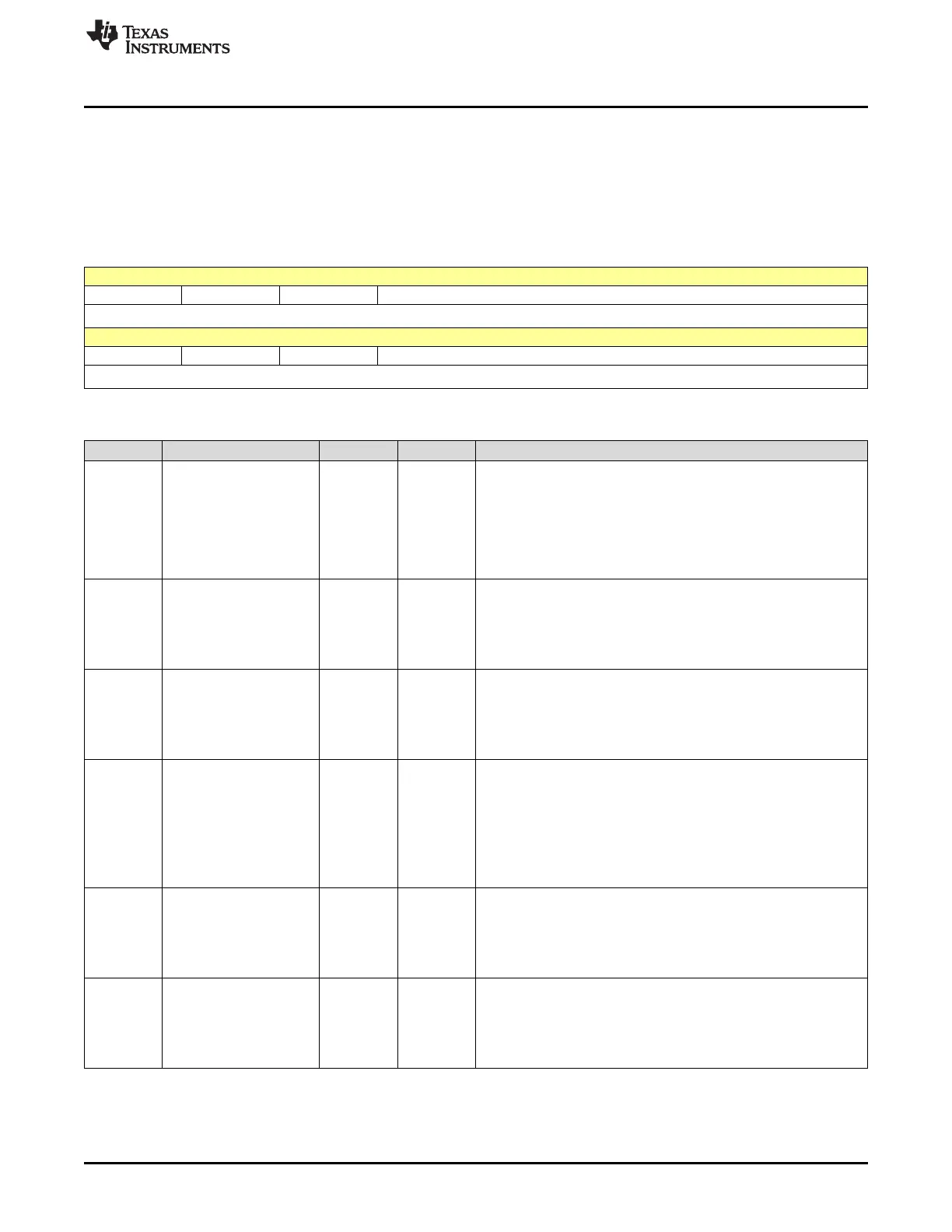

Table 9-16. SPIFFRX Register Field Descriptions

Bit Field Type Reset Description

15 RXFFOVF R 0h

Receive FIFO Overflow Flag

Reset type: SYSRSn

0h (R/W) = Receive FIFO has not overflowed. This is a read-only

bit.

1h (R/W) = Receive FIFO has overflowed, read-only bit. More than

16 words have been received in to the FIFO, and the first received

word is lost.

14 RXFFOVFCLR W 0h

Receive FIFO Overflow Clear

Reset type: SYSRSn

0h (R/W) = Write 0 does not affect RXFFOVF flag bit, Bit reads

back a zero.

1h (R/W) = Write 1 to clear SPIFFRX[RXFFOVF].

13 RXFIFORESET R/W 1h

Receive FIFO Reset

Reset type: SYSRSn

0h (R/W) = Write 0 to reset the FIFO pointer to zero, and hold in

reset.

1h (R/W) = Re-enable receive FIFO operation.

12-8 RXFFST R 0h

Receive FIFO Status

Reset type: SYSRSn

0h (R/W) = Receive FIFO is empty.

1h (R/W) = Receive FIFO has 1 word.

2h (R/W) = Receive FIFO has 2 words.

10h (R/W) = Receive FIFO has 16 words, which is the maximum.

1Fh (R/W) = Reserved.

7 RXFFINT R 0h

Receive FIFO Interrupt Flag

Reset type: SYSRSn

0h (R/W) = RXFIFO interrupt has not occurred. This is a read-only

bit.

1h (R/W) = RXFIFO interrupt has occurred. This is a read-only bit.

6 RXFFINTCLR W 0h

Receive FIFO Interrupt Clear

Reset type: SYSRSn

0h (R/W) = Write 0 has no effect on RXFIFINT flag bit, Bit reads

back a zero.

1h (R/W) = Write 1 to clear SPIFFRX[RXFFINT] flag

Loading...

Loading...