SPI Registers

www.ti.com

578

SPRUI07–March 2020

Submit Documentation Feedback

Copyright © 2020, Texas Instruments Incorporated

Serial Peripheral Interface (SPI)

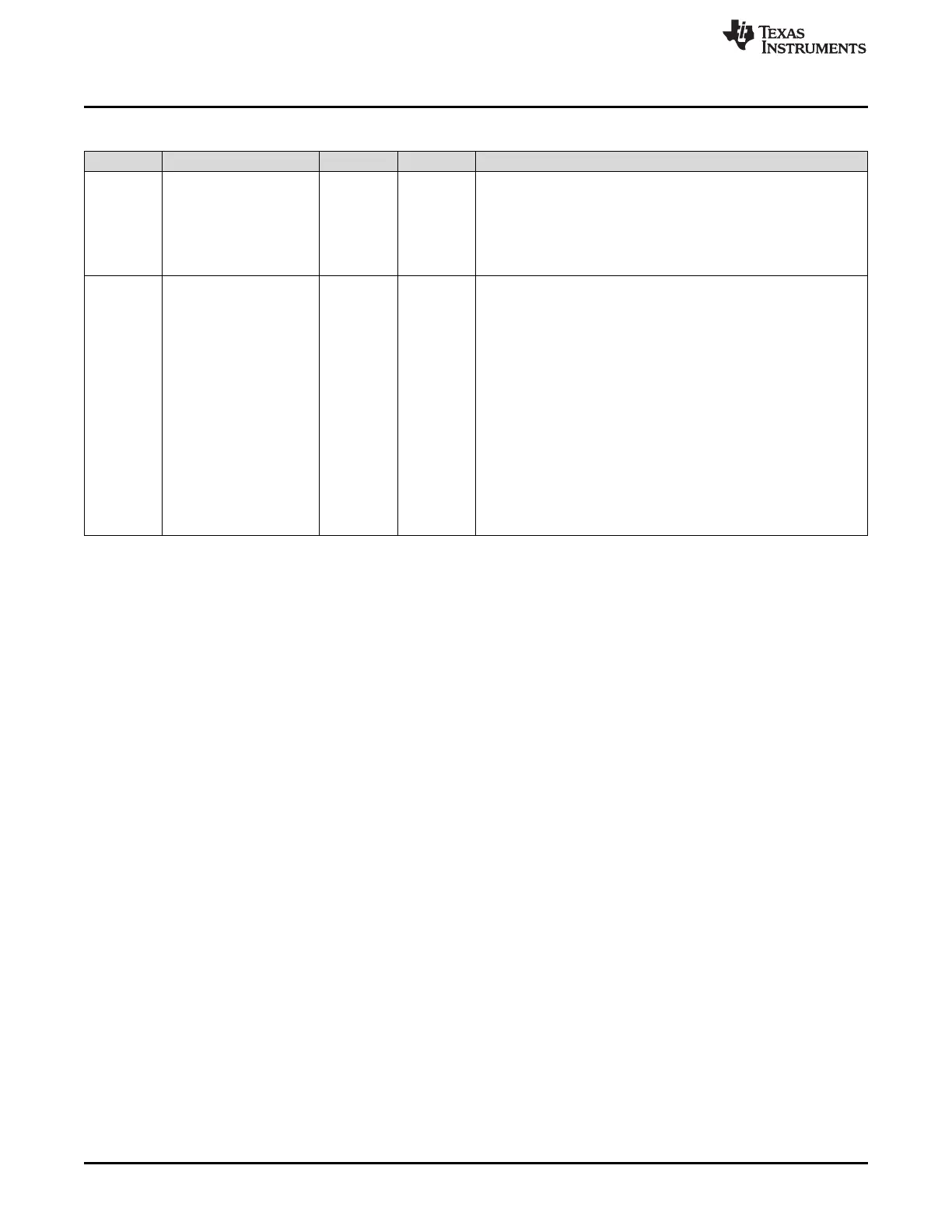

Table 9-16. SPIFFRX Register Field Descriptions (continued)

Bit Field Type Reset Description

5 RXFFIENA R/W 0h

RX FIFO Interrupt Enable

Reset type: SYSRSn

0h (R/W) = RX FIFO interrupt based on RXFFIL match (greater

than or equal to) will be disabled.

1h (R/W) = RX FIFO interrupt based on RXFFIL match (greater

than or equal to) will be enabled.

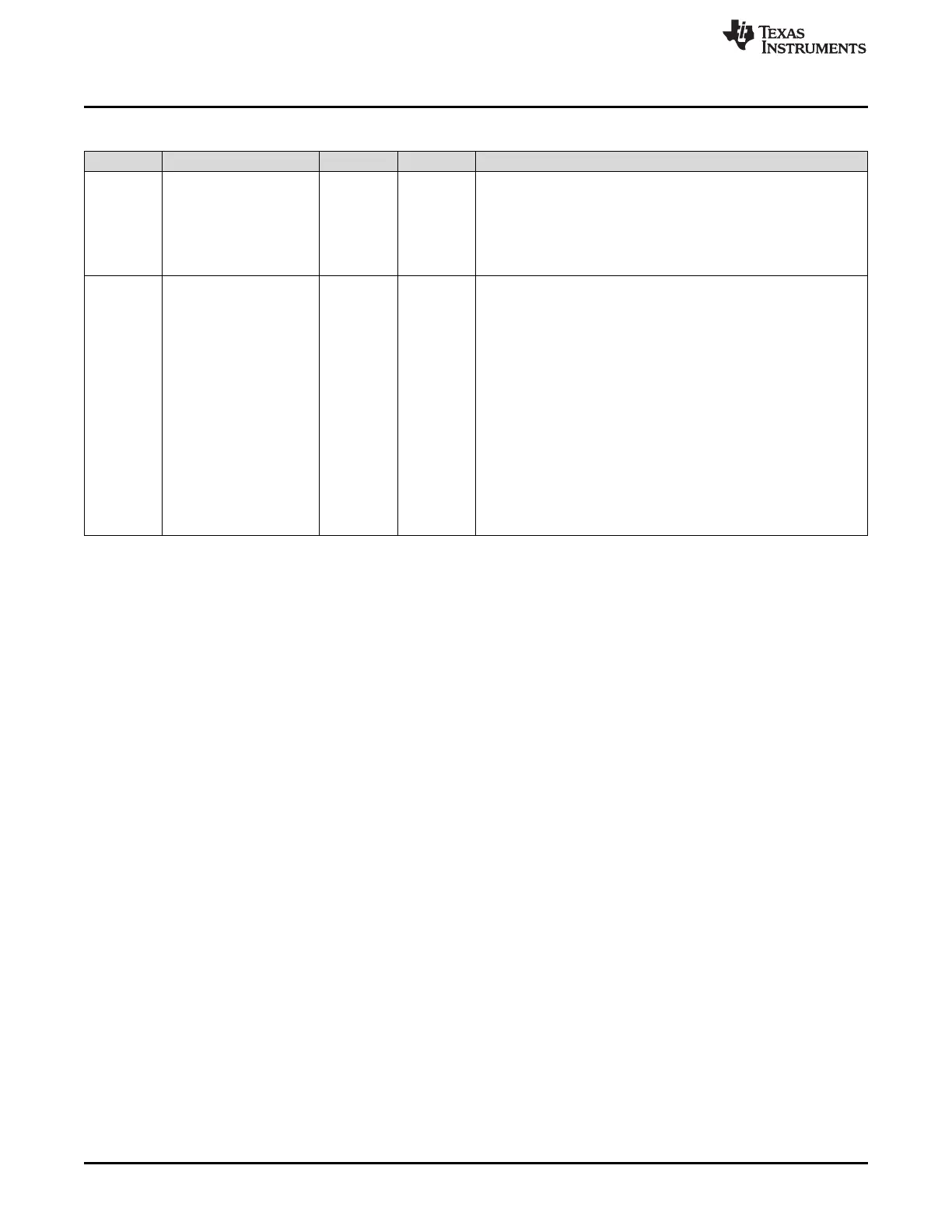

4-0 RXFFIL R/W 1Fh

Receive FIFO Interrupt Level Bits

Receive FIFO generates an interrupt when the FIFO status bits

(RXFFST4-0) are greater than or equal to the FIFO level bits

(RXFFIL4-0). The default value of these bits after reset is 11111.

This avoids frequent interrupts after reset, as the receive FIFO will

be empty most of the time.

Reset type: SYSRSn

0h (R/W) = A RX FIFO interrupt request is generated when there is

0 or more words in the RX buffer.

1h (R/W) = A RX FIFO interrupt request is generated when there

are 1 or more words in the RX buffer.

2h (R/W) = A RX FIFO interrupt request is generated when there

are 2 or more words in the RX buffer.

10h (R/W) = A RX FIFO interrupt request is generated when there

are 16 words in the RX buffer.

1Fh (R/W) = Reserved.

Loading...

Loading...