www.ti.com

I2C Registers

653

SPRUI07–March 2020

Submit Documentation Feedback

Copyright © 2020, Texas Instruments Incorporated

Inter-Integrated Circuit Module (I2C)

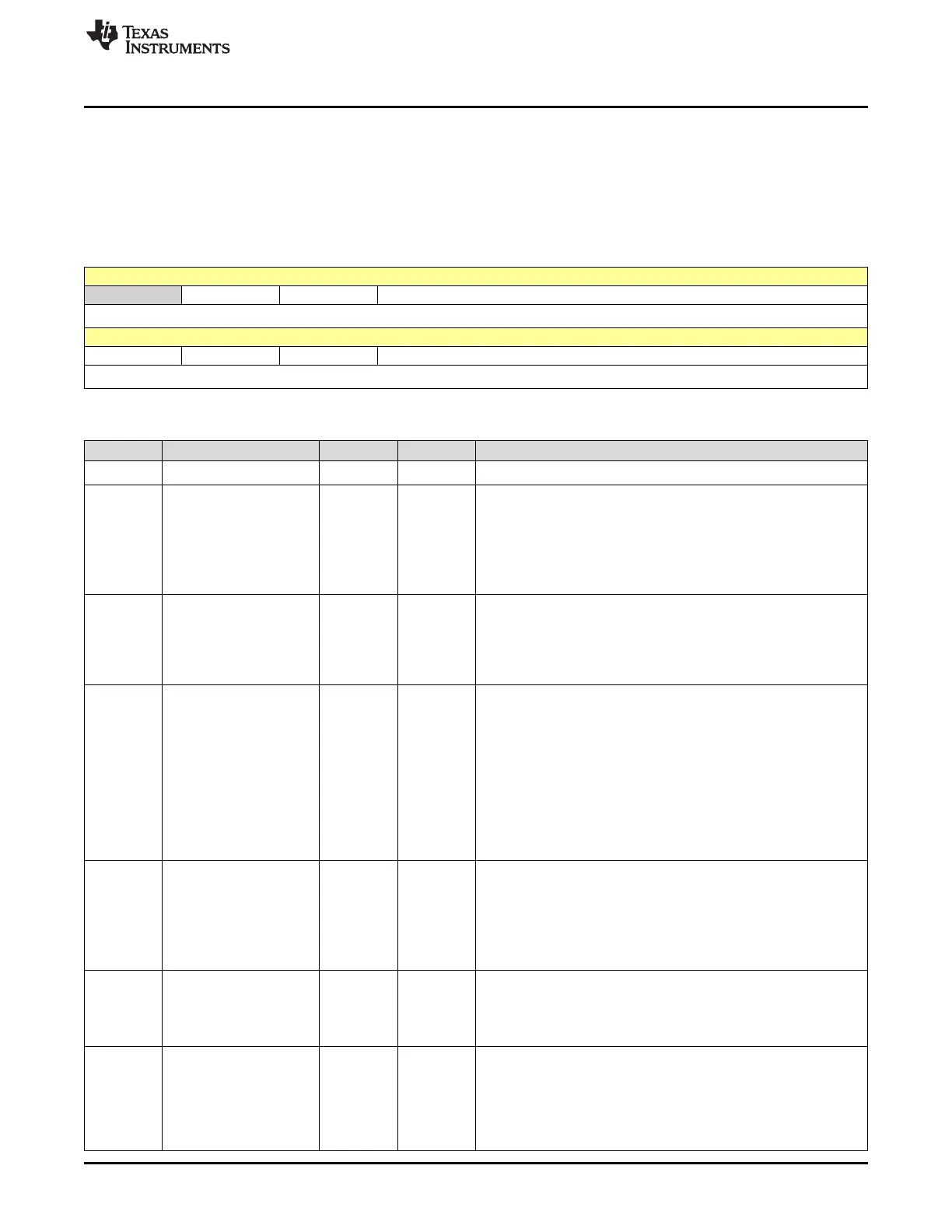

11.6.2.14 I2CFFTX Register (Offset = 20h) [reset = 0h]

I2CFFTX is shown in Figure 11-31 and described in Table 11-23.

Return to the Summary Table.

The I2C transmit FIFO register (I2CFFTX) is a 16-bit register that contains the I2C FIFO mode enable bit

as well as the control and status bits for the transmit FIFO mode of operation on the I2C peripheral.

Figure 11-31. I2CFFTX Register

15 14 13 12 11 10 9 8

RESERVED I2CFFEN TXFFRST TXFFST

R-0h R/W-0h R/W-0h R-0h

7 6 5 4 3 2 1 0

TXFFINT TXFFINTCLR TXFFIENA TXFFIL

R-0h R-0/W1S-0h R/W-0h R/W-0h

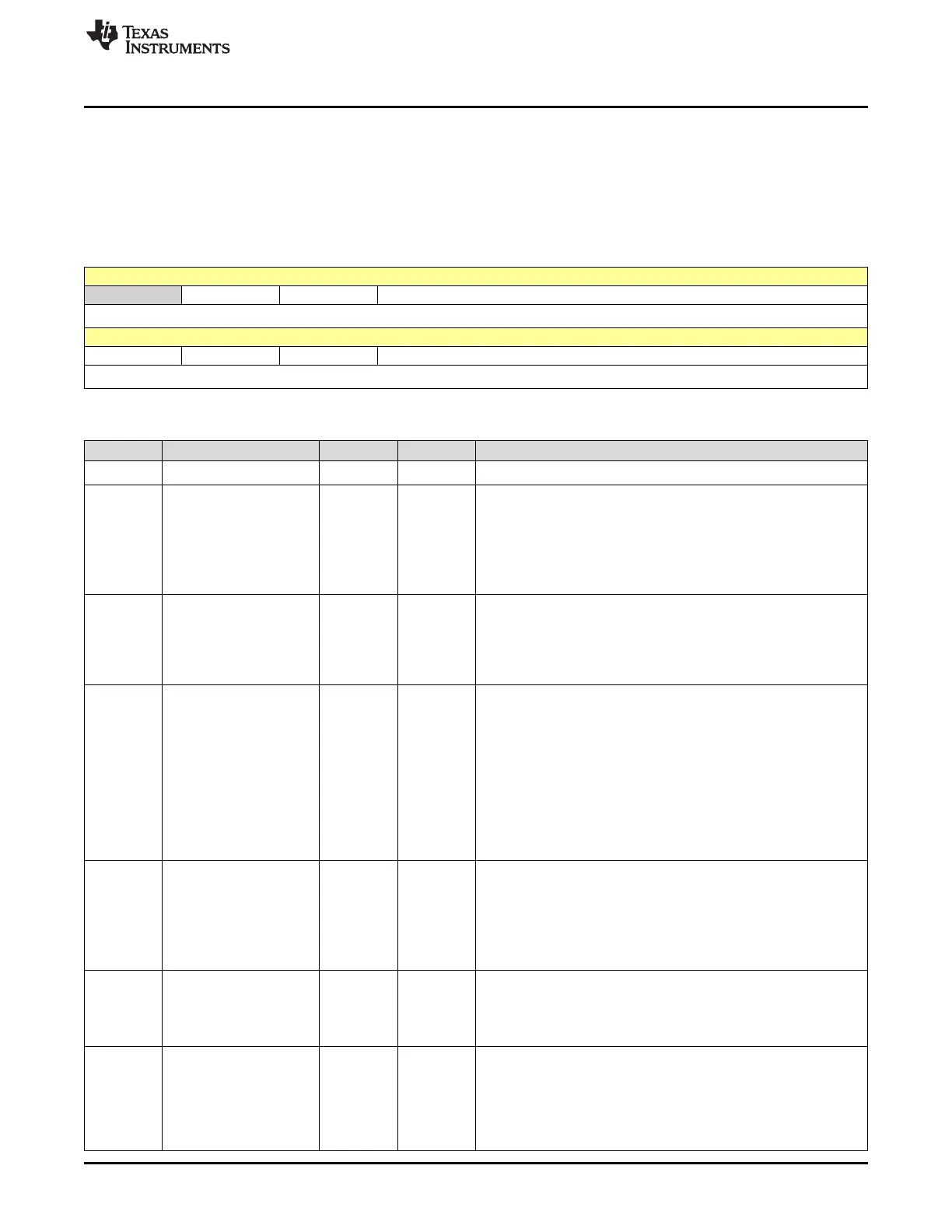

Table 11-23. I2CFFTX Register Field Descriptions

Bit Field Type Reset Description

15 RESERVED R 0h

Reserved

14 I2CFFEN R/W 0h

I2C FIFO mode enable bit.

This bit must be enabled for either the transmit or the receive FIFO

to operate correctly.

Reset type: SYSRSn

0h (R/W) = Disable the I2C FIFO mode.

1h (R/W) = Enable the I2C FIFO mode.

13 TXFFRST R/W 0h

Transmit FIFO Reset

Reset type: SYSRSn

0h (R/W) = Reset the transmit FIFO pointer to 0000 and hold the

transmit FIFO in the reset state.

1h (R/W) = Enable the transmit FIFO operation.

12-8 TXFFST R 0h

Contains the status of the transmit FIFO:

xxxxx Transmit FIFO contains xxxxx bytes.

00000 Transmit FIFO is empty.

Note: Since these bits are reset to zero, the transmit FIFO interrupt

flag will be set when the transmit FIFO operation is enabled and the

I2C is taken out of reset. This will generate a transmit FIFO interrupt

if enabled. To avoid any detrimental effects from this, write a one to

the TXFFINTCLR once the transmit FIFO operation is enabled and

the I2C is taken out of reset.

Reset type: SYSRSn

7 TXFFINT R 0h

Transmit FIFO interrupt flag.

This bit cleared by a CPU write of a 1 to the TXFFINTCLR bit. If the

TXFFIENA bit is set, this bit will generate an interrupt when it is set.

Reset type: SYSRSn

0h (R/W) = Transmit FIFO interrupt condition has not occurred.

1h (R/W) = Transmit FIFO interrupt condition has occurred.

6 TXFFINTCLR R-0/W1S 0h

Transmit FIFO Interrupt Flag Clear

Reset type: SYSRSn

0h (R/W) = Writes of zeros have no effect. Reads return a 0.

1h (R/W) = Writing a 1 to this bit clears the TXFFINT flag.

5 TXFFIENA R/W 0h

Transmit FIFO Interrupt Enable

Reset type: SYSRSn

0h (R/W) = Disabled. TXFFINT flag does not generate an interrupt

when set.

1h (R/W) = Enabled. TXFFINT flag does generate an interrupt

when set.

Loading...

Loading...