Clocking and System Control

www.ti.com

74

SPRUI07–March 2020

Submit Documentation Feedback

Copyright © 2020, Texas Instruments Incorporated

System Control and Interrupts

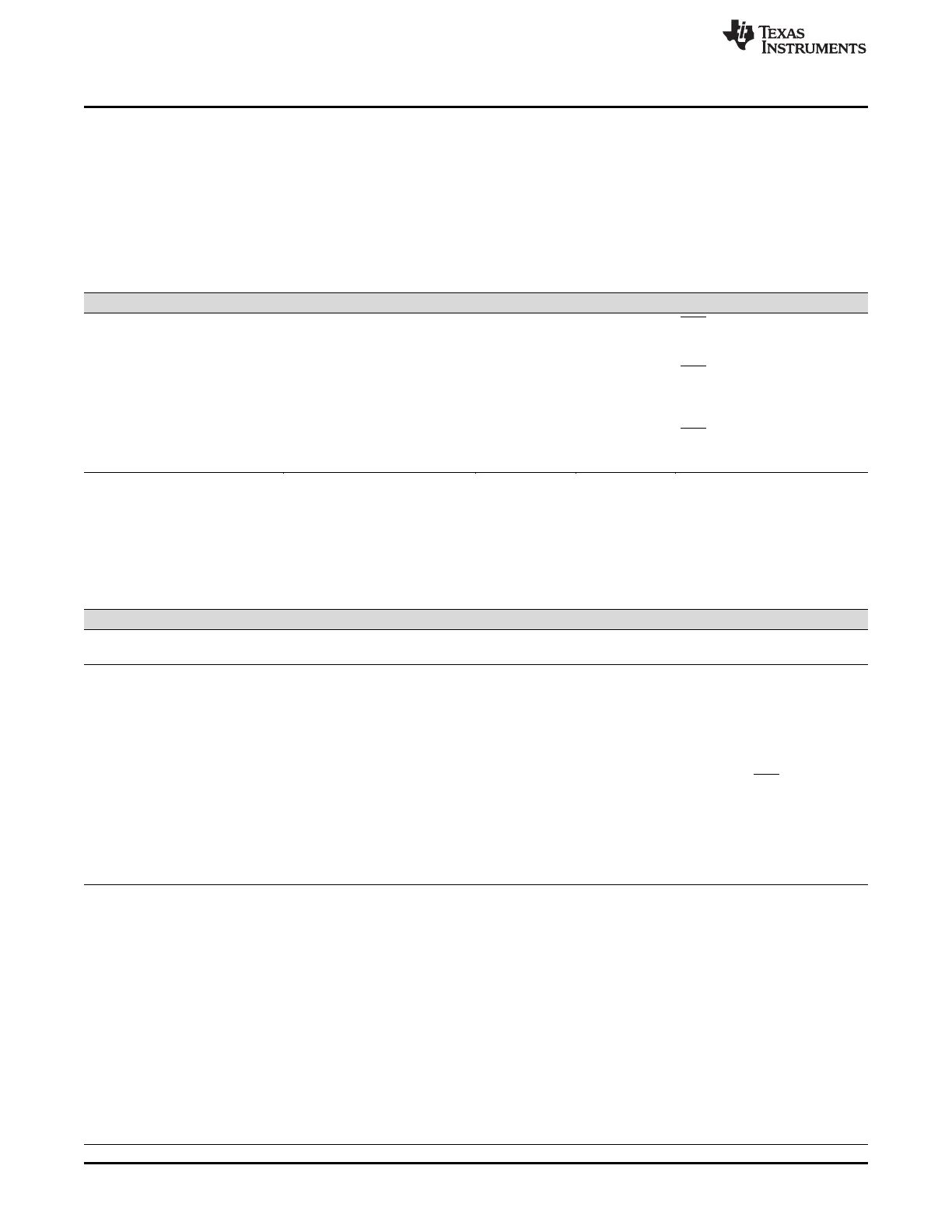

1.3.3 Low-Power Modes Block

Table 1-23 summarizes the various modes.

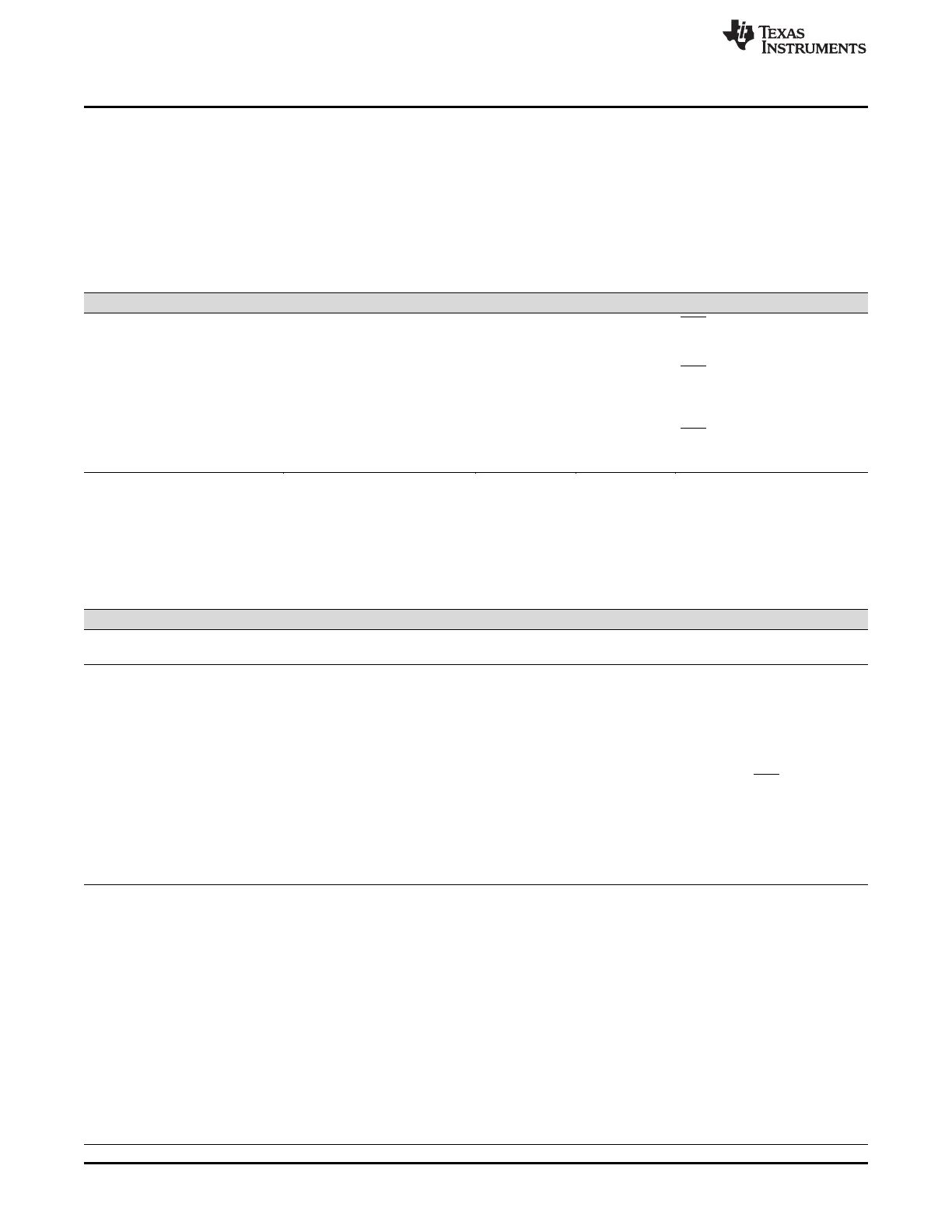

The various low-power modes operate as shown in Table 1-24.

See the TMS320F28335, TMS320F28334, TMS320F28332, TMS320F28235, TMS320F28234,

TMS320F28232 Digital Signal Controllers (DSCs) Data Manual (literature number SPRS439) for exact

timing for entering and exiting the low power modes.

(1)

The Exit column lists which signals or under what conditions the low power mode is exited. This signal must be kept low long enough for

an interrupt to be recognized by the device. Otherwise the IDLE mode is not exited and the device goes back into the indicated low

power mode.

(2)

The IDLE mode on the 28x behaves differently than on the 24x/240x. On the 28x, the clock output from the CPU (SYSCLKOUT) is still

functional while on the 24x/240x the clock is turned off.

(3)

On the 28x, the JTAG port can still function even if the clock to the CPU (CLKIN) is turned off.

Table 1-23. Low-Power Mode Summary

Mode LPMCR0[1:0] OSCCLK CLKIN SYSCLKOUT Exit

(1)

IDLE 00 On On On

(2)

XRS,

Watchdog interrupt,

Any enabled interrupt

STANDBY 01 On

(watchdog still running)

Off Off XRS,

Watchdog interrupt,

GPIO Port A signal,

Debugger

(3)

HALT 1X Off

(oscillator and PLL turned off,

watchdog not functional)

Off Off XRS,

GPIO Port A Signal,

Debugger

(3)

Table 1-24. Low Power Modes

Mode Description

IDLE

Mode:

This mode is exited by any enabled interrupt or an NMI. The LPM block itself performs no tasks during this mode.

STANDBY

Mode:

If the LPM bits in the LPMCR0 register are set to 01, the device enters STANDBY mode when the IDLE instruction is

executed. In STANDBY mode the clock input to the CPU (CLKIN) is disabled, which disables all clocks derived from

SYSCLKOUT. The oscillator and PLL and watchdog will still function. Before entering the STANDBY mode, you should

perform the following tasks:

• Enable the WAKEINT interrupt in the PIE module. This interrupt is connected to both the watchdog and the low

power mode module interrupt.

• If desired, specify one of the GPIO port A signals to wake the device in the GPIOLPMSEL register. The

GPIOLPMSEL register is part of the GPIO module. In addition to the selected GPIO signal, the XRS input and the

watchdog interrupt, if enabled in the LPMCR0 register, can wake the device from the STANDBY mode.

• Select the input qualification in the LPMCR0 register for the signal that will wake the device.

When the selected external signal goes low, it must remain low a number of OSCCLK cycles as specified by the

qualification period in the LPMCR0 register. If the signal should be sampled high during this time, the qualification will

restart. At the end of the qualification period, the PLL enables the CLKIN to the CPU and the WAKEINT interrupt is

latched in the PIE block. The CPU then responds to the WAKEINT interrupt if it is enabled.

HALT

Mode:

If the LPM bits in the LPMCR0 register are set to 1x, the device enters the HALT mode when the IDLE instruction is

executed. In HALT mode all of the device clocks, including the PLL and oscillator, are shut down. Before entering the

HALT mode, you should perform the following tasks:

• Enable the WAKEINT interrupt in the PIE module (PIEIER1.8 = 1). This interrupt is connected to both the

watchdog and the Low-Power-Mode module interrupt.

• Specify one of the GPIO port A signals to wake the device in the GPIOLPMSEL register. The GPIOLPMSEL

register is part of the GPIO module. In addition to the selected GPIO signal, the XRS input can also wake the

device from the HALT mode

• Disable all interrupts with the possible exception of the HALT mode wakeup interrupt. The interrupts can be re-

enabled after the device is brought out of HALT mode.

• For device to exit HALT mode properly, the following conditions must be met:

Bit 7 (INT1.8) of PIEIER1 register should be 1.

Bit 0 (INT1) of IER register must be 1.

• If the above conditions are met,

– WAKE_INT ISR will be executed first, followed by the instruction(s) after IDLE, if INTM = 0.

– WAKE_INT ISR will not be executed and instruction(s) after IDLE will be executed, if INTM = 1.

Loading...

Loading...