www.ti.com

XINTF Registers

861

SPRUI07–March 2020

Submit Documentation Feedback

Copyright © 2020, Texas Instruments Incorporated

External Interface (XINTF)

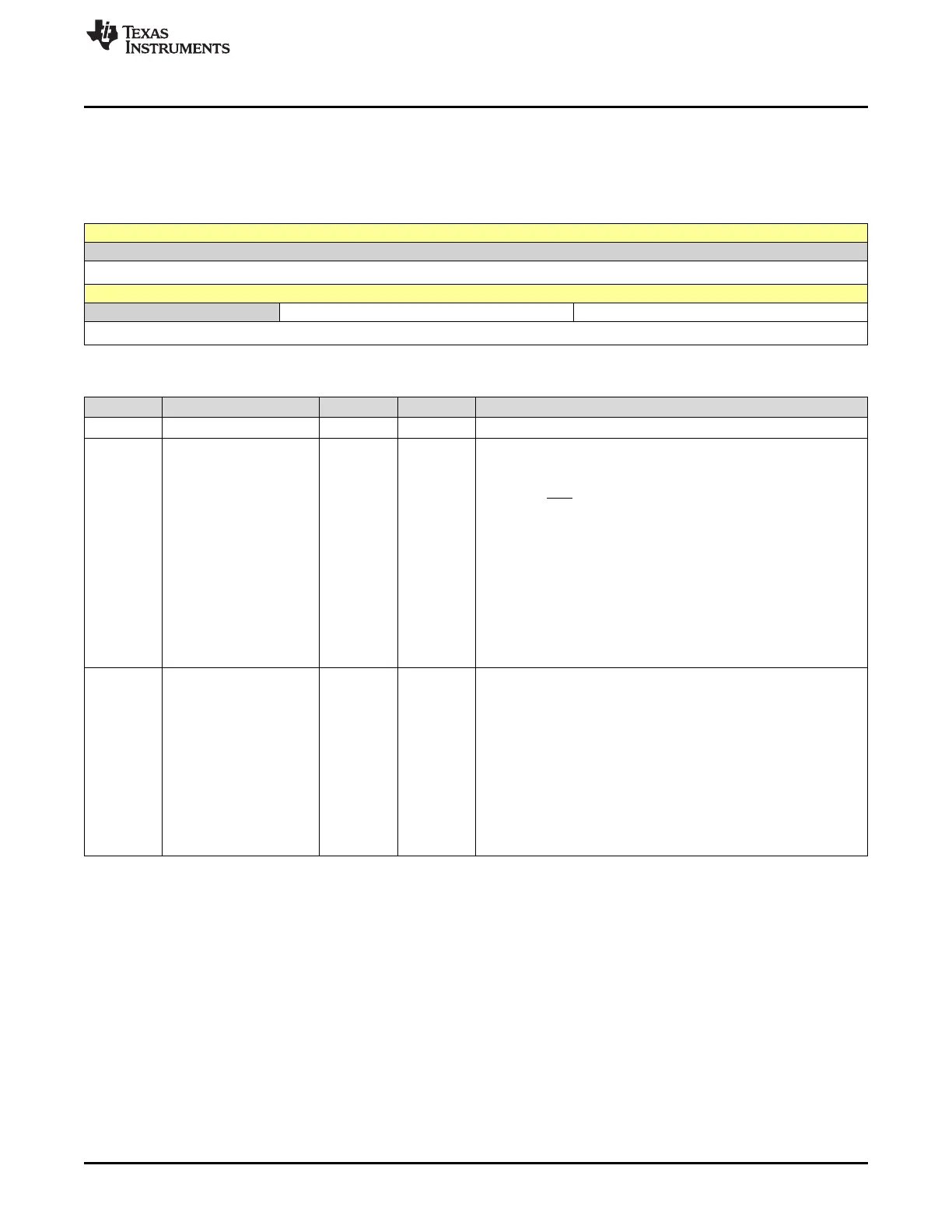

14.6.5 XBANK Register (Offset = B38h) [reset = 9h]

XBANK is shown in Figure 14-10 and described in Table 14-18.

This register is EALLOW protected.

Figure 14-10. XBANK Register

15 14 13 12 11 10 9 8

RESERVED

R-0h

7 6 5 4 3 2 1 0

RESERVED BCYC BANK

R-0h R/W-1h R/W-1h

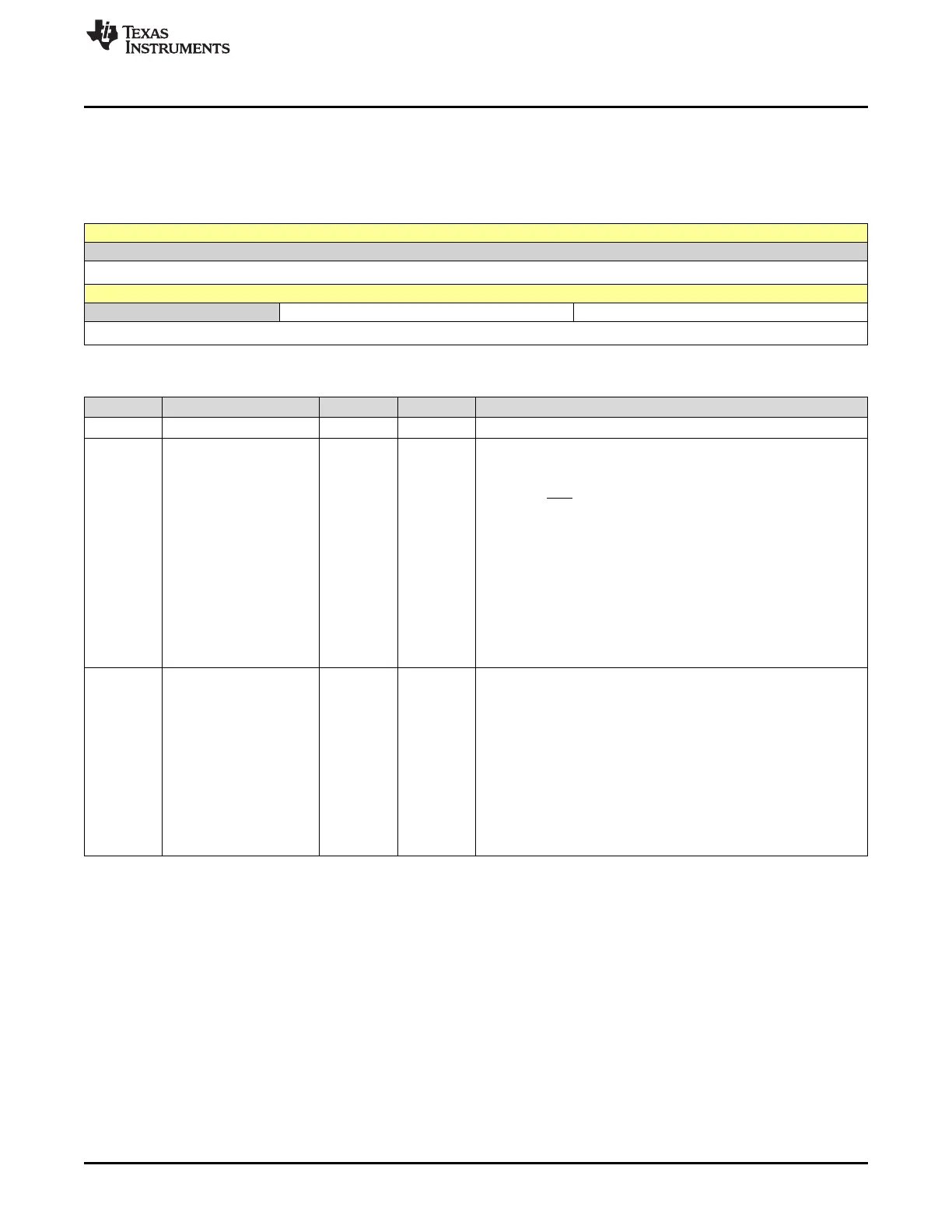

Table 14-18. XBANK Register Field Descriptions

Bit Field Type Reset Description

15-6 RESERVED R 0h

5-3 BCYC R/W 1h These bits specify the number of XTIMCLK cycles to add between

any consecutive access that crosses into or out of the specified

zone, be it a read or write, program or data space.

The number of XTIMCLK cycles can be 0 to 7.

On a reset (XRS), the value defaults to 7 XTIMCLK cycles (14

SYSCLKOUT cycles).

0h = 0 cycle

1h = 1 XTIMCLK cycle

2h = 2 XTIMCLK cycles

3h = 3 XTIMCLK cycles

4h = 4 XTIMCLK cycles

5h = 5 XTIMCLK cycles

6h = 6 XTIMCLK cycles

7h = 7 XTIMCLK cycles (default)

2-0 BANK R/W 1h These bits specify the XINTF zone for which bank switching is

enabled, ZONE 0 to ZONE 7.

At reset, XINTF Zone 7 is selected.

0h = Zone 0

1h = Reserved

2h = Reserved

3h = Reserved

4h = Reserved

5h = Reserved

6h = Zone 6

7h = Zone 7 (selected at reset by default)

Loading...

Loading...