www.ti.com

SCI Registers

605

SPRUI07–March 2020

Submit Documentation Feedback

Copyright © 2020, Texas Instruments Incorporated

Serial Communications Interface (SCI)

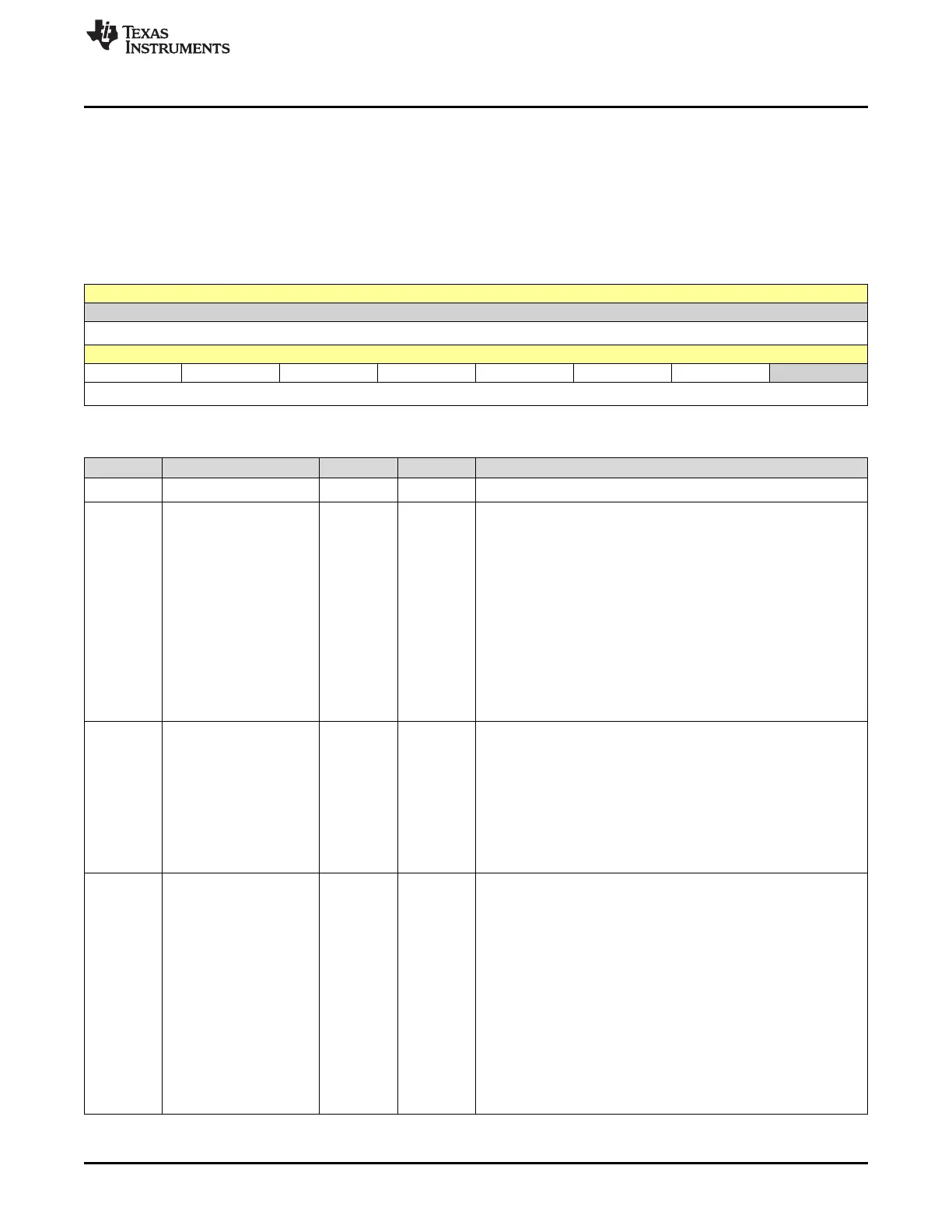

10.14.2.6 SCIRXST Register (Offset = 5h) [reset = 0h]

SCIRXST is shown in Figure 10-16 and described in Table 10-12.

Return to the Summary Table.

SCIRXST contains seven bits that are receiver status flags (two of which can generate interrupt requests).

Each time a complete character is transferred to the receiver buffers (SCIRXEMU and SCIRXBUF), the

status flags are updated.

Figure 10-16. SCIRXST Register

15 14 13 12 11 10 9 8

RESERVED

R-0h

7 6 5 4 3 2 1 0

RXERROR RXRDY BRKDT FE OE PE RXWAKE RESERVED

R-0h R-0h R-0h R-0h R-0h R-0h R-0h R-0h

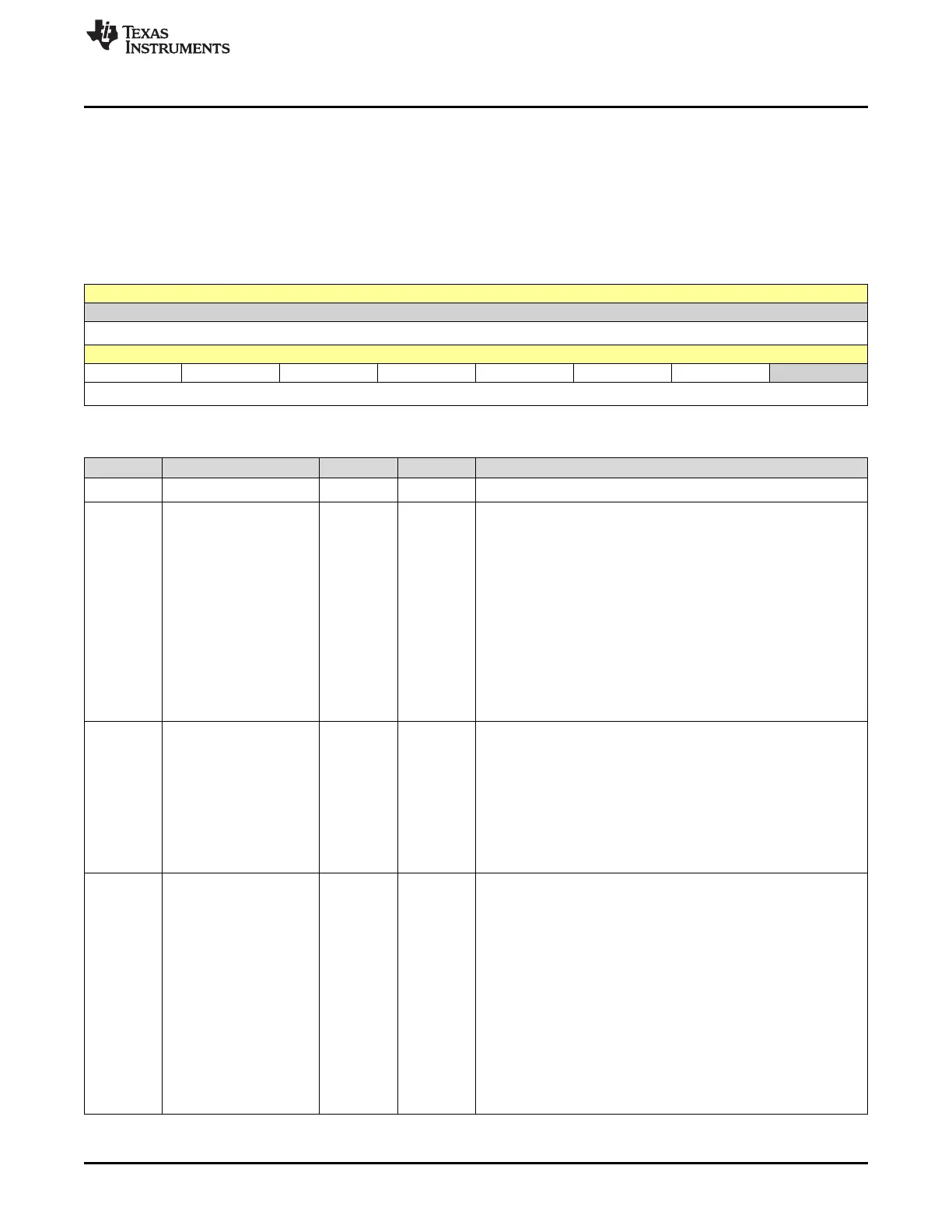

Table 10-12. SCIRXST Register Field Descriptions

Bit Field Type Reset Description

15-8 RESERVED R 0h

Reserved

7 RXERROR R 0h

SCI receiver error flag.

The RX ERROR flag indicates that one of the error flags in the

receiver status register is set. RX ERROR is a logical OR of the

break detect, framing error, overrun, and parity error enable flags

(bits 5-2: BRKDT, FE, OE, and PE).

A 1 on this bit will cause an interrupt if the RX ERR INT ENA bit

(SCICTL1.6) is set. This bit can be used for fast error-condition

checking during the interrupt service routine. This error flag cannot

be cleared directly

it is cleared by an active SW RESET or by a system reset.

Reset type: SYSRSn

0h (R/W) = No error flags set

1h (R/W) = Error flag(s) set

6 RXRDY R 0h

SCI receiver-ready flag.

When a new character is ready to be read from the SCIRXBUF

register, the receiver sets this bit, and a receiver interrupt is

generated if the RX/BK INT ENA bit (SCICTL2.1) is a 1. RXRDY is

cleared by a reading of the SCIRXBUF register, by an active SW

RESET, or by a system reset.

Reset type: SYSRSn

0h (R/W) = No new character in SCIRXBUF

1h (R/W) = Character ready to be read from SCIRXBUF

5 BRKDT R 0h

SCI break-detect flag.

The SCI sets this bit when a break condition occurs. A break

conditionoccurs when the SCI receiver data line (SCIRXD) remains

continuously low for at least ten bits,

beginning after a missing first stop bit. The occurrence of a break

causes a receiver interrupt to be generated if the RX/BK INT ENA bit

is a 1, but it does not cause the receiver buffer to be loaded. A

BRKDT interrupt can occur even if the receiver SLEEP bit is set to 1.

BRKDT is cleared by an active SW RESET or by a system reset. It

is not cleared by receipt of a character after the break is detected. In

order to receive more characters, the SCI must be reset by toggling

the SW RESET bit or by a system reset.

Reset type: SYSRSn

0h (R/W) = No break condition

1h (R/W) = Break condition occurred

Loading...

Loading...