www.ti.com

McBSP Registers

771

SPRUI07–March 2020

Submit Documentation Feedback

Copyright © 2020, Texas Instruments Incorporated

Multichannel Buffered Serial Port (McBSP)

Table 12-96. Use of the Transmit Channel Enable Registers (continued)

Number of

Selectable

Channels

Block Assignments Channel Assignments

XCERx Block Assigned Bit in XCERx Channel Assigned

XCERE Block 4 XCE0 Channel 64

XCE1 Channel 65

XCE2 Channel 66

: :

XCE15 Channel 79

XCERF Block 5 XCE0 Channel 80

XCE1 Channel 81

XCE2 Channel 82

: :

XCE15 Channel 95

XCERG Block 6 XCE0 Channel 96

XCE1 Channel 97

XCE2 Channel 98

: :

XCE15 Channel 111

XCERH Block 7 XCE0 Channel 112

XCE1 Channel 113

XCE2 Channel 114

: :

XCE15 Channel 127

12.15.13 McBSP Interrupt Enable Register

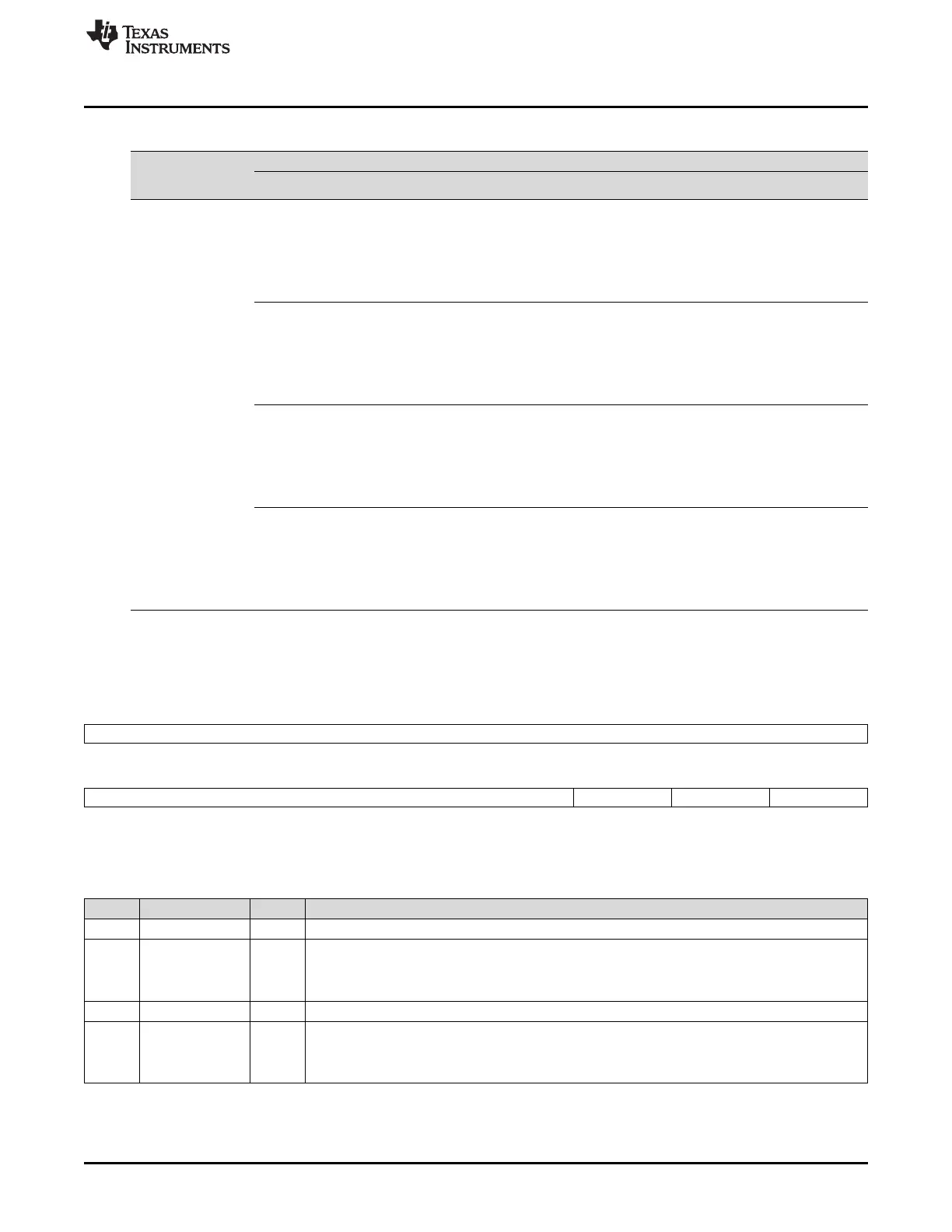

Figure 12-82. McBSP Interrupt Enable Register (MFFINT)

15 8

Reserved

R-0

7 3 2 1 0

Reserved RINT ENA Reserved XINT ENA

R-0 R/W-0 R-0 R/W-0

LEGEND: R/W = Read/Write; R = Read only; -n = value after reset

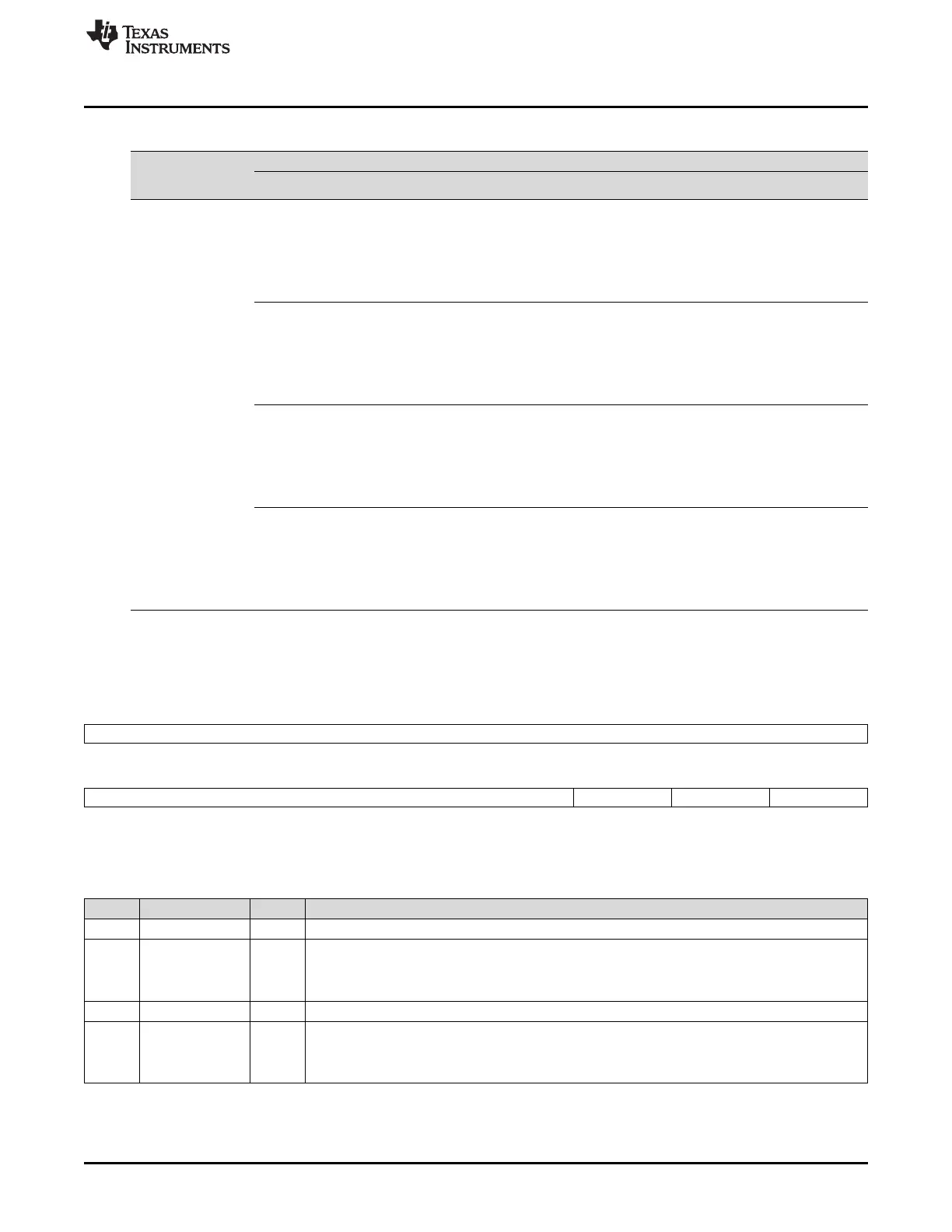

Table 12-97. McBSP Interrupt Enable Register (MFFINT) Field Descriptions

Bit Field Value Description

15:3 Reserved Reserved

2 RINT ENA Enable for Receive Interrupt

0 Receive interrupt on RRDY is disabled.

1 Receive interrupt on RRDY is enabled.

1 Reserved

0 XINT ENA Enable for transmit Interrupt

0 Transmit interrupt on XRDY is disabled.

1 Transmit interrupt on XRDY is enabled.

Loading...

Loading...