www.ti.com

I2C Registers

651

SPRUI07–March 2020

Submit Documentation Feedback

Copyright © 2020, Texas Instruments Incorporated

Inter-Integrated Circuit Module (I2C)

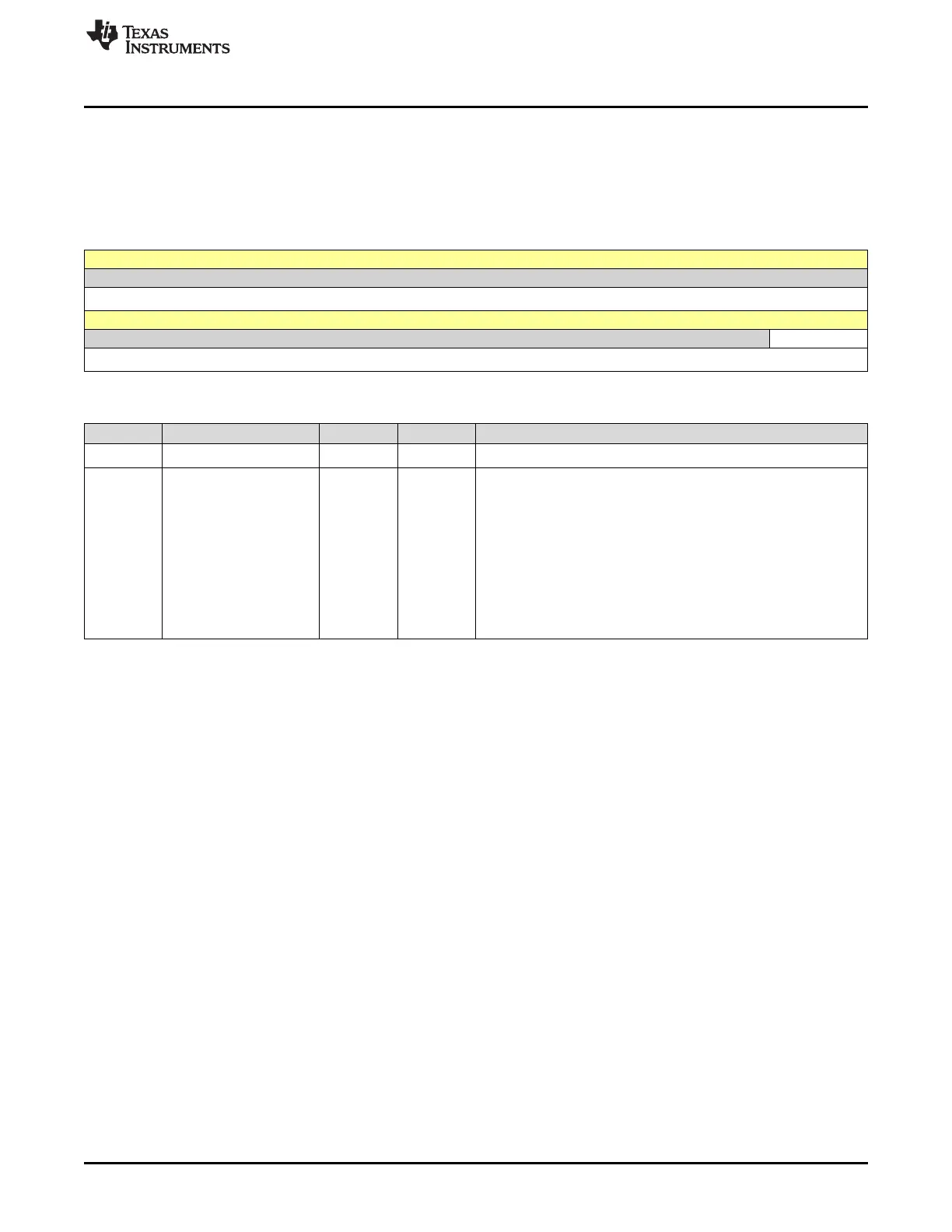

11.6.2.12 I2CEMDR Register (Offset = Bh) [reset = 1h]

I2CEMDR is shown in Figure 11-29 and described in Table 11-21.

Return to the Summary Table.

I2C Extended Mode

Figure 11-29. I2CEMDR Register

15 14 13 12 11 10 9 8

RESERVED

R-0h

7 6 5 4 3 2 1 0

RESERVED BC

R-0h R/W-1h

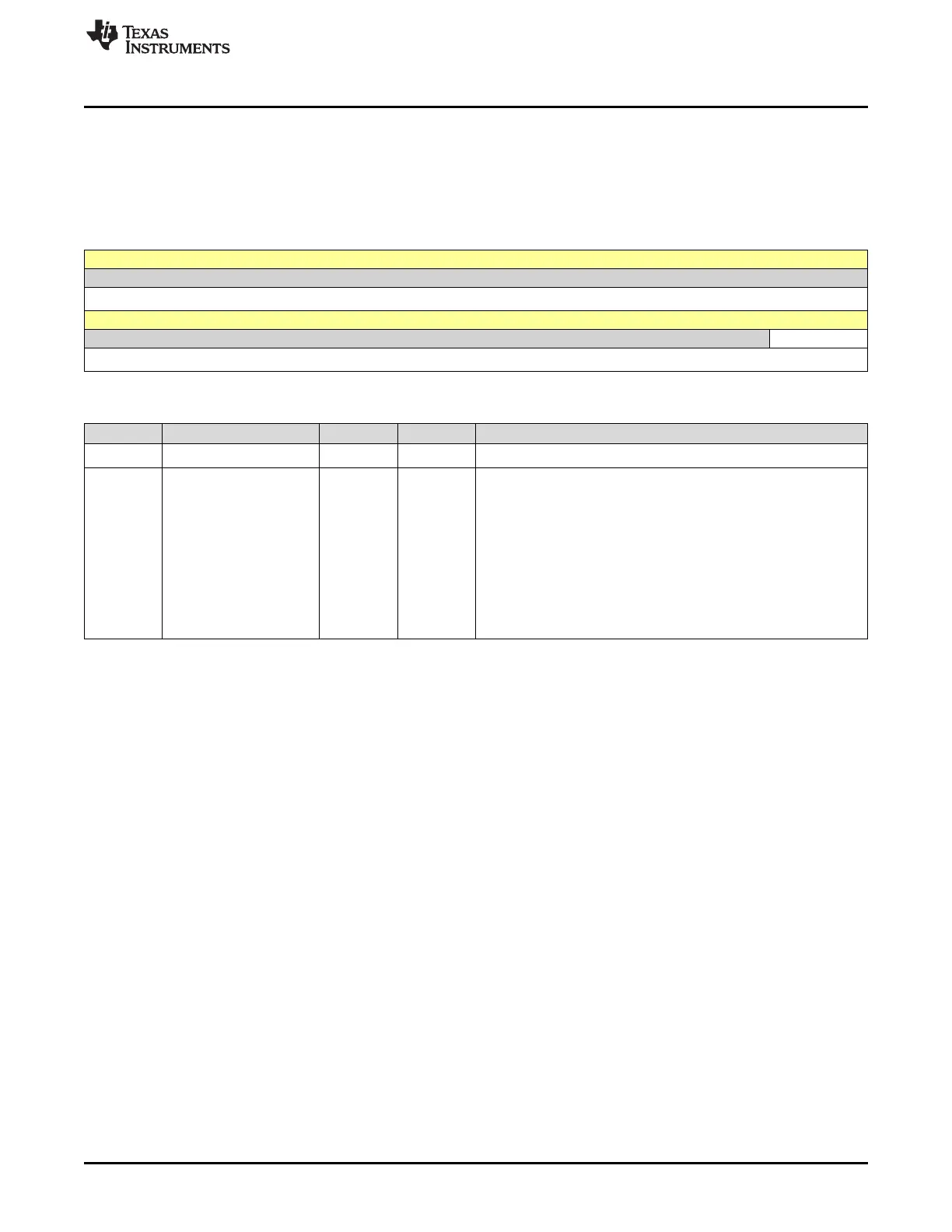

Table 11-21. I2CEMDR Register Field Descriptions

Bit Field Type Reset Description

15-1 RESERVED R 0h

Reserved

0 BC R/W 1h

Backwards compatibility mode.

This bit affects the timing of the transmit status bits (XRDY and

XSMT) in the I2CSTR register when in slave transmitter mode.

Check Backwards Compatibility Mode Bit, Slave Transmitter diagram

for more details.

Reset type: SYSRSn

0h (R/W) = See the "Backwards Compatibility Mode Bit, Slave

Transmitter" Figure for details.

1h (R/W) = See the "Backwards Compatibility Mode Bit, Slave

Transmitter" Figure for details.

Loading...

Loading...