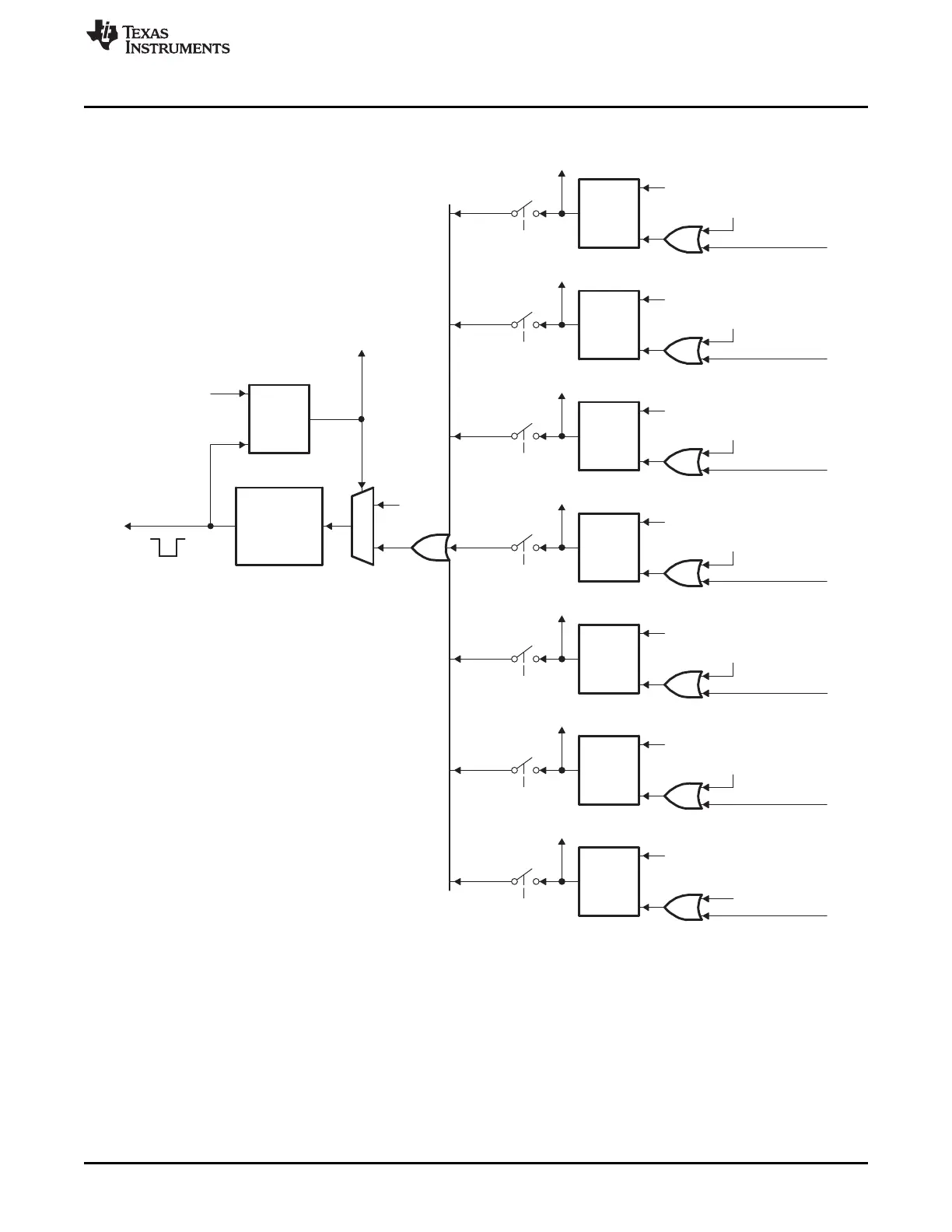

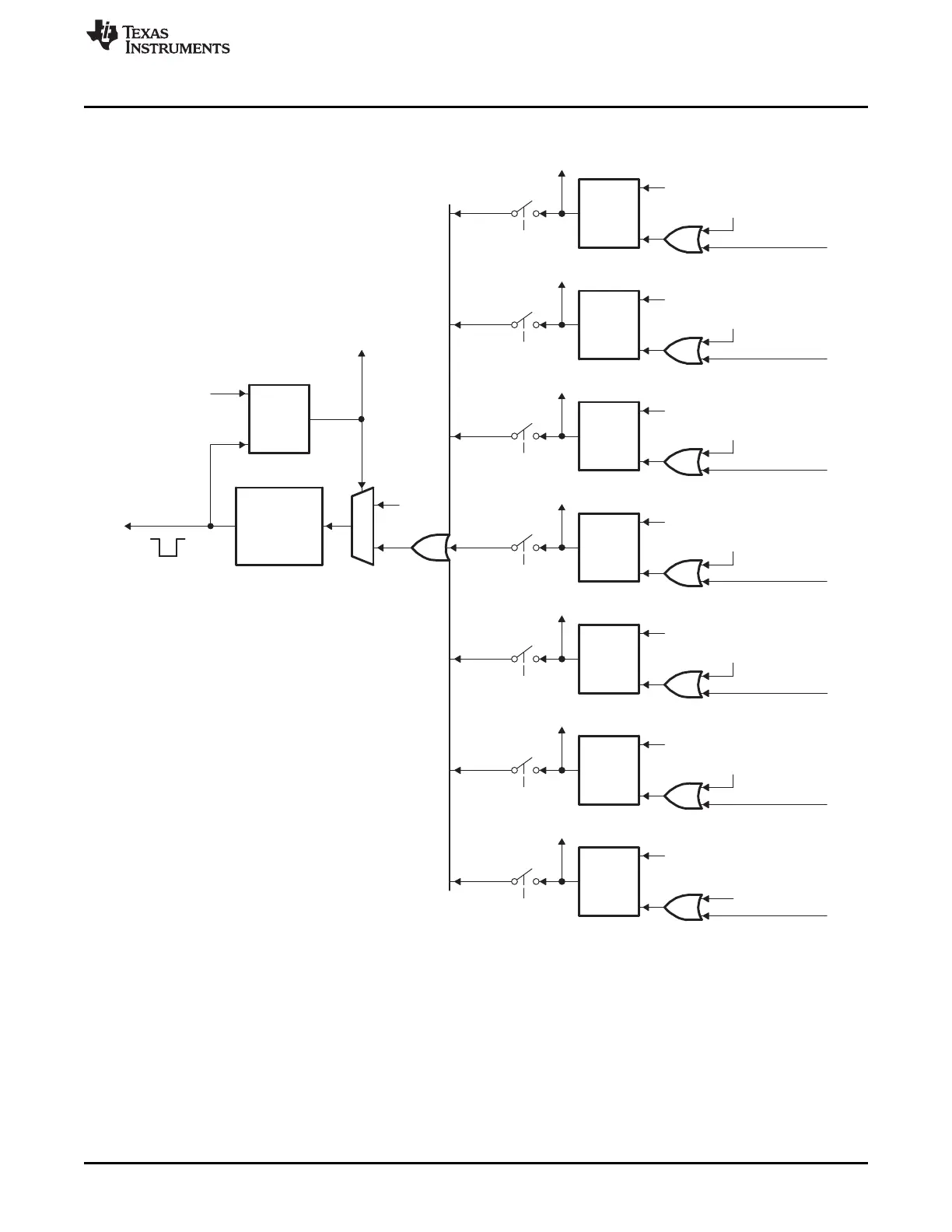

PRDEQ

Clear

Set

Latch

CEVT1

ECFRC

ECCLR

ECFLG

ECEINT

ECCLR

ECEINT Set

Clear

Latch

CEVT2

ECFRC

ECFLG

ECCLR

ECCLR

Clear

ECEINT

Latch

Set

ECFLG

ECEINT Set

Clear

Latch

ECFRC

CEVT4

CEVT3

ECFRC

ECFLG

ECFRC

ECCLR

ECEINT Set

ECEINT

ECFLG

Latch

Clear

Latch

Set

CMPEQ

ECFRC

ECCLR

ECCLRClear

ECFLG

ECEINT

Clear

Latch

Set

ECFRC

CTROVF

ECFLG

01

0

Generate

interrupt

pulse when

input=1

Latch

Clear

Set

ECCLR

ECAPxINT

ECFLG

www.ti.com

Capture Mode Description

361

SPRUI07–March 2020

Submit Documentation Feedback

Copyright © 2020, Texas Instruments Incorporated

Enhanced Capture (eCAP)

Figure 5-9. Interrupts in eCAP Module

5.5.7 Shadow Load and Lockout Control

In capture mode, this logic inhibits (locks out) any shadow loading of CAP1 or CAP2 from APRD and

ACMP registers, respectively.

In APWM mode, shadow loading is active and two choices are permitted:

• Immediate - APRD or ACMP are transferred to CAP1 or CAP2 immediately upon writing a new value.

• On period equal, CTR[31:0] = PRD[31:0].

5.5.8 APWM Mode Operation

Main operating highlights of the APWM section:

Loading...

Loading...