DXR1 to XSR1 copyDXR2 to XSR2 copy

RBR1 to DRR1 copyRBR2 to DRR2 copy

DX

FSX

CLKX

DR

FSR

CLKR

DX

FSX

CLKX

DR

FSR

CLKR

DXR1 to XSR1 copyDXR1 to XSR1 copyDXR1 to XSR1 copyDXR1 to XSR1 copy

RSR1 to RBR1 copyRSR1 to RBR1 copyRSR1 to RBR1 copyRSR1 to RBR1 copy

Data Packing Examples

www.ti.com

740

SPRUI07–March 2020

Submit Documentation Feedback

Copyright © 2020, Texas Instruments Incorporated

Multichannel Buffered Serial Port (McBSP)

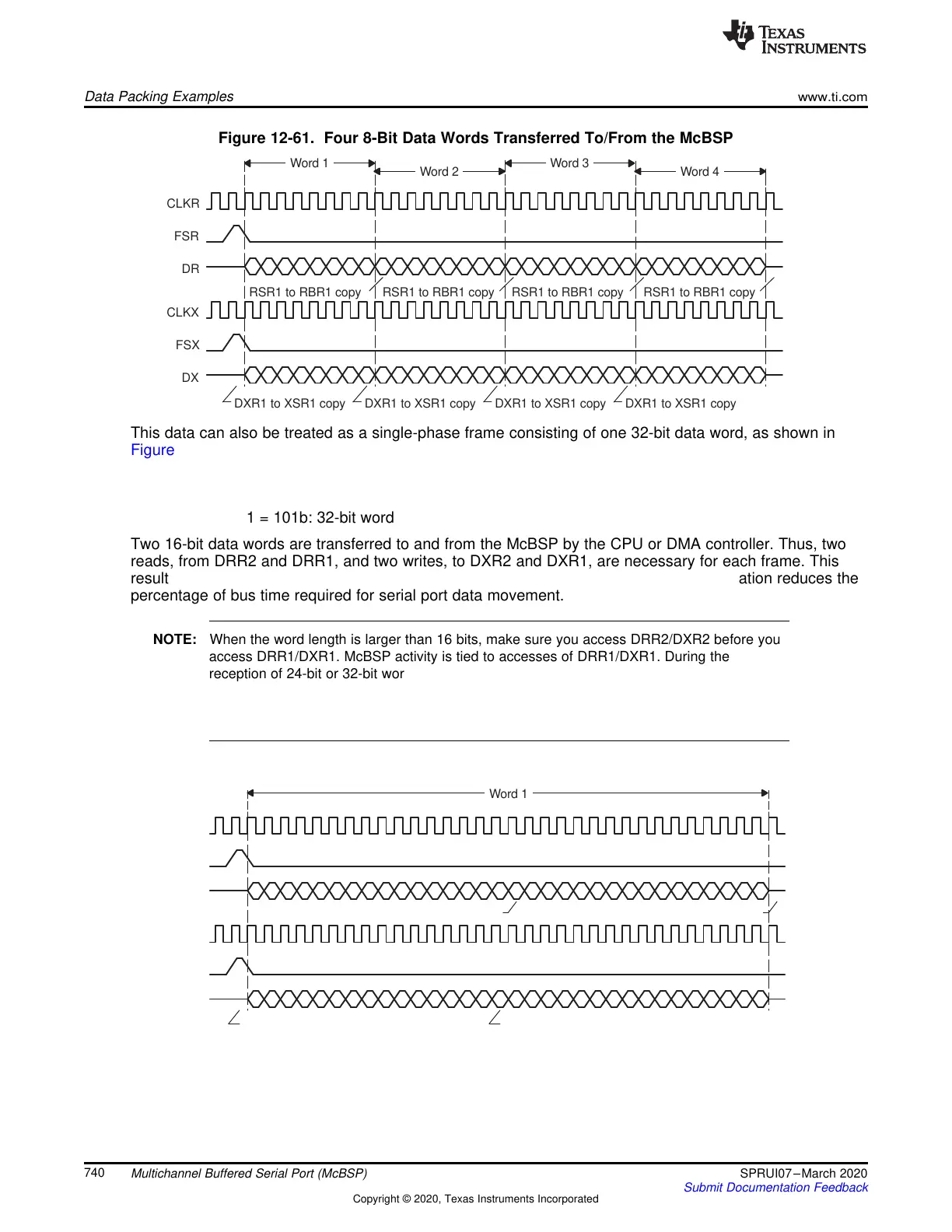

Figure 12-61. Four 8-Bit Data Words Transferred To/From the McBSP

This data can also be treated as a single-phase frame consisting of one 32-bit data word, as shown in

Figure 12-62. In this case:

• (R/X)PHASE = 0: Single-phase frame

• (R/X)FRLEN1 = 0000000b: 1-word frame

• (R/X)WDLEN1 = 101b: 32-bit word

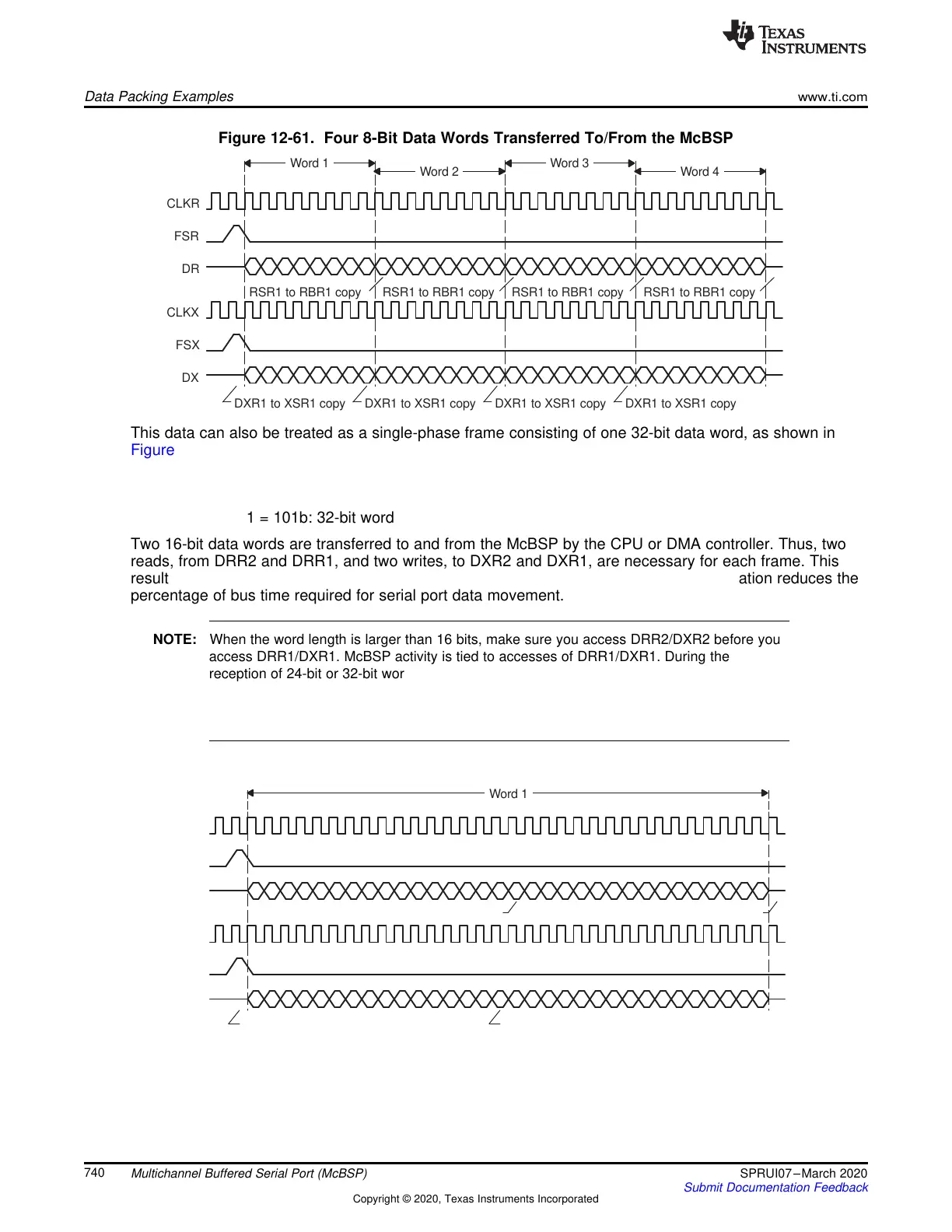

Two 16-bit data words are transferred to and from the McBSP by the CPU or DMA controller. Thus, two

reads, from DRR2 and DRR1, and two writes, to DXR2 and DXR1, are necessary for each frame. This

results in only half the number of transfers compared to the previous case. This manipulation reduces the

percentage of bus time required for serial port data movement.

NOTE: When the word length is larger than 16 bits, make sure you access DRR2/DXR2 before you

access DRR1/DXR1. McBSP activity is tied to accesses of DRR1/DXR1. During the

reception of 24-bit or 32-bit words, read DRR2 and then read DRR1. Otherwise, the next

RBR[1,2]-to-DRR[1,2] copy occurs before DRR2 is read. Similarly, during the transmission of

24-bit or 32-bit words, write to DXR2 and then write to DXR1. Otherwise, the next DXR[1,2]-

to-XSR[1,2] copy occurs before DXR2 is loaded with new data.

Figure 12-62. One 32-Bit Data Word Transferred To/From the McBSP

Loading...

Loading...