Frame ignored Frame ignored

FSX

DX

Frame ignored

DXR1 to XSR1 copy

DR

FSR

CLKR

RBR1 to DRR1 copy

RBR2 to DRR2 copy

Frame ignoredFrame ignoredFrame ignored

DX

FSX

CLKX

DR

FSR

CLKR

DXR1 to XSR1 copyDXR1 to XSR1 copyDXR1 to XSR1 copyDXR1 to XSR1 copy

RBR1 to DRR1 copyRBR1 to DRR1 copyRBR1 to DRR1 copyRBR1 to DRR1 copy

www.ti.com

Data Packing Examples

741

SPRUI07–March 2020

Submit Documentation Feedback

Copyright © 2020, Texas Instruments Incorporated

Multichannel Buffered Serial Port (McBSP)

12.11.2 Data Packing Using Word Length and the Frame-Synchronization Ignore Function

When there are multiple words per frame, you can implement data packing by increasing the word length

(defining a serial word with more bits) and by ignoring frame-synchronization pulses. First, consider

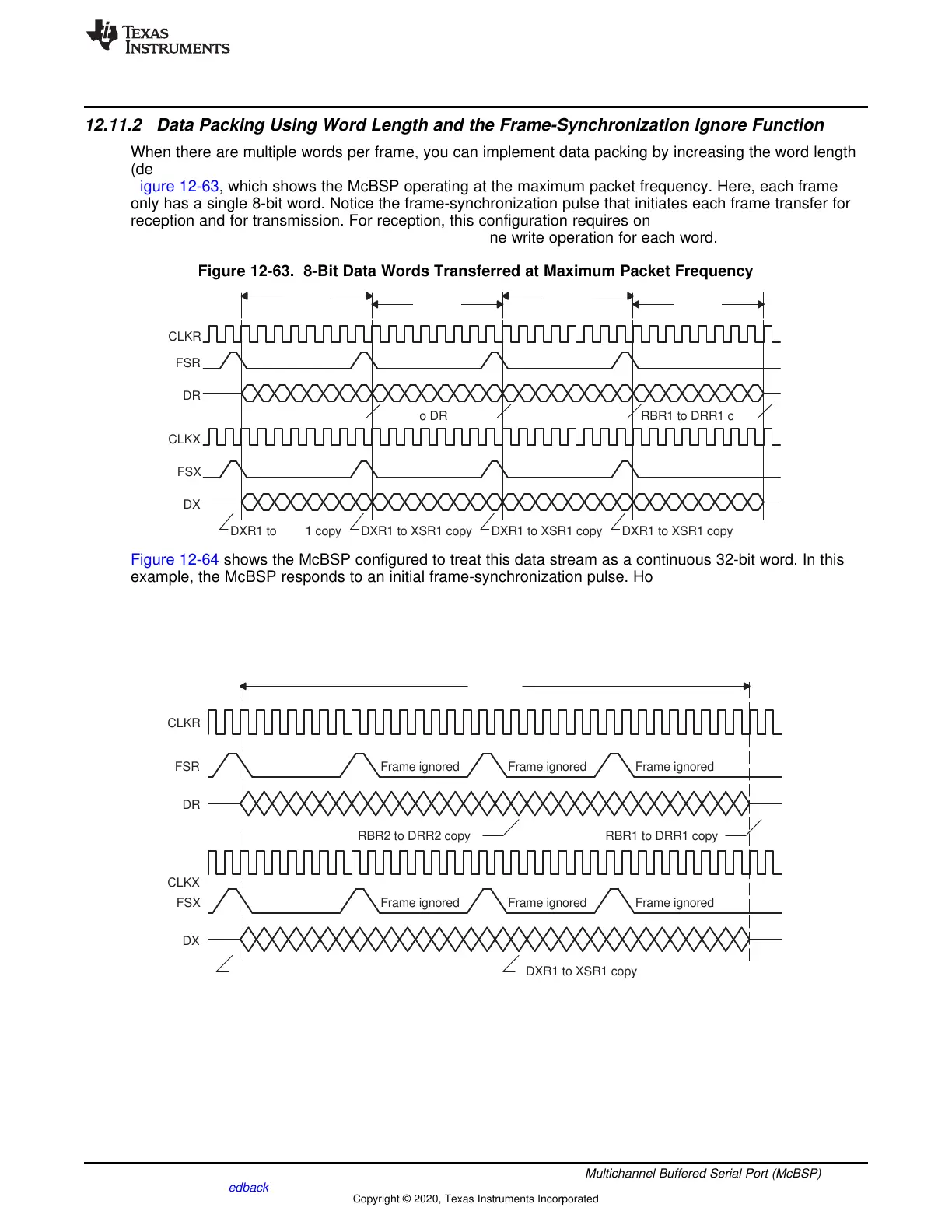

Figure 12-63, which shows the McBSP operating at the maximum packet frequency. Here, each frame

only has a single 8-bit word. Notice the frame-synchronization pulse that initiates each frame transfer for

reception and for transmission. For reception, this configuration requires one read operation for each

word. For transmission, this configuration requires one write operation for each word.

Figure 12-63. 8-Bit Data Words Transferred at Maximum Packet Frequency

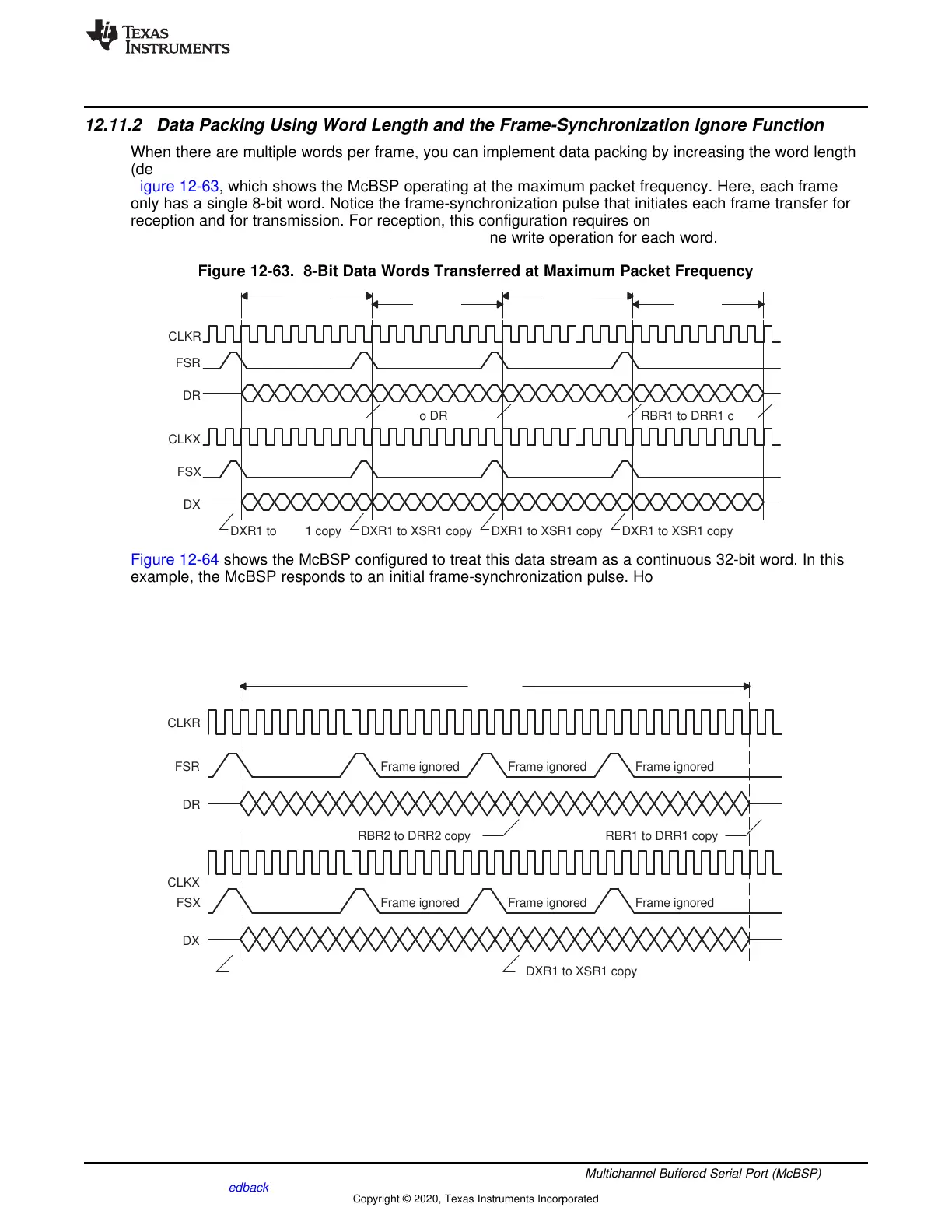

Figure 12-64 shows the McBSP configured to treat this data stream as a continuous 32-bit word. In this

example, the McBSP responds to an initial frame-synchronization pulse. However, (R/X)FIG = 1 so that

the McBSP ignores subsequent pulses. Only two read transfers or two write transfers are needed every

32 bits. This configuration effectively reduces the required bus bandwidth to half the bandwidth needed to

transfer four 8-bit words.

Figure 12-64. Configuring the Data Stream of Figure 12-63 as a Continuous 32-Bit Word

12.12 Interrupt Generation

McBSP registers can be programmed to receive and transmit data through DRR2/DRR1 and DXR2/DXR1

registers, respectively. The CPU can directly access these registers to move data from memory to these

registers. Interrupt signals will be based on these register pair contents and its related flags.

MRINT/MXINT will generate CPU interrupts for receive and transmit conditions.

Loading...

Loading...