www.ti.com

eCAP Registers

387

SPRUI07–March 2020

Submit Documentation Feedback

Copyright © 2020, Texas Instruments Incorporated

Enhanced Capture (eCAP)

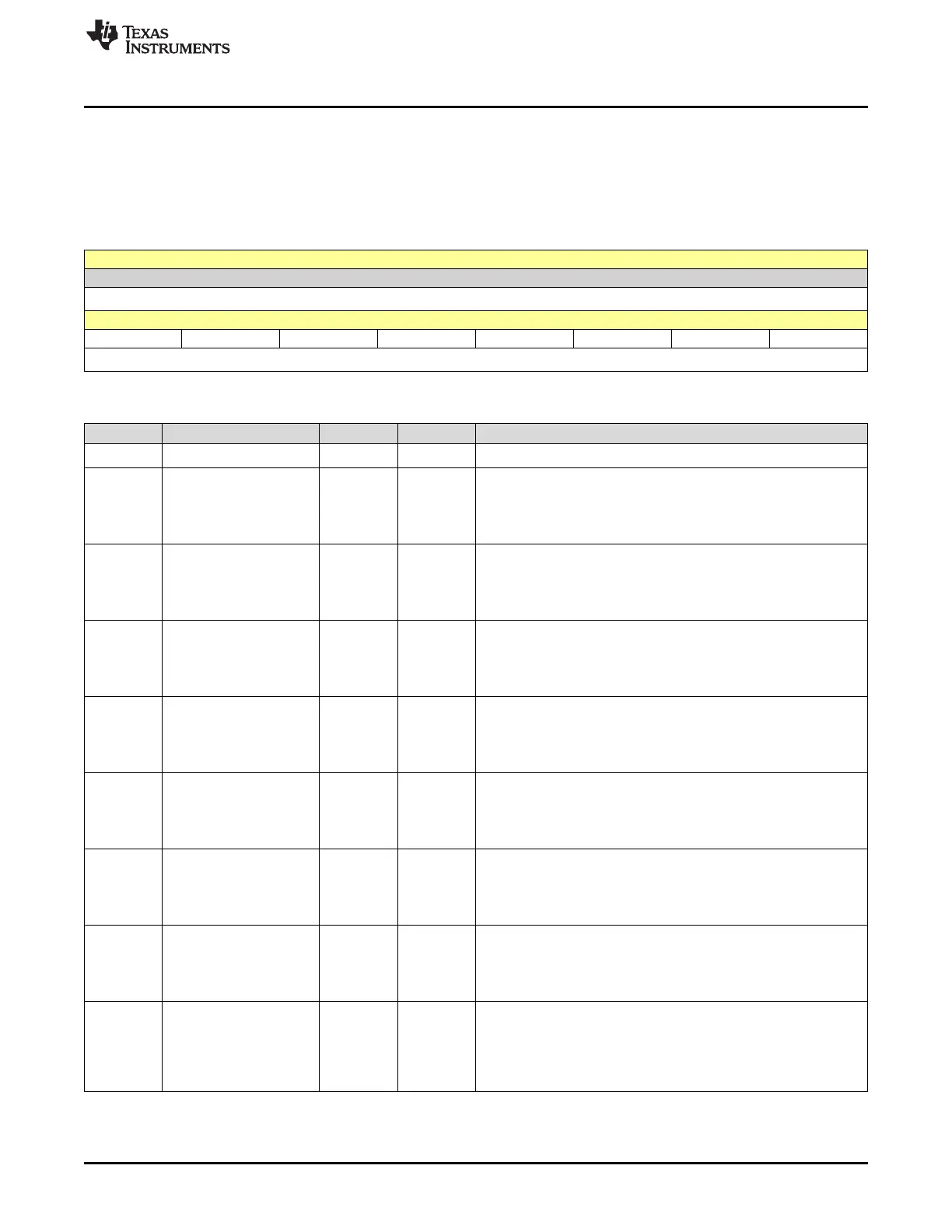

5.8.2.11 ECCLR Register (Offset = 18h) [reset = 0h]

ECCLR is shown in Figure 5-28 and described in Table 5-14.

Return to the Summary Table.

Capture Interrupt Clear Register

Figure 5-28. ECCLR Register

15 14 13 12 11 10 9 8

RESERVED

R-0h

7 6 5 4 3 2 1 0

CTR_CMP CTR_PRD CTROVF CEVT4 CEVT3 CEVT2 CEVT1 INT

R-0/W1C-0h R-0/W1C-0h R-0/W1C-0h R-0/W1C-0h R-0/W1C-0h R-0/W1C-0h R-0/W1C-0h R-0/W1C-0h

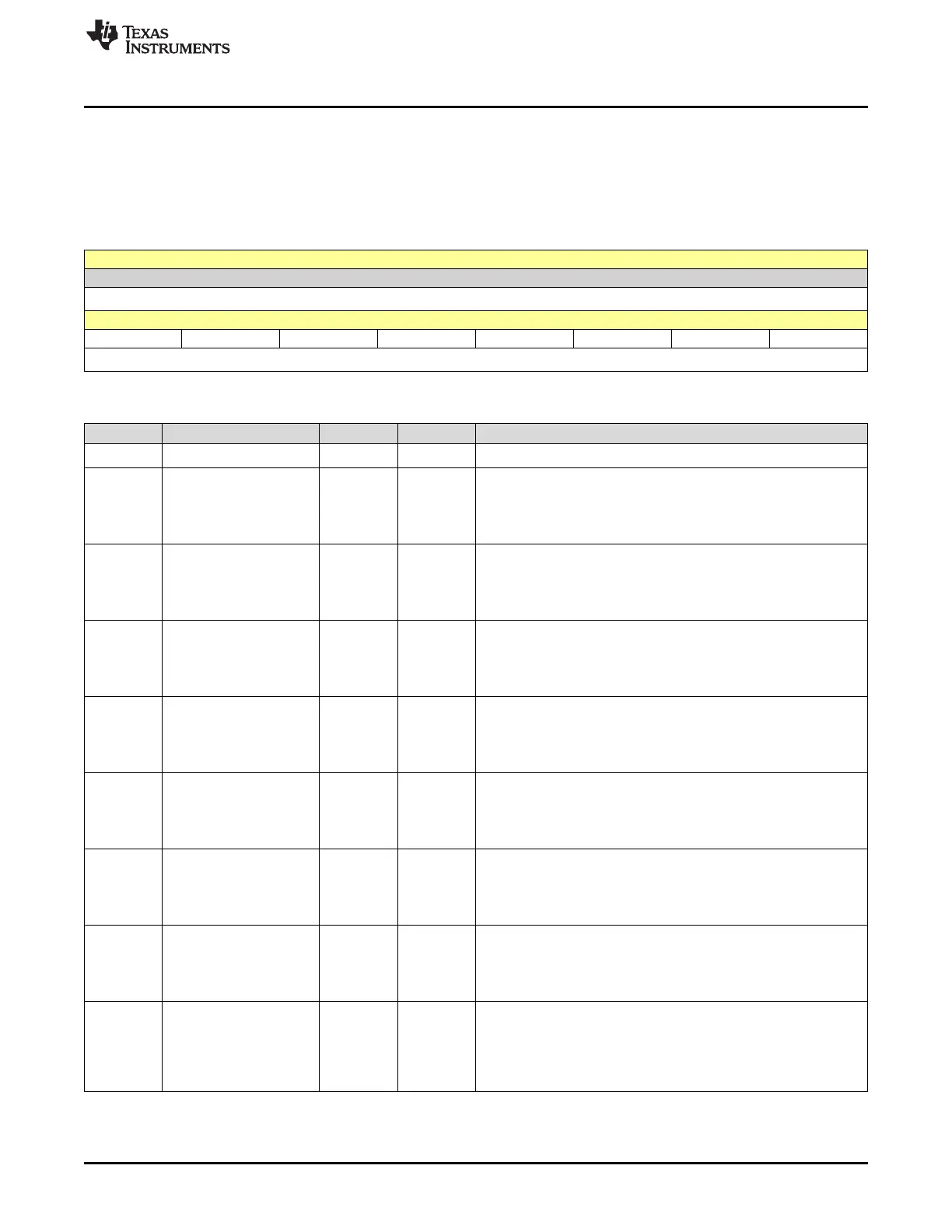

Table 5-14. ECCLR Register Field Descriptions

Bit Field Type Reset Description

15-8 RESERVED R 0h

Reserved

7 CTR_CMP R-0/W1C 0h

Counter Equal Compare Status Clear

Reset type: SYSRSn

0h (R/W) = Writing a 0 has no effect. Always reads back a 0

1h (R/W) = Writing a 1 clears the CTR=CMP flag.

6 CTR_PRD R-0/W1C 0h

Counter Equal Period Status Clear

Reset type: SYSRSn

0h (R/W) = Writing a 0 has no effect. Always reads back a 0

1h (R/W) = Writing a 1 clears the CTR=PRD flag.

5 CTROVF R-0/W1C 0h

Counter Overflow Status Clear

Reset type: SYSRSn

0h (R/W) = Writing a 0 has no effect. Always reads back a 0

1h (R/W) = Writing a 1 clears the CTROVF flag.

4 CEVT4 R-0/W1C 0h

Capture Event 4 Status Clear

Reset type: SYSRSn

0h (R/W) = Writing a 0 has no effect. Always reads back a 0

1h (R/W) = Writing a 1 clears the CEVT4 flag.

3 CEVT3 R-0/W1C 0h

Capture Event 3 Status Clear

Reset type: SYSRSn

0h (R/W) = Writing a 0 has no effect. Always reads back a 0

1h (R/W) = Writing a 1 clears the CEVT3 flag.

2 CEVT2 R-0/W1C 0h

Capture Event 2 Status Clear

Reset type: SYSRSn

0h (R/W) = Writing a 0 has no effect. Always reads back a 0

1h (R/W) = Writing a 1 clears the CEVT2 flag.

1 CEVT1 R-0/W1C 0h

Capture Event 1 Status Clear

Reset type: SYSRSn

0h (R/W) = Writing a 0 has no effect. Always reads back a 0

1h (R/W) = Writing a 1 clears the CEVT1 flag.

0 INT R-0/W1C 0h

ECAP Global Interrupt Status Clear

Reset type: SYSRSn

0h (R/W) = Writing a 0 has no effect. Always reads back a 0

1h (R/W) = Writing a 1 clears the INT flag and enable further

interrupts to be generated if any of the event flags are set to 1

Loading...

Loading...