Register Descriptions

www.ti.com

524

SPRUI07–March 2020

Submit Documentation Feedback

Copyright © 2020, Texas Instruments Incorporated

Direct Memory Access (DMA) Module

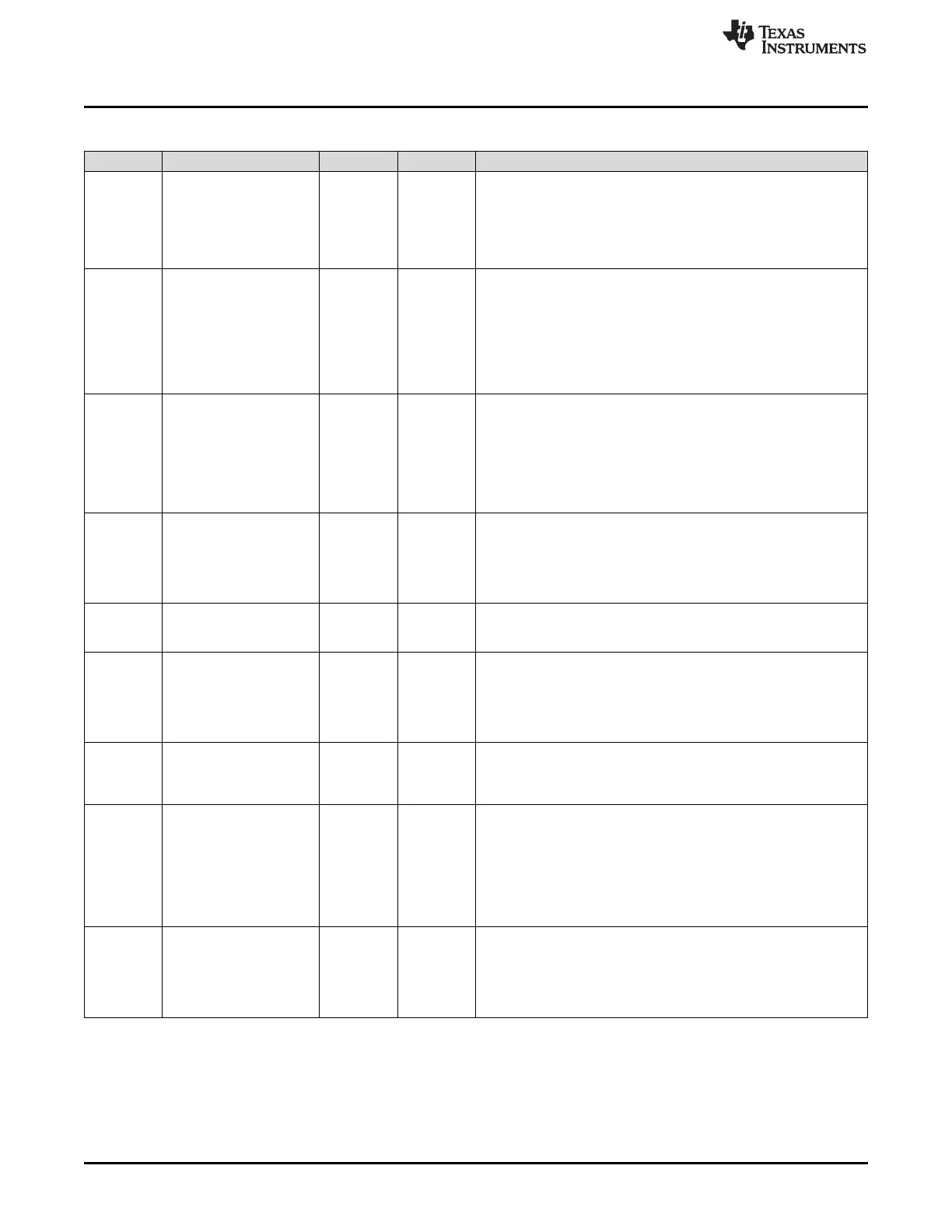

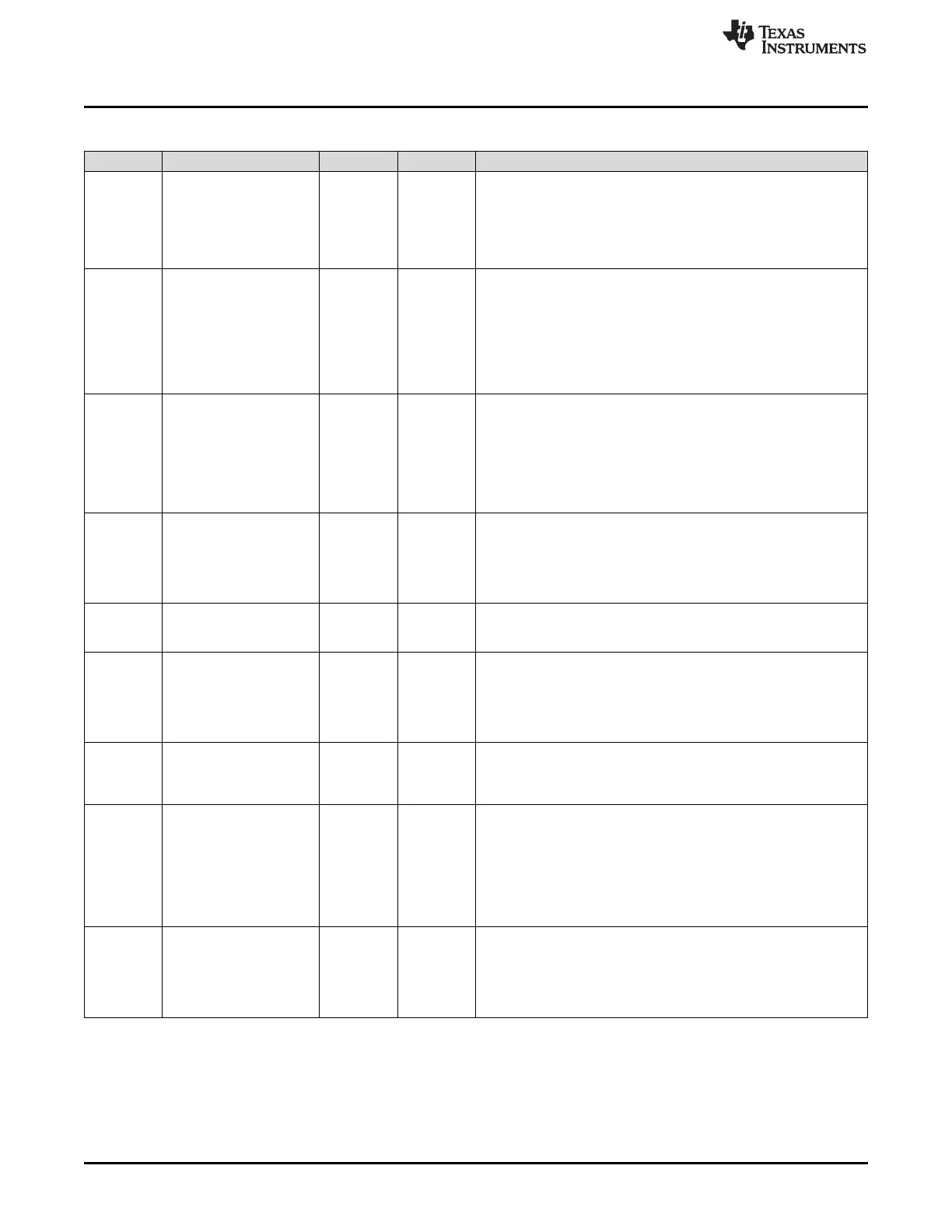

Table 8-10. CONTROL Register Field Descriptions (continued)

Bit Field Type Reset Description

9 SYNCFLG R 0h Sync Flag Bit: This bit indicates if an ADCSYNC event has occurred.

This flag is automatically cleared when the first burst transfer begins.

The SYNCFRC bit can be used to set the state of this bit to 1.

The SYNCCLR bit can be used to clear the state of this bit to 0.

0h = No sync event

1h = Sync event

8 PERINTFLG R 0h Peripheral Interrupt Trigger Flag Bit: This bit indicates if a peripheral

interrupt event trigger has occurred.

This flag is automatically cleared when the first burst transfer begins.

The PERINTFRC bit can be used to set the state of this bit to 1 and

force a software DMA event.

The PERINTCLR bit can be used to clear the state of this bit to 0.

0h = No interrupt event trigger

1h = Interrupt event trigger

7 ERRCLR RS 0h Error Clear Bit: Writing a 1 to this bit will clear any latched sync error

event and clear the SYNCERR bit.

This bit will also clear the OVRFLG bit.

This bit would normally be used when initializing the DMA for the first

time or if an overflow condition is detected.

If an ADCSYNC error event or overflow event occurs at the same

time as writing to this bit, the ADC or overrun has priority and the

SYNCERR or OVRFLG bit is set.

6 SYNCCLR RS 0h Sync Clear Bit: Writing a 1 to this bit will clear a latched sync event

and clear the SYNCFLG bit.

This bit would normally be used when initializing the DMA for the first

time.

If an ADCSYNC event occurs at the same time as writing to this bit,

the ADC has priority and the SYNCFLG bit is set.

5 SYNCFRC RS 0h Sync Force Bit: Writing a 1 to this bit latches a sync event and sets

the SYNCFLG bit.

This bit can be used like a software sync for the wrap counter.

4 PERINTCLR RS 0h Peripheral Interrupt Clear Bit: Writing a 1 to this bit clears any

latched peripheral interrupt event and clears the PERINTFLG bit.

This bit would normally be used when initializing the DMA for the first

time.

If a peripheral event occurs at the same time as writing to this bit,

the peripheral has priority and the PERINTFLG bit is set.

3 PERINTFRC RS 0h Peripheral Interrupt Force Bit: Writing a 1 to this bit latches a

peripheral interrupt event trigger and sets the PERINTFLG bit.

If the PERINTE bit is set, this bit can be used like a software force

for a DMA burst transfer.

2 SOFTRESET RS 0h

Channel Soft Reset Bit: Writing a 1 to this bit completes current

read-write access and places the channel into a default state as

follows: RUNSTS = 0 TRANSFERSTS = 0 BURSTSTS = 0

BURST_COUNT = 0 TRANSFER_COUNT = 0

SRC_WRAP_COUNT = 0 DST_WRAP_COUNT = 0 This is a soft

reset that basically allows the DMA to complete the current read-

write access and then places the DMA channel into the default reset

state.

1 HALT RS 0h Channel Halt Bit: Writing a 1 to this bit halts the DMA at the current

state and any current read-write access is completed.

See Figure 8-5 for the various positions the state machine can be at

when HALTED.

The RUNSTS bit is set to 0.

To take the device out of HALT, the RUN bit needs to be activated.

Loading...

Loading...