Peripheral Interrupt Expansion (PIE)

www.ti.com

160

SPRUI07–March 2020

Submit Documentation Feedback

Copyright © 2020, Texas Instruments Incorporated

System Control and Interrupts

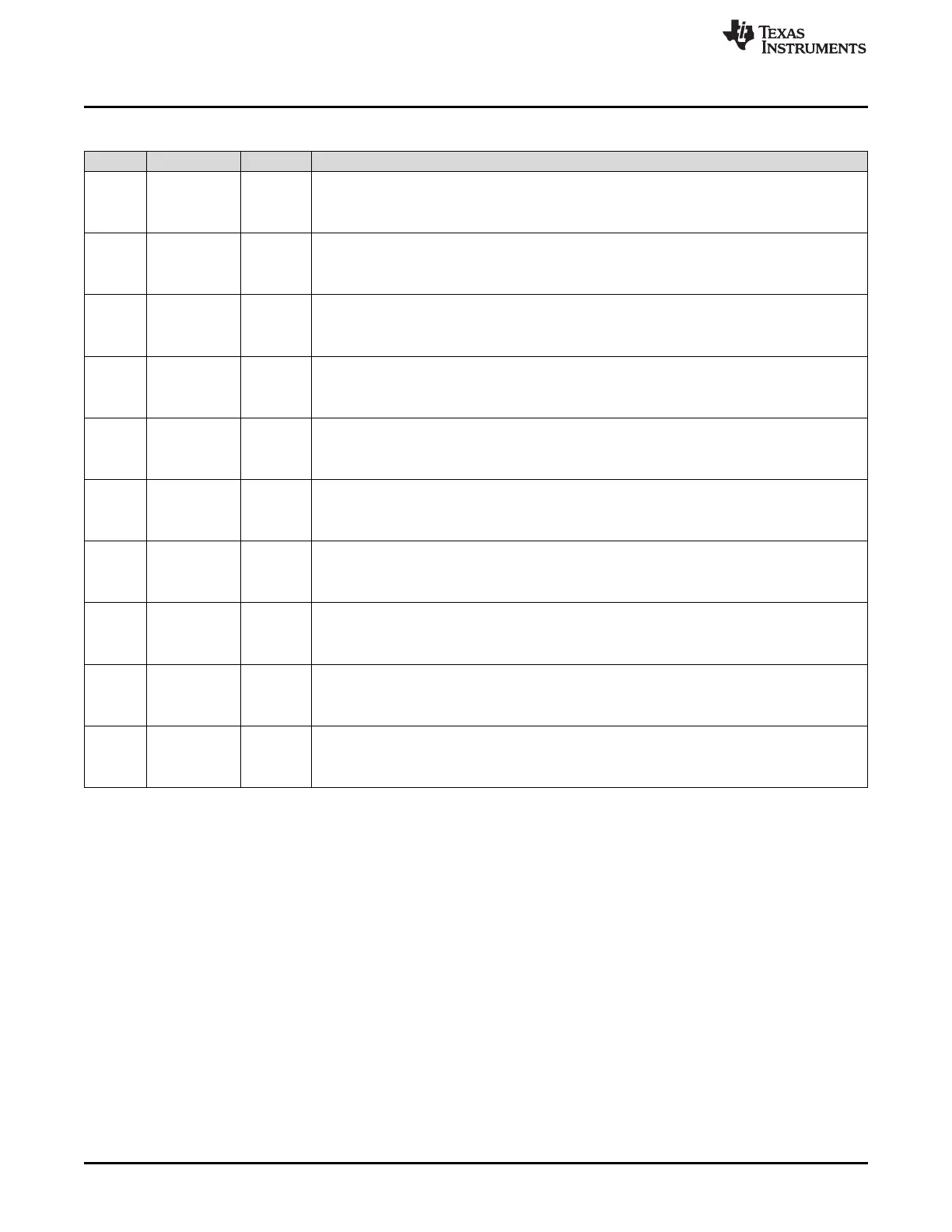

Table 1-119. Interrupt Enable Register (IER) — CPU Register Field Descriptions (continued)

Bits Field Value Description

9 INT10 Interrupt 10 enable. INT10 enables or disables CPU interrupt level INT10.

0 Level INT10 is disabled

1 Level INT10 is enabled

8 INT9 Interrupt 9 enable. INT9 enables or disables CPU interrupt level INT9.

0 Level INT9 is disabled

1 Level INT9 is enabled

7 INT8 Interrupt 8 enable. INT8 enables or disables CPU interrupt level INT8.

0 Level INT8 is disabled

1 Level INT8 is enabled

6 INT7 Interrupt 7 enable. INT7 enables or disables CPU interrupt level INT7.

0 Level INT7 is disabled

1 Level INT7 is enabled

5 INT6 Interrupt 6 enable. INT6 enables or disables CPU interrupt level INT6.

0 Level INT6 is disabled

1 Level INT6 is enabled

4 INT5 Interrupt 5 enable.INT5 enables or disables CPU interrupt level INT5.

0 Level INT5 is disabled

1 Level INT5 is enabled

3 INT4 Interrupt 4 enable.INT4 enables or disables CPU interrupt level INT4.

0 Level INT4 is disabled

1 Level INT4 is enabled

2 INT3 Interrupt 3 enable.INT3 enables or disables CPU interrupt level INT3.

0 Level INT3 is disabled

1 Level INT3 is enabled

1 INT2 Interrupt 2 enable.INT2 enables or disables CPU interrupt level INT2.

0 Level INT2 is disabled

1 Level INT2 is enabled

0 INT1 Interrupt 1 enable.INT1 enables or disables CPU interrupt level INT1.

0 Level INT1 is disabled

1 Level INT1 is enabled

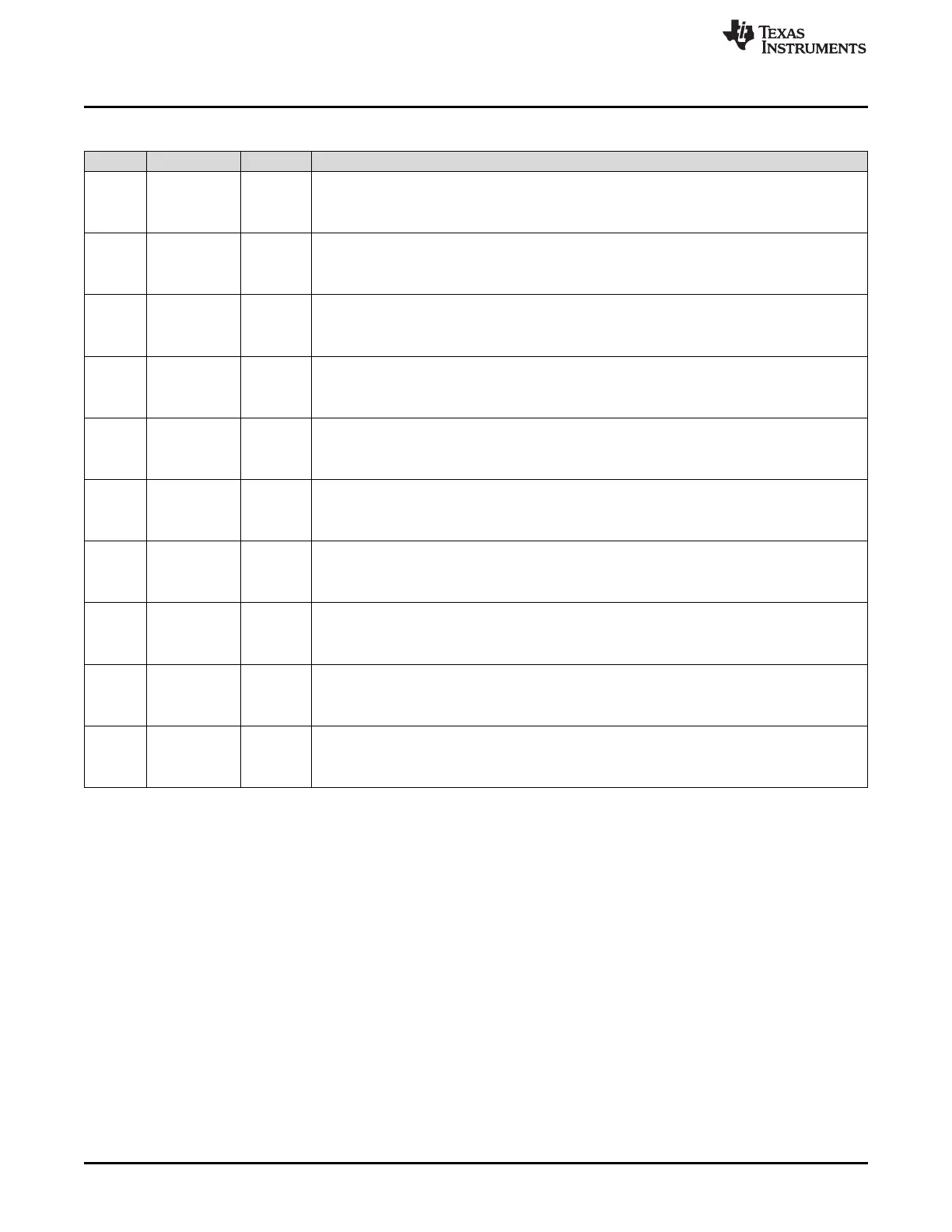

1.6.4.7 Debug Interrupt Enable Register (DBGIER) — CPU Register

The Debug Interrupt Enable Register (DBGIER) is used only when the CPU is halted in real-time

emulation mode. An interrupt enabled in the DBGIER is defined as a time-critical interrupt. When the CPU

is halted in real-time mode, the only interrupts that are serviced are time-critical interrupts that are also

enabled in the IER. If the CPU is running in real-time emulation mode, the standard interrupt-handling

process is used and the DBGIER is ignored.

As with the IER, you can read the DBGIER to identify enabled or disabled interrupts and write to the

DBGIER to enable or disable interrupts. To enable an interrupt, set its corresponding bit to 1. To disable

an interrupt, set its corresponding bit to 0. Use the PUSH DBGIER instruction to read from the DBGIER

and POP DBGIER to write to the DBGIER register. At reset, all the DBGIER bits are set to 0.

Loading...

Loading...