Registers

www.ti.com

298

SPRUI07–March 2020

Submit Documentation Feedback

Copyright © 2020, Texas Instruments Incorporated

Enhanced Pulse Width Modulator (ePWM) Module

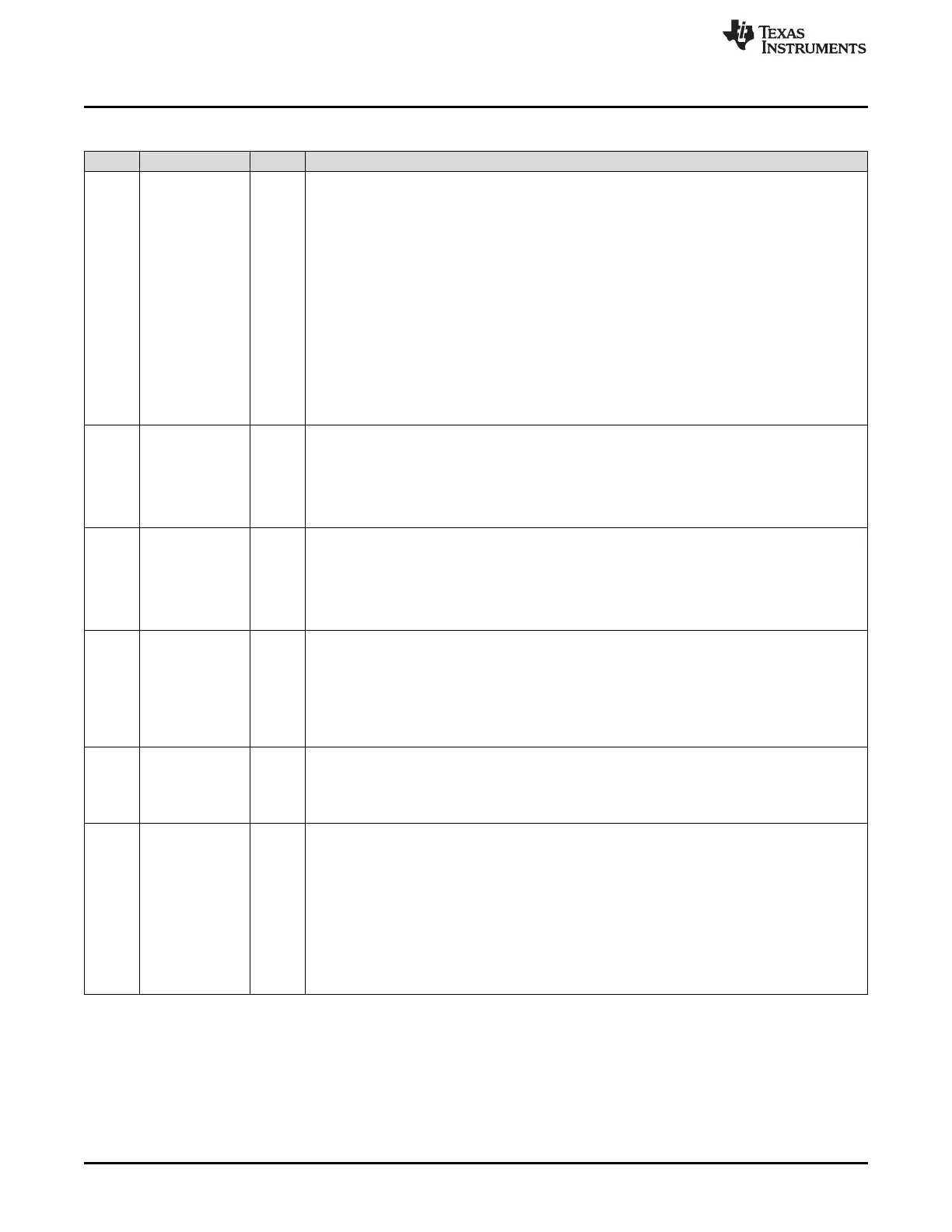

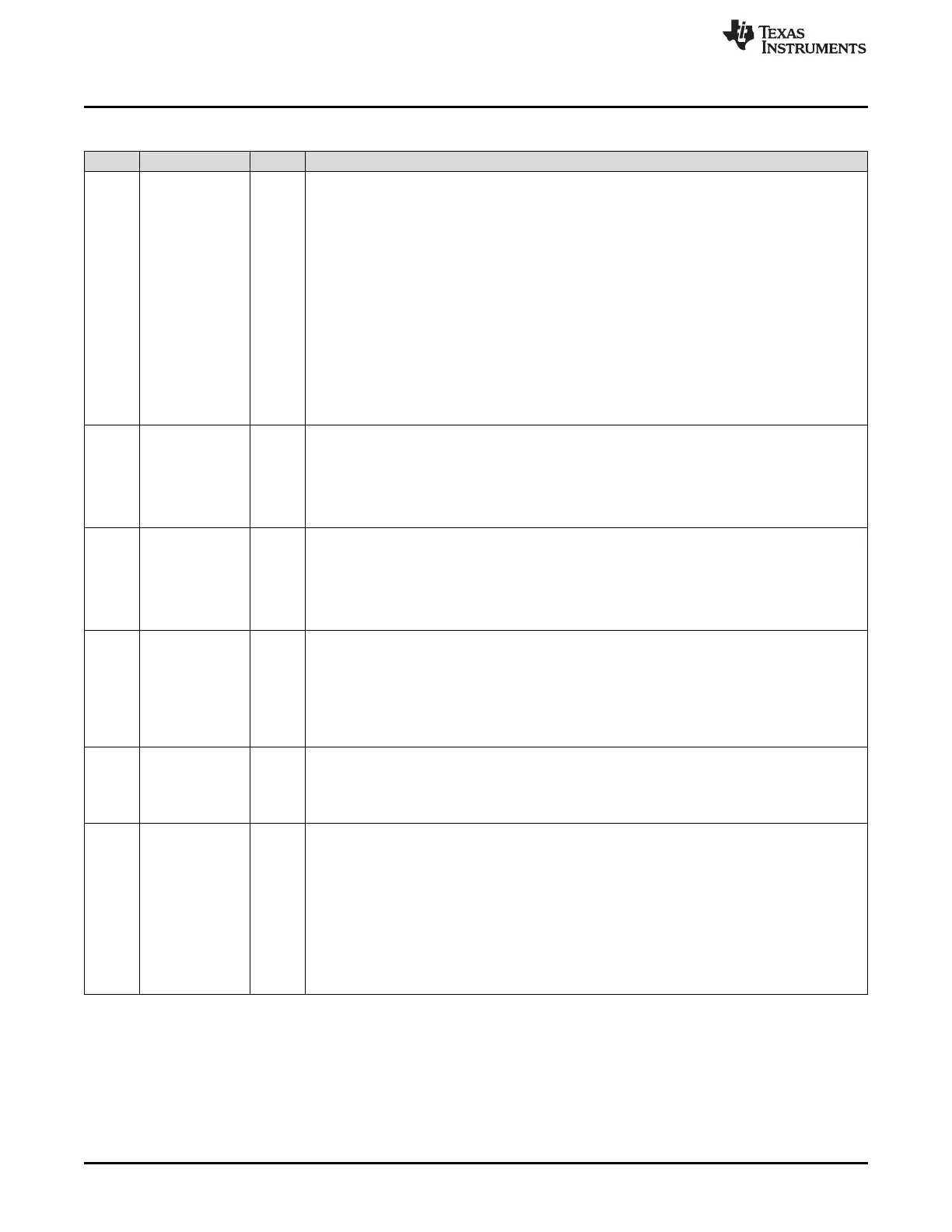

Table 3-24. Time-Base Control Register (TBCTL) Field Descriptions (continued)

Bit Field Value Description

9:7 HSPCLKDIV High Speed Time-base Clock Prescale Bits

These bits determine part of the time-base clock prescale value.

TBCLK = SYSCLKOUT / (HSPCLKDIV × CLKDIV)

This divisor emulates the HSPCLK in the TMS320x281x system as used on the Event Manager

(EV) peripheral.

000 /1

001 /2 (default on reset)

010 /4

011 /6

100 /8

101 /10

110 /12

111 /14

6 SWFSYNC Software Forced Synchronization Pulse

0 Writing a 0 has no effect and reads always return a 0.

1 Writing a 1 forces a one-time synchronization pulse to be generated.

This event is ORed with the EPWMxSYNCI input of the ePWM module.

SWFSYNC is valid (operates) only when EPWMxSYNCI is selected by SYNCOSEL = 00.

5:4 SYNCOSEL Synchronization Output Select. These bits select the source of the EPWMxSYNCO signal.

00 EPWMxSYNC:

01 CTR = zero: Time-base counter equal to zero (TBCTR = 0x0000)

10 CTR = CMPB : Time-base counter equal to counter-compare B (TBCTR = CMPB)

11 Disable EPWMxSYNCO signal

3 PRDLD Active Period Register Load From Shadow Register Select

0 The period register (TBPRD) is loaded from its shadow register when the time-base counter,

TBCTR, is equal to zero.

A write or read to the TBPRD register accesses the shadow register.

1 Load the TBPRD register immediately without using a shadow register.

A write or read to the TBPRD register directly accesses the active register.

2 PHSEN Counter Register Load From Phase Register Enable

0 Do not load the time-base counter (TBCTR) from the time-base phase register (TBPHS)

1 Load the time-base counter with the phase register when an EPWMxSYNCI input signal occurs or

when a software synchronization is forced by the SWFSYNC bit

1:0 CTRMODE Counter Mode

The time-base counter mode is normally configured once and not changed during normal operation.

If you change the mode of the counter, the change will take effect at the next TBCLK edge and the

current counter value shall increment or decrement from the value before the mode change.

These bits set the time-base counter mode of operation as follows:

00 Up-count mode

01 Down-count mode

10 Up-down-count mode

11 Stop-freeze counter operation (default on reset)

Loading...

Loading...