www.ti.com

eQEP Registers

427

SPRUI07–March 2020

Submit Documentation Feedback

Copyright © 2020, Texas Instruments Incorporated

Enhanced Quadrature Encoder Pulse (eQEP)

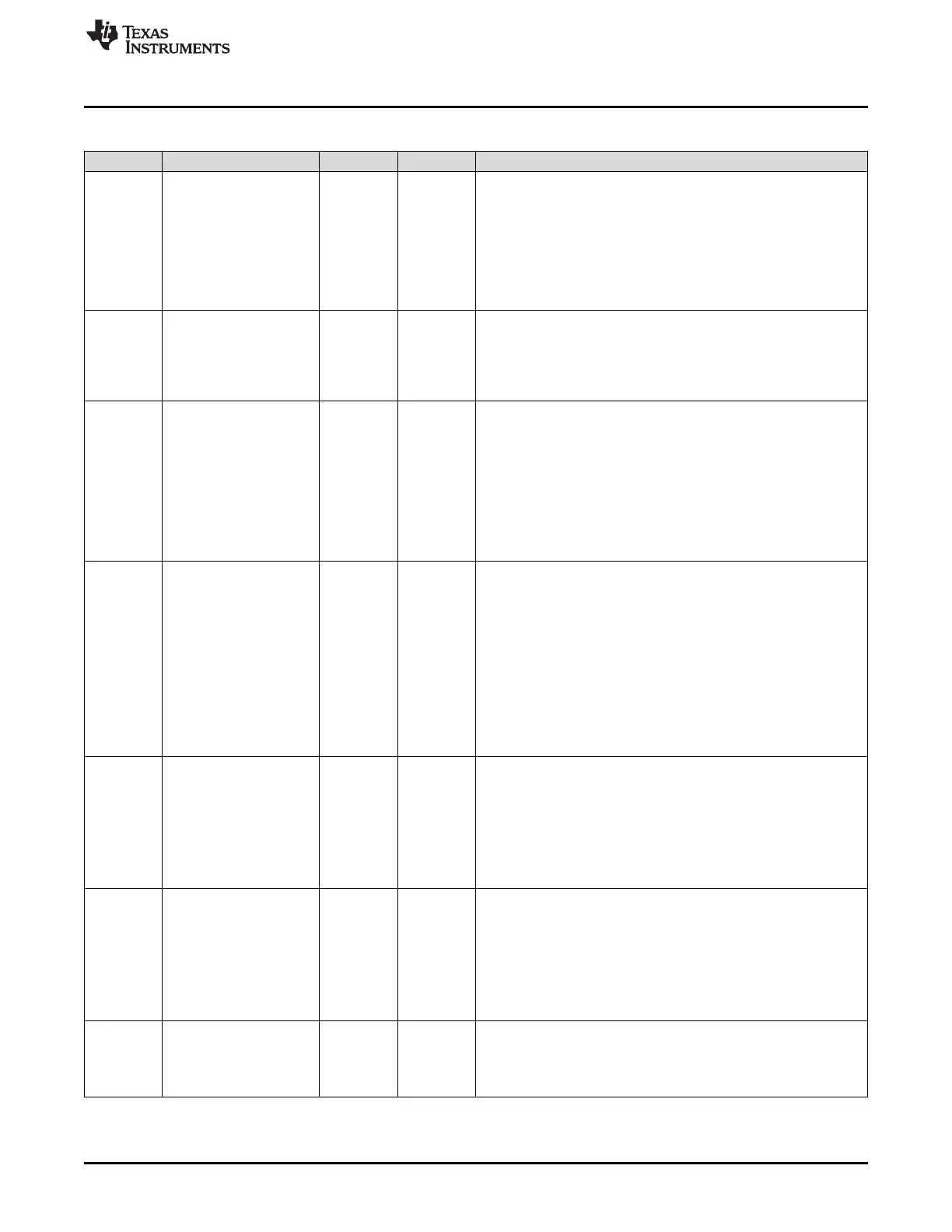

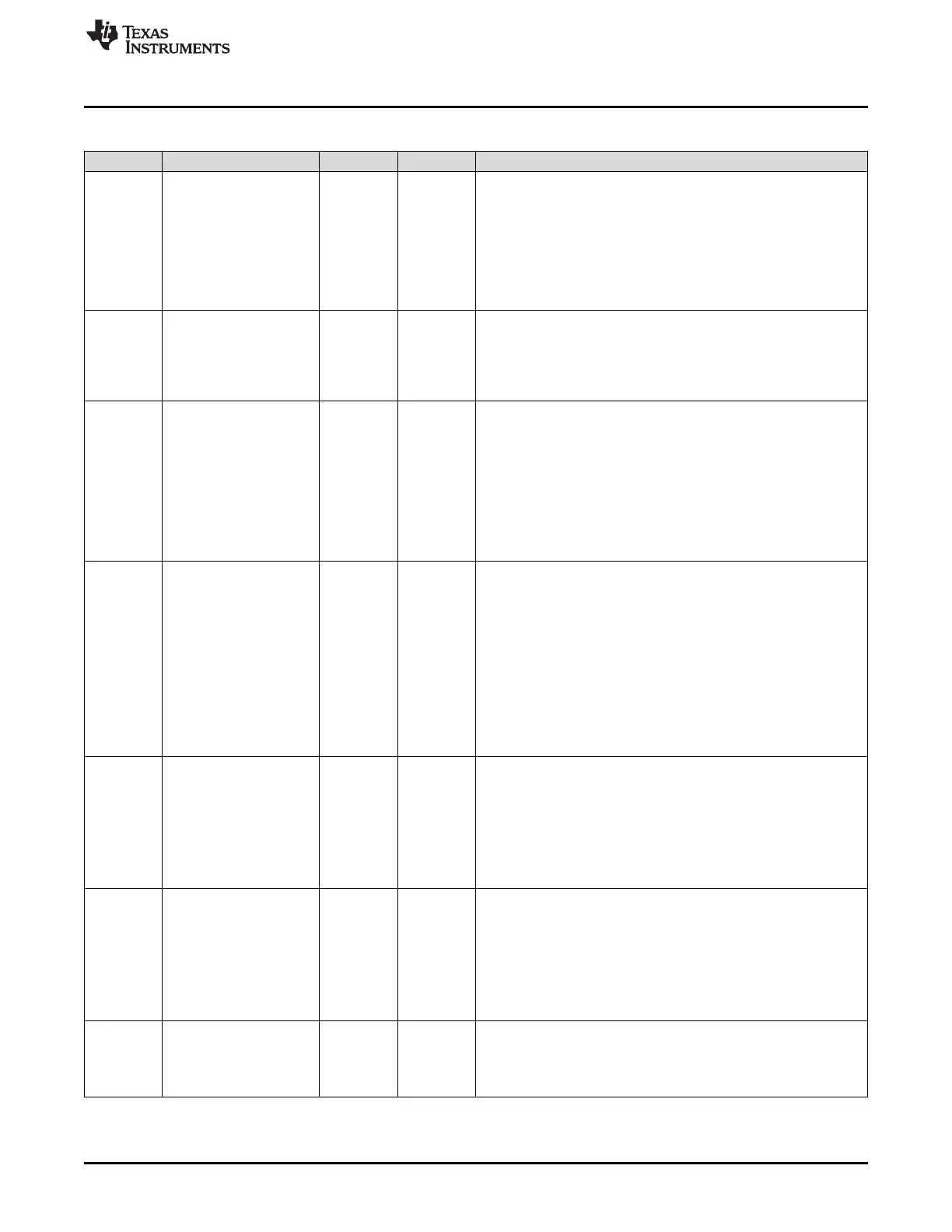

Table 6-18. QEPCTL Register Field Descriptions (continued)

Bit Field Type Reset Description

9-8 IEI R/W 0h

Index event init of position count

Reset type: SYSRSn

0h (R/W) = Do nothing (action disabled)

1h (R/W) = Do nothing (action disabled)

2h (R/W) = Initializes the position counter on the rising edge of the

QEPI signal (QPOSCNT = QPOSINIT)

3h (R/W) = Initializes the position counter on the falling edge of

QEPI signal (QPOSCNT = QPOSINIT)

7 SWI R/W 0h

Software init position counter

Reset type: SYSRSn

0h (R/W) = Do nothing (action disabled)

1h (R/W) = Initialize position counter (QPOSCNT=QPOSINIT). This

bit is not cleared automatically

6 SEL R/W 0h

Strobe event latch of position counter

Reset type: SYSRSn

0h (R/W) = The position counter is latched on the rising edge of

QEPS strobe (QPOSSLAT = POSCCNT). Latching on the falling

edge can be done by inverting the strobe input using the QSP bit in

the QDECCTL register

1h (R/W) = Clockwise Direction:

Position counter is latched on rising edge of QEPS strobe

Counter Clockwise Direction:

Position counter is latched on falling edge of QEPS strobe

5-4 IEL R/W 0h

Index event latch of position counter (software index marker)

Reset type: SYSRSn

0h (R/W) = Reserved

1h (R/W) = Latches position counter on rising edge of the index

signal

2h (R/W) = Latches position counter on falling edge of the index

signal

3h (R/W) = Software index marker. Latches the position counter

and quadrature direction flag on index event marker. The position

counter is latched to the QPOSILAT register and the direction flag

is latched in the QEPSTS[QDLF] bit. This mode is useful for

software index marking.

3 QPEN R/W 0h

Quadrature position counter enable/software reset

Reset type: SYSRSn

0h (R/W) = Reset the eQEP peripheral internal operating

flags/read-only registers. Control/configuration registers are not

disturbed by a software reset.

When QPEN is disabled, some flags in the QFLG register do not

get reset or cleared and show the actual state of that flag.

1h (R/W) = eQEP position counter is enabled

2 QCLM R/W 0h

QEP capture latch mode

Reset type: SYSRSn

0h (R/W) = Latch on position counter read by CPU. Capture timer

and capture period values are latched into QCTMRLAT and

QCPRDLAT registers when CPU reads the QPOSCNT register.

1h (R/W) = Latch on unit time out. Position counter, capture timer

and capture period values are latched into QPOSLAT, QCTMRLAT

and QCPRDLAT registers on unit time out.

1 UTE R/W 0h

QEP unit timer enable

Reset type: SYSRSn

0h (R/W) = Disable eQEP unit timer

1h (R/W) = Enable unit timer

Loading...

Loading...