General-Purpose Input/Output (GPIO)

www.ti.com

102

SPRUI07–March 2020

Submit Documentation Feedback

Copyright © 2020, Texas Instruments Incorporated

System Control and Interrupts

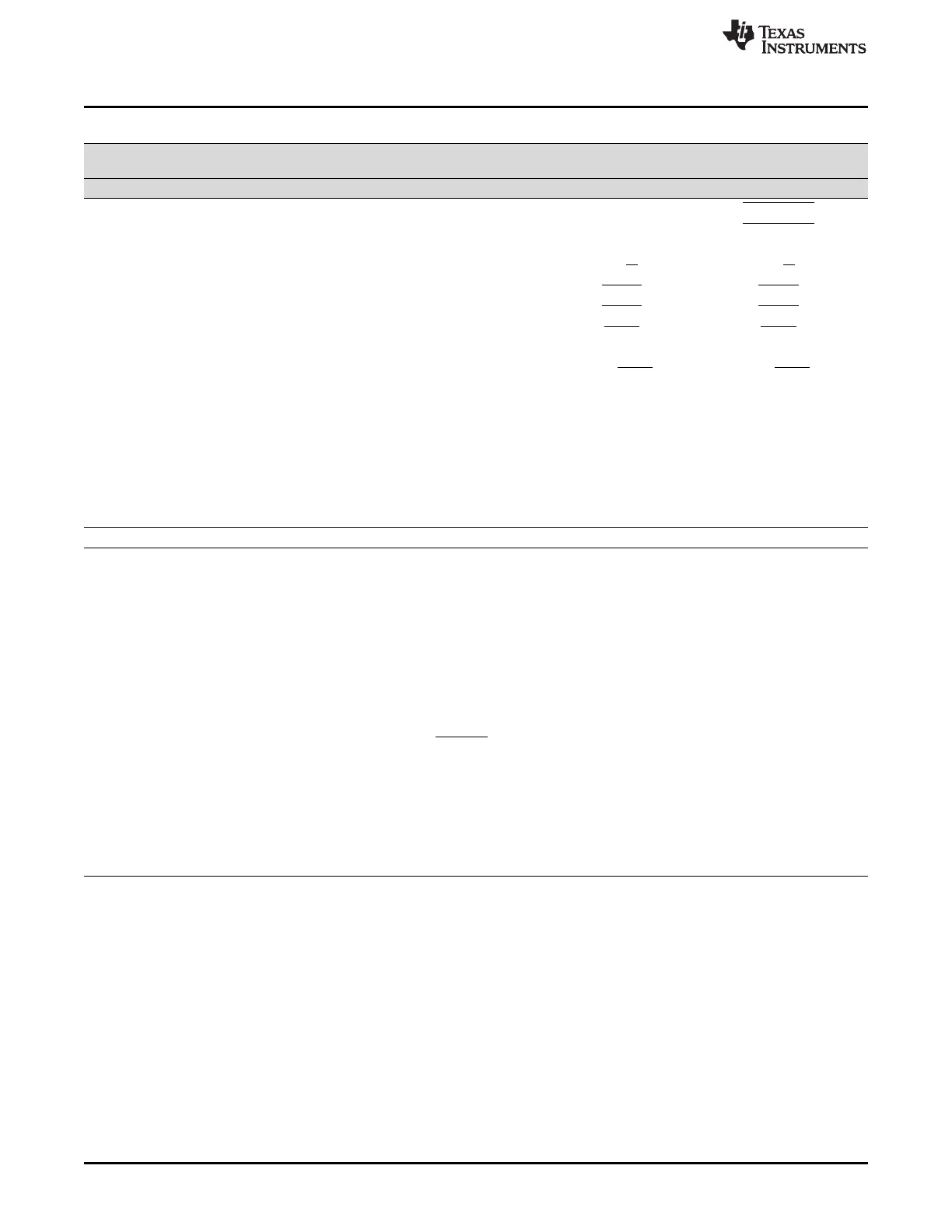

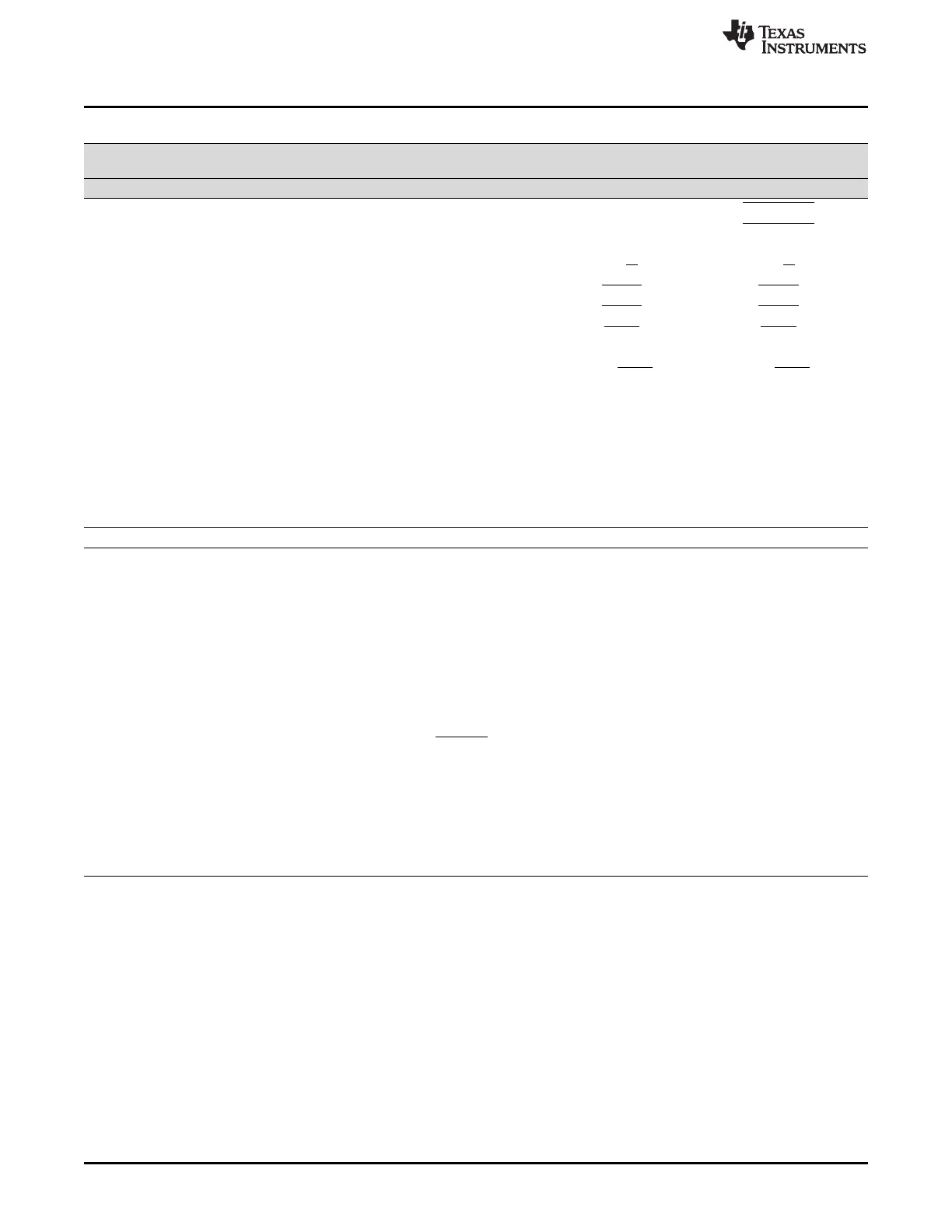

Table 1-48. GPIOB MUX

Default at Reset

Primary I/O Function Peripheral Selection 1 Peripheral Selection 2 Peripheral Selection 3

GPBMUX1 Register Bits (GPBMUX1 bits = 00) (GPBMUX1 bits = 01) (GPBMUX1 bits = 10) (GPBMUX1 bits = 11)

1,0 GPIO32 (I/O) SDAA (I/OC) EPWMSYNCI (I) ADCSOCAO (O)

3,2 GPIO33 (I/O) SCLA (I/OC) EPWMSYNCO (O) ADCSOCBO (O)

5,4 GPIO34 (I/O) ECAP1 (I/O) XREADY (I) XREADY (I)

7,6 GPIO35 (I/O) SCITXDA (O) XR/W (O) XR/W (O)

9,8 GPIO36 (I/O) SCIRXDA (I) XZCS0 (O) XZCS0 (O)

11,10 GPIO37 (I/O) ECAP2 (I/O) XZCS7 (O) XZCS7 (O)

13,12 GPIO38 (I/O) Reserved XWE0 (O) XWE0 (O)

15,14 GPIO39 (I/O) Reserved XA16 (O) XA16 (O)

17,16 GPIO40 (I/O) Reserved XA0/XWE1 (O) XA0/XWE1 (O)

19,18 GPIO41 (I/O) Reserved XA1 (O) XA1 (O)

21,20 GPIO42 (I/O) Reserved XA2 (O) XA2 (O)

23,22 GPIO43 (I/O) Reserved XA3 (O) XA3 (O)

25,24 GPIO44 (I/O) Reserved XA4 (O) XA4 (O)

27,26 GPIO45 (I/O) Reserved XA5 (O) XA5 (O)

29,28 GPIO46 (I/O) Reserved XA6 (O) XA6 (O)

31,30 GPIO47 (I/O) Reserved XA7 (O) XA7 (O)

GPBMUX2 Register Bits (GPBMUX2 bits = 00) (GPBMUX2 bits = 01) (GPBMUX2 bits = 10 or 11)

1,0 GPIO48 (I/O) ECAP5 (I/O) XD31 (I/O)

3,2 GPIO49 (I/O) ECAP6 (I/O) XD30 (I/O)

5,4 GPIO50 (I/O) EQEP1A (I) XD29 (I/O)

7,6 GPIO51 (I/O) EQEP1B (I) XD28 (I/O)

9,8 GPIO52 (I/O) EQEP1S (I/O) XD27 (I/O)

11,10 GPIO53 (I/O) EQEP1I (I/O) XD26 (I/O)

13,12 GPIO54 (I/O) SPISIMOA (I/O) XD25 (I/O)

15,14 GPIO55 (I/O) SPISOMIA (I/O) XD24 (I/O)

17,16 GPIO56 (I/O) SPICLKA (I/O) XD23 (I/O)

19,18 GPIO57 (I/O) SPISTEA (I/O) XD22 (I/O)

21,20 GPIO58 (I/O) MCLKRA (I/O) XD21 (I/O)

23,22 GPIO59 (I/O) MFSRA (I/O) XD20 (I/O)

25,24 GPIO60 (I/O) MCLKRB (I/O) XD19 (I/O)

27,26 GPIO61 (I/O) MFSRB (I/O) XD18 (I/O)

29,28 GPIO62 (I/O) SCIRXDC (I) XD17 (I/O)

31,30 GPIO63 (I/O) SCITXDC (O) XD16 (I/O)

Loading...

Loading...