www.ti.com

ADC Registers

481

SPRUI07–March 2020

Submit Documentation Feedback

Copyright © 2020, Texas Instruments Incorporated

Analog-to-Digital Converter (ADC)

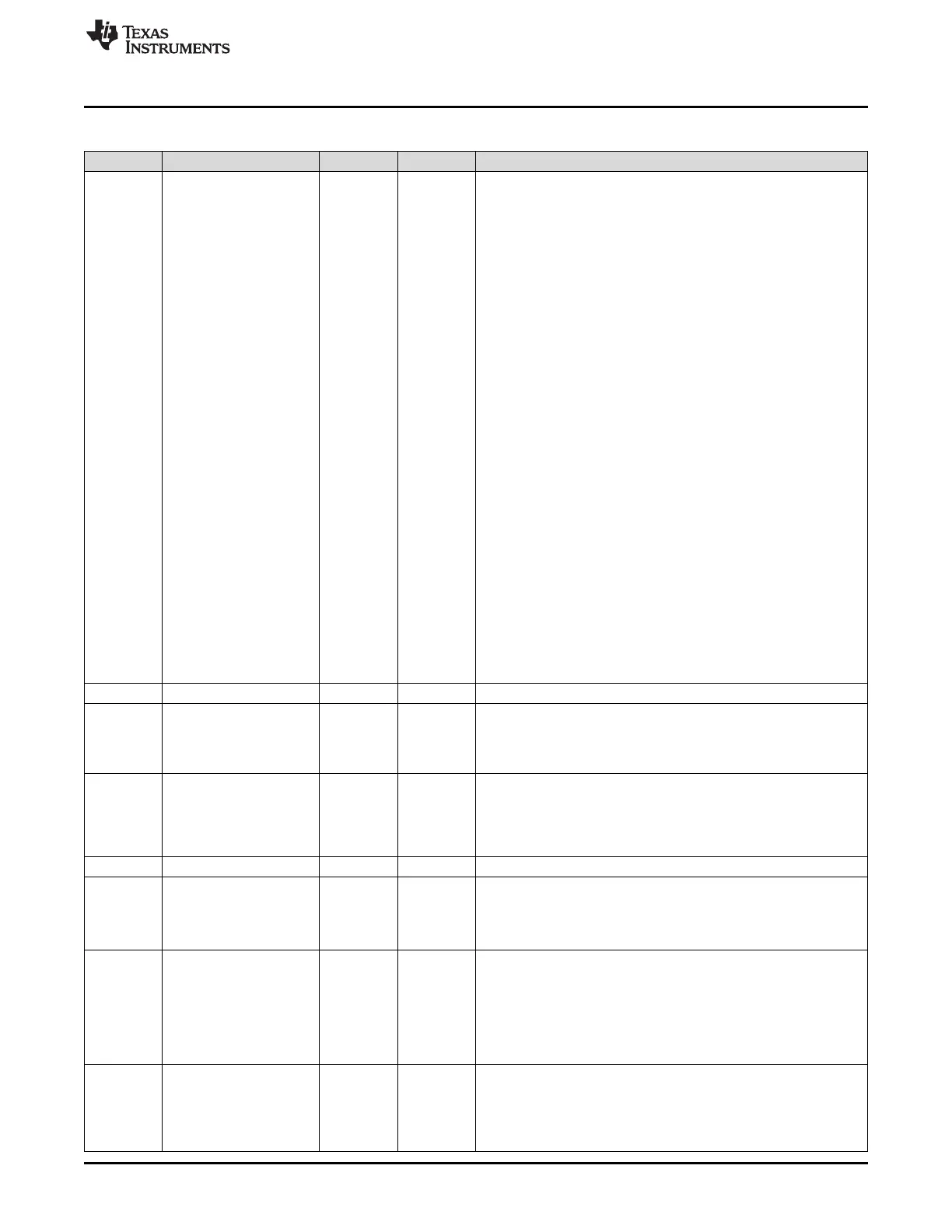

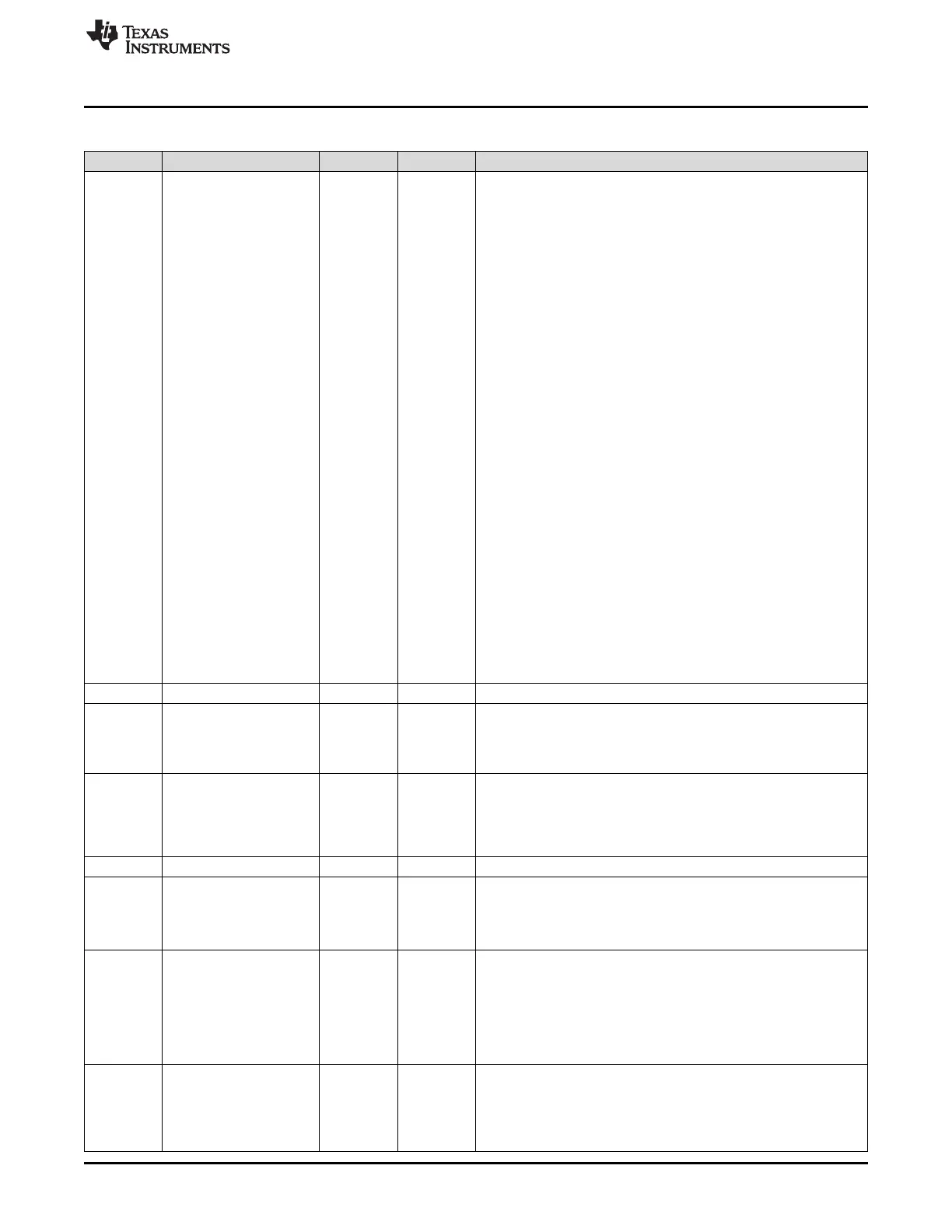

Table 7-11. ADCTRL2 Register Field Descriptions (continued)

Bit Field Type Reset Description

13 SOC_SEQ1 R/W 0h

Start-of-conversion (SOC) trigger for Sequencer 1 (SEQ1) or the

cascaded sequencer. This bit can be set by the following triggers:

• S/W - Software writing a 1 to this bit

• ePWM SOCA

• ePWM SOCB (only in cascaded mode)

• EXT - External pin (i.e., GPIO Port A pin (GPIO31-0) configured

as XINT2 in the GPIOxINT2SEL register.

See the TMS320x2833x System Control and Interrupts Reference

Guide (literature number SPRUFB0) for details on how to configure a

GPIO pin as XINT2. When a trigger occurs, there are three

possibilities:

Case 1: SEQ1 idle and SOC bit clear SEQ1 starts immediately

(under arbiter control). This bit is set and cleared, allowing for any

"pending" trigger requests.

Case 2: SEQ1 busy and SOC bit clear Bit is set signifying a trigger

request is pending. When SEQ1 finally starts after completing

current conversion, this bit is cleared.

Case 3: SEQ1 busy and SOC bit set Any trigger occurring in this

case is ignored (lost).

0h = Clears a pending SOC trigger. Note: If the sequencer has

already started, this bit is automatically cleared, and hence, writing a

zero has no effect; i.e., an already started sequencer cannot be

stopped by clearing this bit.

1h = Software trigger - Start SEQ1 from currently stopped position

(i.e., Idle mode)

Note: The RST_SEQ1 (ADCTRL2.14) and the SOC_SEQ1

(ADCTRL2.13) bits should not be set in the same instruction. This

resets the sequencer, but does not start the sequence. The correct

sequence of operation is to set the RST_SEQ1 bit first, and the

SOC_SEQ1 bit in the following instruction. This makes certain that

the sequencer is reset and a new sequence started. This sequence

applies to the RST_SEQ2 (ADCTRL2.6) and SOC_SEQ2

(ADCTRL2.5) bits also.

12 RESERVED R 0h Reads return a zero. Writes have no effect.

11 INT_ENA_SEQ1 R/W 0h SEQ1 interrupt enable. This bit enables the interrupt request to CPU

by INT SEQ1.

0h = Interrupt request by INT_SEQ1 is disabled.

1h = Interrupt request by INT_SEQ1 is enabled.

10 INT_MOD_SEQ1 R/W 0h SEQ1 interrupt mode. This bit selects SEQ1 interrupt mode. It

affects the setting of INT SEQ1 at the end of the SEQ1 conversion

sequence.

0h = INT_SEQ1 is set at the end of every SEQ1 sequence.

1h = INT_SEQ1 is set at the end of every other SEQ1 sequence.

9 RESERVED R 0h Reads return a zero. Writes have no effect.

8 ePWM_SOCA_SEQ1 R/W 0h

ePWM SOCA enable bit for SEQ1

0h = SEQ1 cannot be started by ePWMx SOCA trigger.

1h = Allows SEQ1/SEQ to be started by ePWMx SOCA trigger. The

ePWMs can be programmed to start a conversion on various events.

7 EXT_SOC_SEQ1 R/W 0h

External signal start-of-conversion bit for SEQ1

0h = No action

1h = Setting this bit enables an ADC autoconversion sequence to be

started by a signal from a GPIO Port A pin (GPIO31-0) configured as

XINT2 in the GPIOXINT2SEL register. See the TMS320x2833x

System Control and Interrupts Reference Guide (literature number

SPRUFB0)

6 RST_SEQ2 R/W 0h

Reset SEQ2

0h = No action

1h = Immediately resets SEQ2 to an initial "pretriggered" state, i.e.,

waiting for a trigger at CONV08. A currently active conversion

sequence will be aborted.

Loading...

Loading...