ADC Registers

www.ti.com

482

SPRUI07–March 2020

Submit Documentation Feedback

Copyright © 2020, Texas Instruments Incorporated

Analog-to-Digital Converter (ADC)

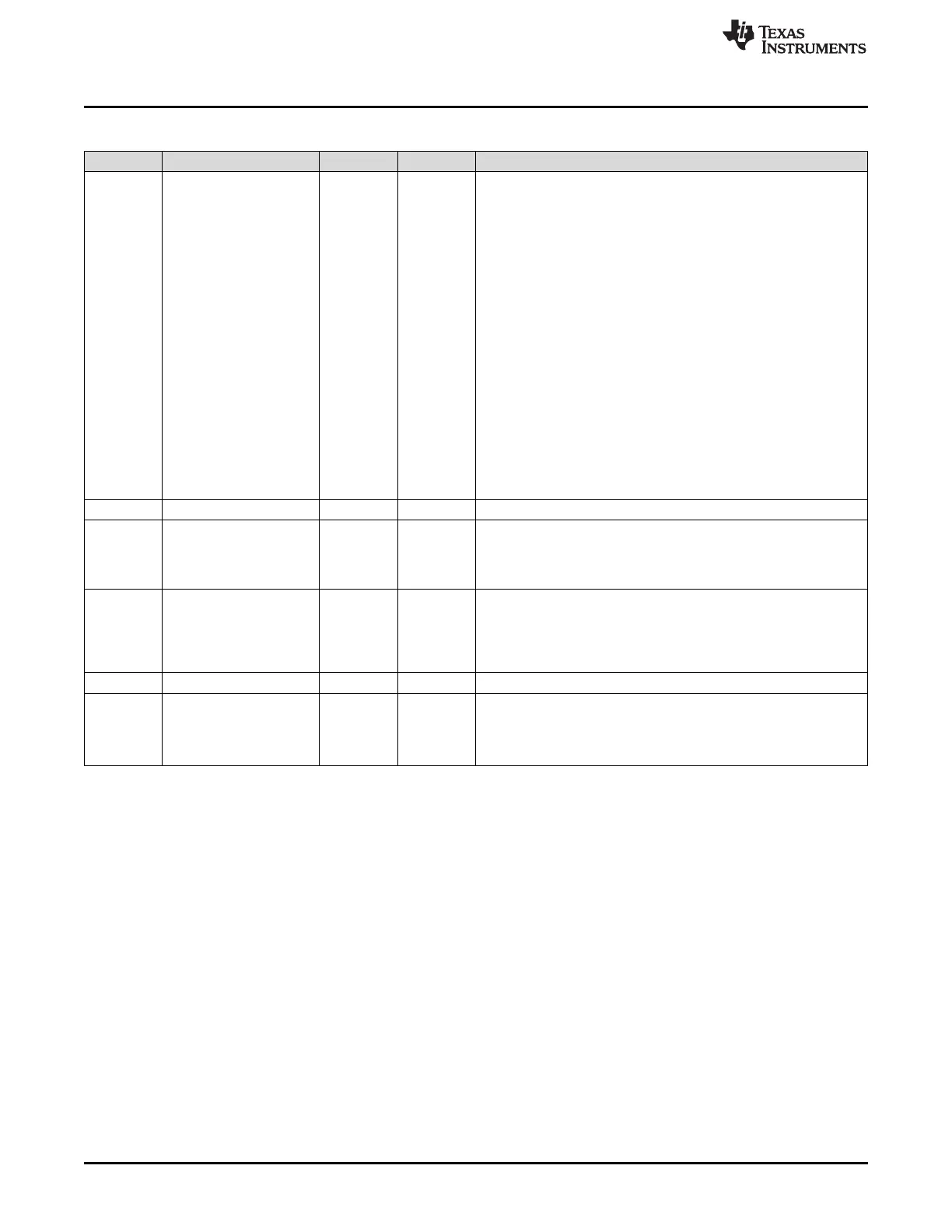

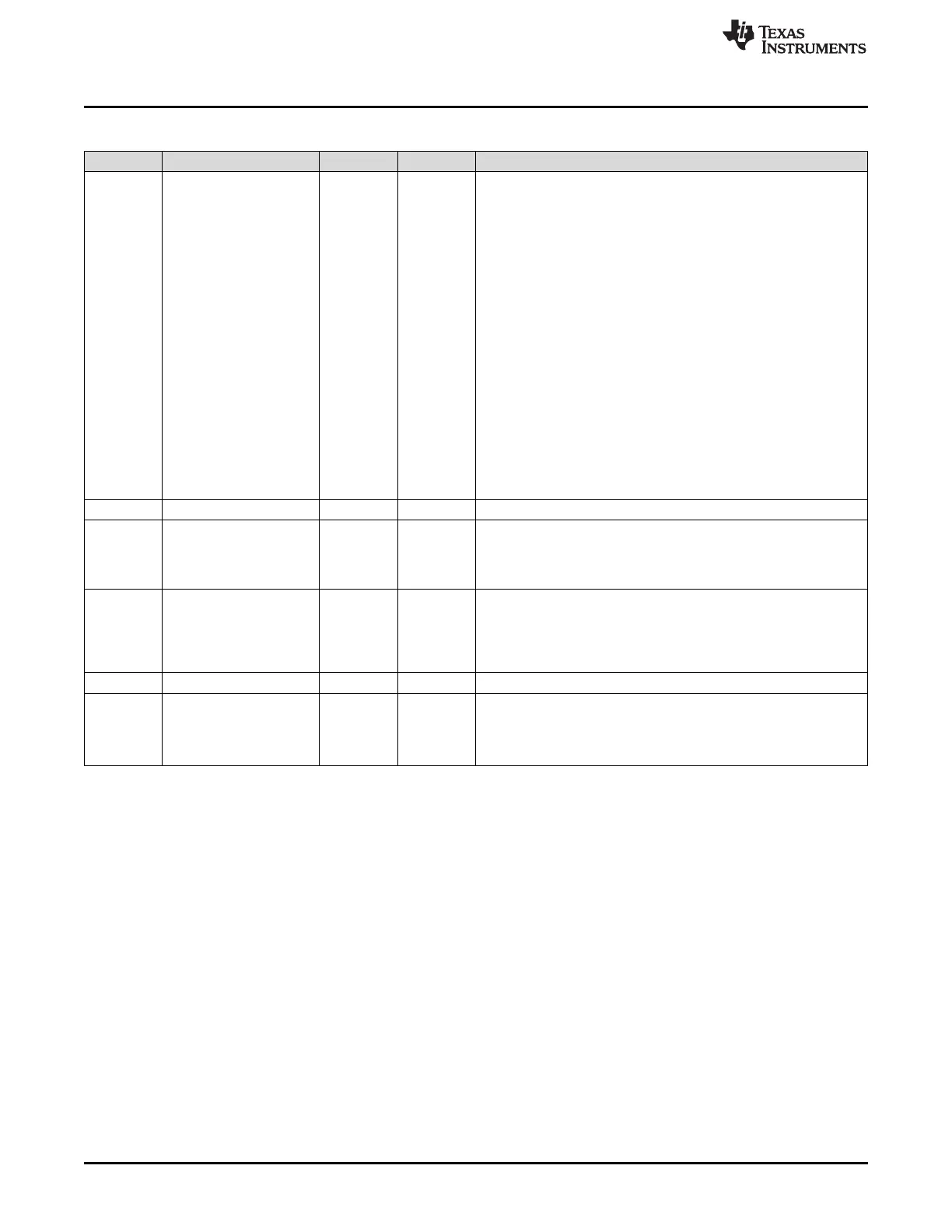

Table 7-11. ADCTRL2 Register Field Descriptions (continued)

Bit Field Type Reset Description

5 SOC_SEQ2 R/W 0h

Start of conversion trigger for sequencer 2 (SEQ2). (Only applicable

in dual-sequencer mode; ignored in cascaded mode.) This bit can be

set by the following triggers:

• S/W - Software writing of 1 to this bit

• ePWM SOCB

When a trigger occurs, there are three possibilities:

Case 1: SEQ2 idle and SOC bit clear SEQ2 starts immediately

(under arbiter control) and the bit is cleared, allowing for any pending

trigger requests.

Case 2: SEQ2 busy and SOC bit clear Bit is set signifying a trigger

request is pending. When SEQ2 finally starts after completing

current conversion, this bit will be cleared.

Case 3: SEQ2 busy and SOC bit set Any trigger occurring in this

case will be ignored (lost).

will be ignored (lost).

0h = Clears a Pending SOC trigger Note: If the sequencer has

already started, this bit is automatically cleared, and writing a zero

has no effect; i.e., an already started sequencer cannot be stopped

by clearing this bit.

1h = Starts SEQ2 from currently stopped position (i.e., Idle mode)

4 RESERVED R 0h Reads return a zero. Writes have no effect.

3 INT_ENA_SEQ2 R/W 0h SEQ2 interrupt enable. This bit enables or disables an interrupt

request to the CPU by INT SEQ2.

0h = Interrupt request by INT_SEQ2 is disabled.

1h = Interrupt request by INT_SEQ2 is enabled.

2 INT_MOD_SEQ2 R/W 0h SEQ2 interrupt mode. This bit selects SEQ2 interrupt mode. It

affects the setting of INT SEQ2 at the end of the SEQ2 conversion

sequence.

0h = INT_SEQ2 is set at the end of every SEQ2 sequence.

1h = INT_SEQ2 is set at the end of every other SEQ2 sequence.

1 RESERVED R 0h Reads return a zero. Writes have no effect.

0 ePWM_SOCB_SEQ2 R/W 0h

ePWM SOCB enable bit for SEQ2.

0h = SEQ2 cannot be started by ePWMx SOCB trigger.

1h = Allows SEQ2 to be started by ePWMx SOCB trigger. The

ePWMs can be programmed to start a conversion on various events.

Loading...

Loading...