www.ti.com

I2C Registers

647

SPRUI07–March 2020

Submit Documentation Feedback

Copyright © 2020, Texas Instruments Incorporated

Inter-Integrated Circuit Module (I2C)

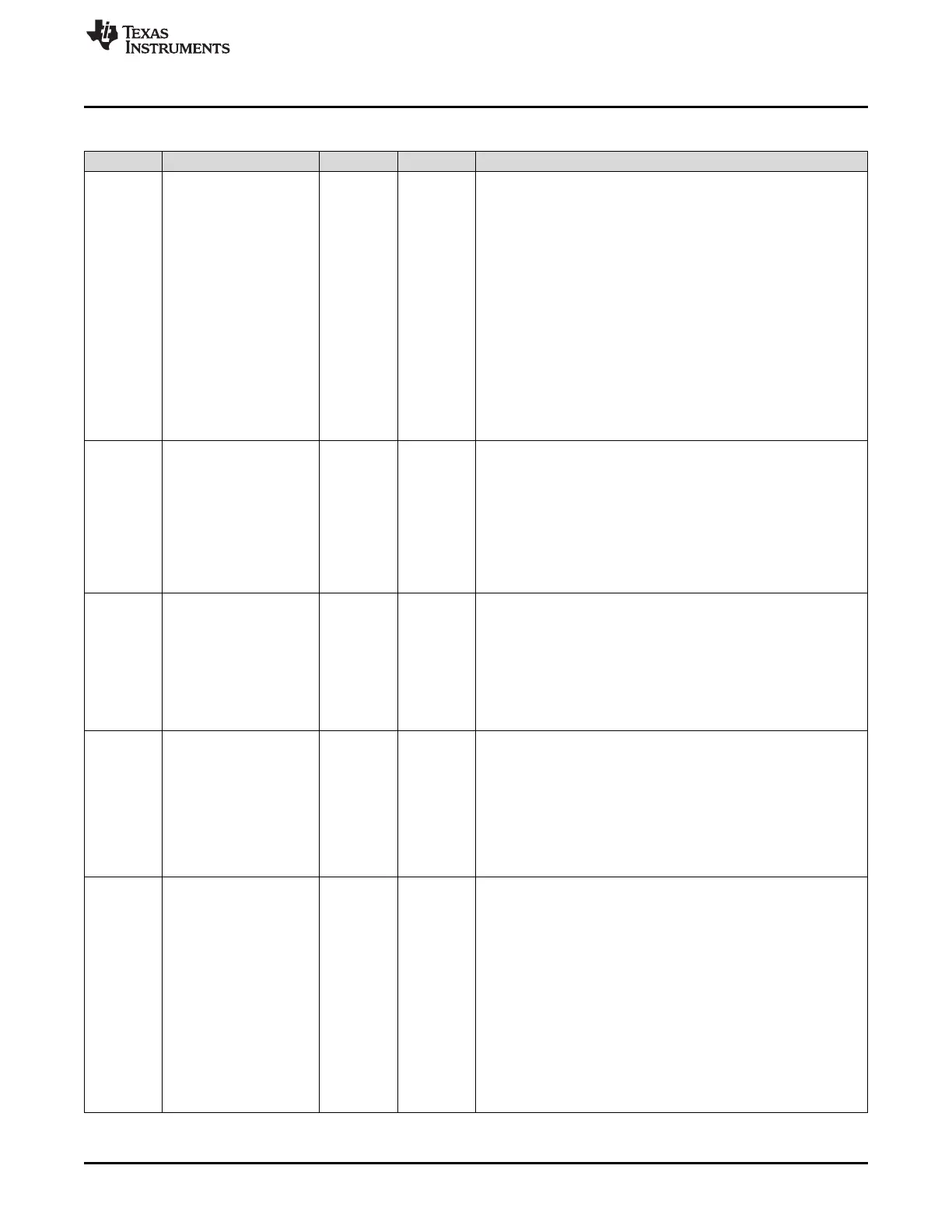

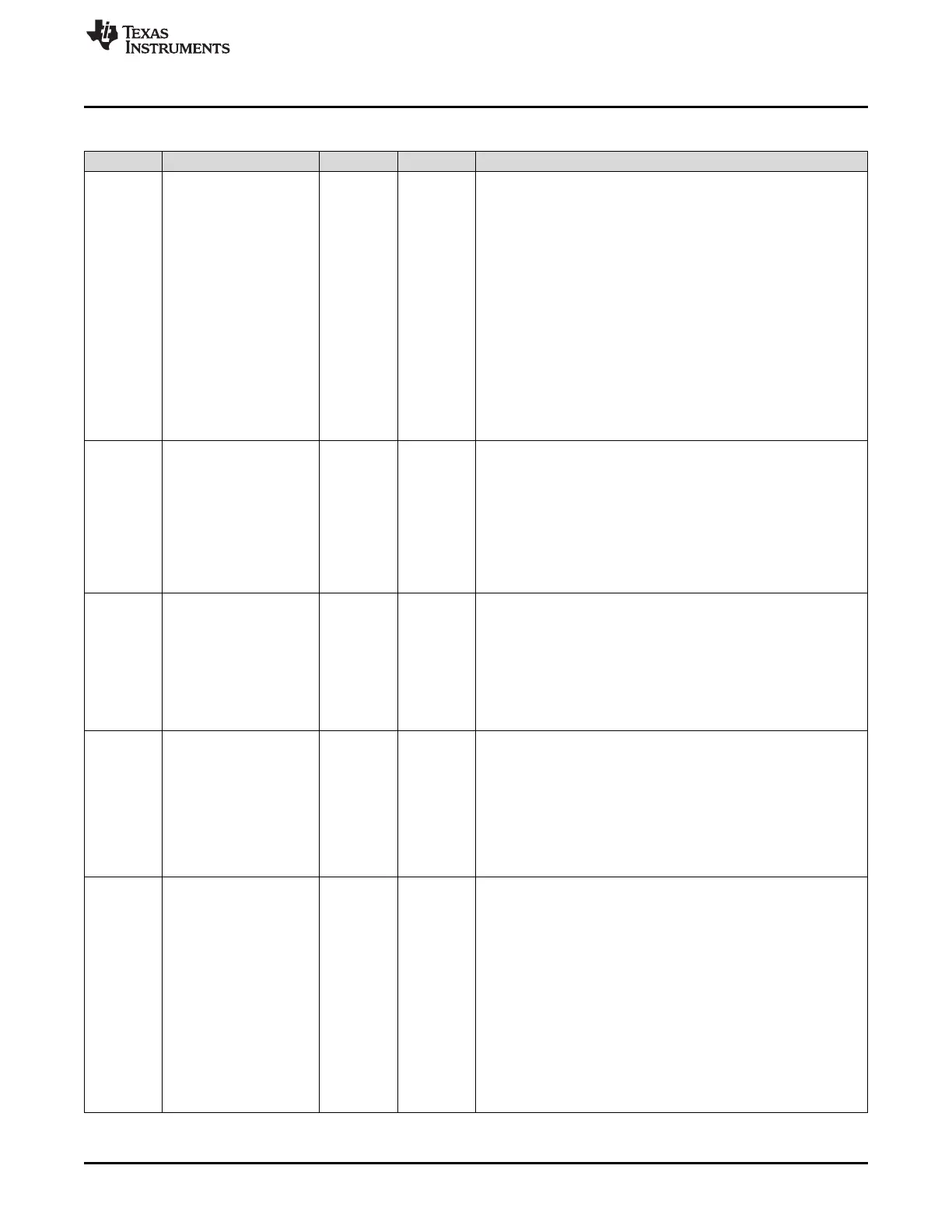

Table 11-19. I2CMDR Register Field Descriptions (continued)

Bit Field Type Reset Description

11 STP R/W 0h

STOP condition bit (only applicable when the I2C module is a

master).

In the master mode, the RM,STT, and STP bits determine when the

I2C module starts and stops data transmissions.

Note that the STT and STP bits can be used to terminate the repeat

mode, and that this bit is not writable when IRS=0. When in non-

repeat mode, at least one byte must be transferred before a stop

condition can be generated. The I2C module delays clearing of this

bit until after the I2CSTR[SCD] bit is set. To avoid disrupting the I2C

state machine, the user must wait until this bit is clear before

initiating a new message.

Reset type: SYSRSn

0h (R/W) = STP is automatically cleared after the STOP condition

has been generated

1h (R/W) = STP has been set by the device to generate a STOP

condition when the internal data counter of the I2C module counts

down to 0.

10 MST R/W 0h

Master mode bit.

MST determines whether the I2C module is in the slave mode or the

master mode. MST is automatically changed from 1 to 0 when the

I2C master generates a STOP condition

Reset type: SYSRSn

0h (R/W) = Slave mode. The I2C module is a slave and receives

the serial clock from the master.

1h (R/W) = Master mode. The I2C module is a master and

generates the serial clock on the SCL pin.

9 TRX R/W 0h

Transmitter mode bit.

When relevant, TRX selects whether the I2C module is in the

transmitter mode or the receiver mode.

Reset type: SYSRSn

0h (R/W) = Receiver mode. The I2C module is a receiver and

receives data on the SDA pin.

1h (R/W) = Transmitter mode. The I2C module is a transmitter and

transmits data on the SDA pin.

8 XA R/W 0h

Expanded address enable bit.

Reset type: SYSRSn

0h (R/W) = 7-bit addressing mode (normal address mode). The I2C

module transmits 7-bit slave addresses (from bits 6-0 of I2CSAR),

and its own slave address has 7 bits (bits 6-0 of I2COAR).

1h (R/W) = 10-bit addressing mode (expanded address mode).

The I2C module transmits 10-bit slave addresses (from bits 9-0 of

I2CSAR), and its own slave address has 10 bits (bits 9-0 of

I2COAR).

7 RM R/W 0h

Repeat mode bit (only applicable when the I2C module is a master-

transmitter).

The RM, STT, and STP bits determine when the I2C module starts

and stops data transmissions

Reset type: SYSRSn

0h (R/W) = Nonrepeat mode. The value in the data count register

(I2CCNT) determines how many bytes are

received/transmitted by the I2C module.

1h (R/W) = Repeat mode. A data byte is transmitted each time the

I2CDXR register is written to (or until the transmit FIFO is empty

when in FIFO mode) until the STP bit is manually set. The value of

I2CCNT is ignored. The ARDY bit/interrupt can be used to

determine when the I2CDXR (or FIFO) is ready for more data, or

when the data has all been sent and the CPU is allowed to write to

the STP bit.

Loading...

Loading...