Register Descriptions

www.ti.com

512

SPRUI07–March 2020

Submit Documentation Feedback

Copyright © 2020, Texas Instruments Incorporated

Direct Memory Access (DMA) Module

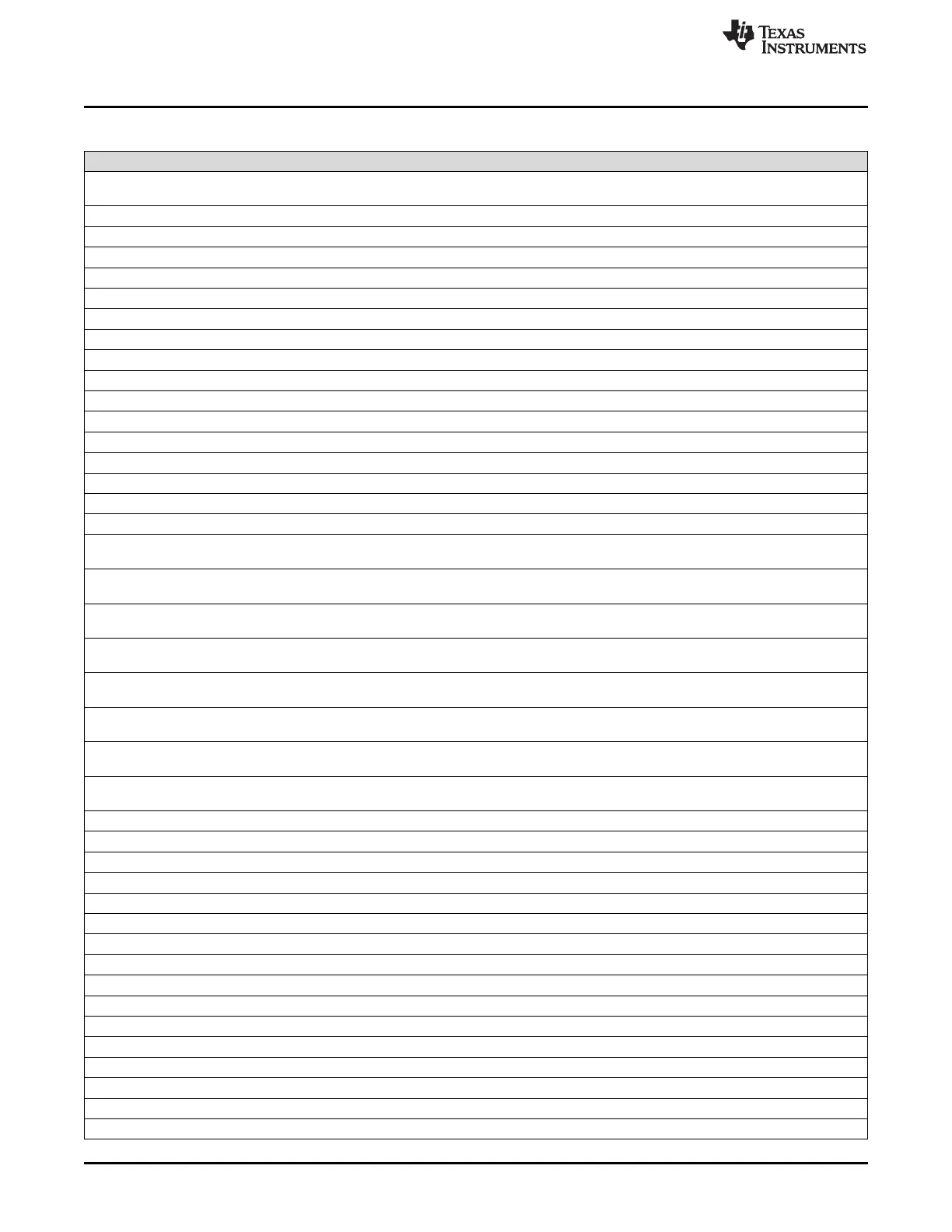

Table 8-2. DMA Register Summary

(1)

(continued)

Offset Acronym Register Name Section

1121h DST_ADDR_1 Active Destination Begin and Current Address Pointer

Registers

Section 8.9.29

11E6h MODE_2 Mode Register Section 8.9.6

11E7h CONTROL_2 Control Register Section 8.9.7

11E8h BURST_SIZE_2 Burst Size Register Section 8.9.8

11E9h BURST_COUNT_2 Burst Count Register Section 8.9.9

11EAh SRC_BURST_STEP_2 Source Burst Step Size Register Section 8.9.10

11EBh DST_BURST_STEP_2 Destination Burst Step Size Register Section 8.9.11

11ECh TRANSFER_SIZE_2 Transfer Size Register Section 8.9.12

11EDh TRANSFER_COUNT_2 Transfer Count Register Section 8.9.13

11EEh SRC_TRANSFER_STEP_2 Source Transfer Step Size Register Section 8.9.14

11EFh DST_TRANSFER_STEP_2 Destination Transfer Step Size Register Section 8.9.15

11F0h SRC_WRAP_SIZE_2 Source Wrap Size Register Section 8.9.16

11F1h SRC_WRAP_COUNT_2 Source Wrap Count Register Section 8.9.17

11F2h SRC_WRAP_STEP_2 Source Wrap Step Size Register Section 8.9.18

11F3h DST_WRAP_SIZE_2 Destination Wrap Size Register Section 8.9.19

11F4h DST_WRAP_COUNT_2 Destination Wrap Count Register Section 8.9.20

11F5h DST_WRAP_STEP_2 Destination Wrap Step Size Register Section 8.9.21

11F6h SRC_BEG_ADDR_SHADOW_2 Shadow Source Begin and Current Address Pointer

Registers

Section 8.9.22

11F8h SRC_ADDR_SHADOW_2 Shadow Destination Begin and Current Address Pointer

Registers

Section 8.9.23

11FAh SRC_BEG_ADDR_2 Active Source Begin and Current Address Pointer

Registers

Section 8.9.24

11FCh SRC_ADDR_2 Active Destination Begin and Current Address Pointer

Registers

Section 8.9.25

11FEh DST_BEG_ADDR_SHADOW_2 Shadow Destination Begin and Current Address Pointer

Registers

Section 8.9.26

1200h DST_ADDR_SHADOW_2 Shadow Destination Begin and Current Address Pointer

Registers

Section 8.9.27

1202h DST_BEG_ADDR_2 Active Destination Begin and Current Address Pointer

Registers

Section 8.9.28

1204h DST_ADDR_2 Active Destination Begin and Current Address Pointer

Registers

Section 8.9.29

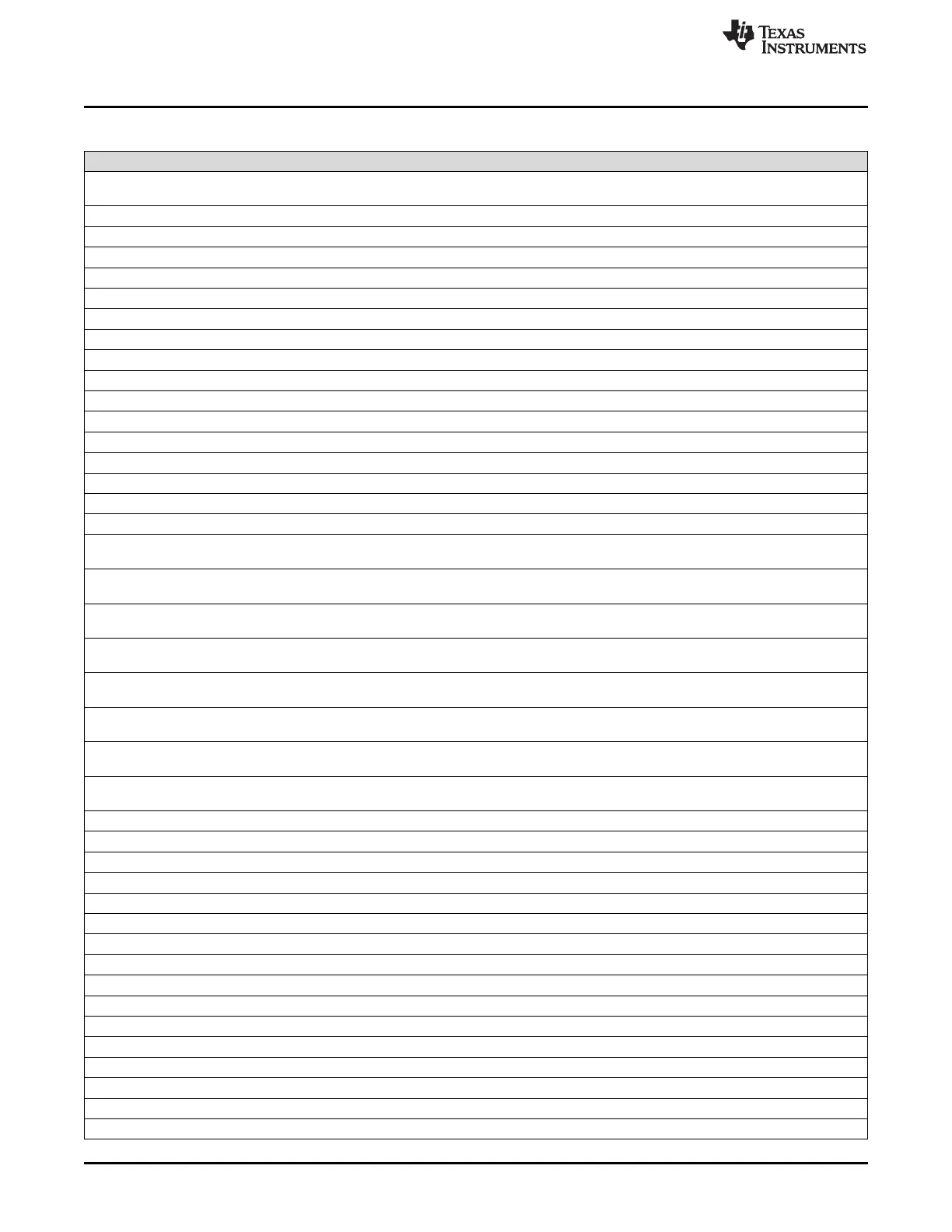

12C9h MODE_3 Mode Register Section 8.9.6

12CAh CONTROL_3 Control Register Section 8.9.7

12CBh BURST_SIZE_3 Burst Size Register Section 8.9.8

12CCh BURST_COUNT_3 Burst Count Register Section 8.9.9

12CDh SRC_BURST_STEP_3 Source Burst Step Size Register Section 8.9.10

12CEh DST_BURST_STEP_3 Destination Burst Step Size Register Section 8.9.11

12CFh TRANSFER_SIZE_3 Transfer Size Register Section 8.9.12

12D0h TRANSFER_COUNT_3 Transfer Count Register Section 8.9.13

12D1h SRC_TRANSFER_STEP_3 Source Transfer Step Size Register Section 8.9.14

12D2h DST_TRANSFER_STEP_3 Destination Transfer Step Size Register Section 8.9.15

12D3h SRC_WRAP_SIZE_3 Source Wrap Size Register Section 8.9.16

12D4h SRC_WRAP_COUNT_3 Source Wrap Count Register Section 8.9.17

12D5h SRC_WRAP_STEP_3 Source Wrap Step Size Register Section 8.9.18

12D6h DST_WRAP_SIZE_3 Destination Wrap Size Register Section 8.9.19

12D7h DST_WRAP_COUNT_3 Destination Wrap Count Register Section 8.9.20

12D8h DST_WRAP_STEP_3 Destination Wrap Step Size Register Section 8.9.21

Loading...

Loading...