XINTF Registers

www.ti.com

854

SPRUI07–March 2020

Submit Documentation Feedback

Copyright © 2020, Texas Instruments Incorporated

External Interface (XINTF)

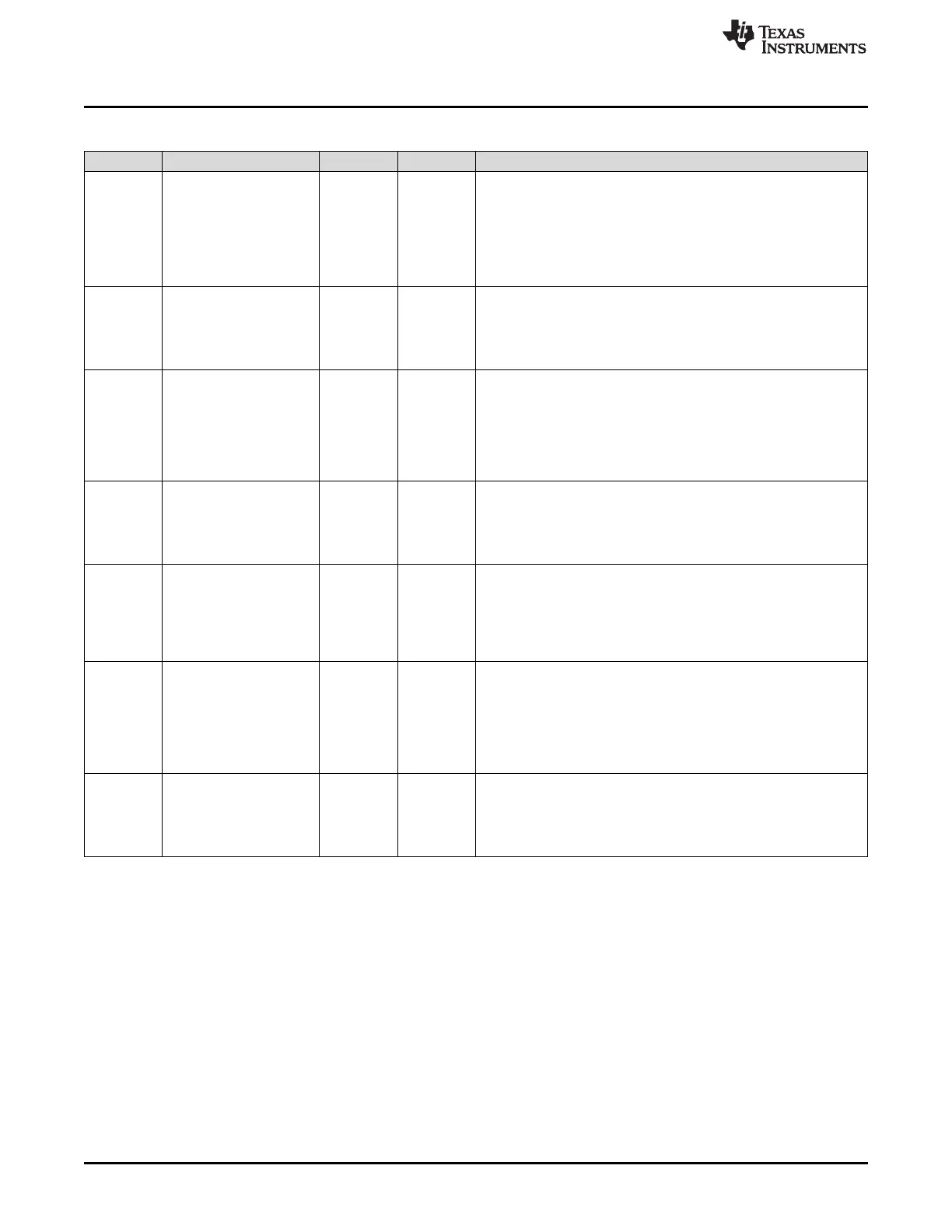

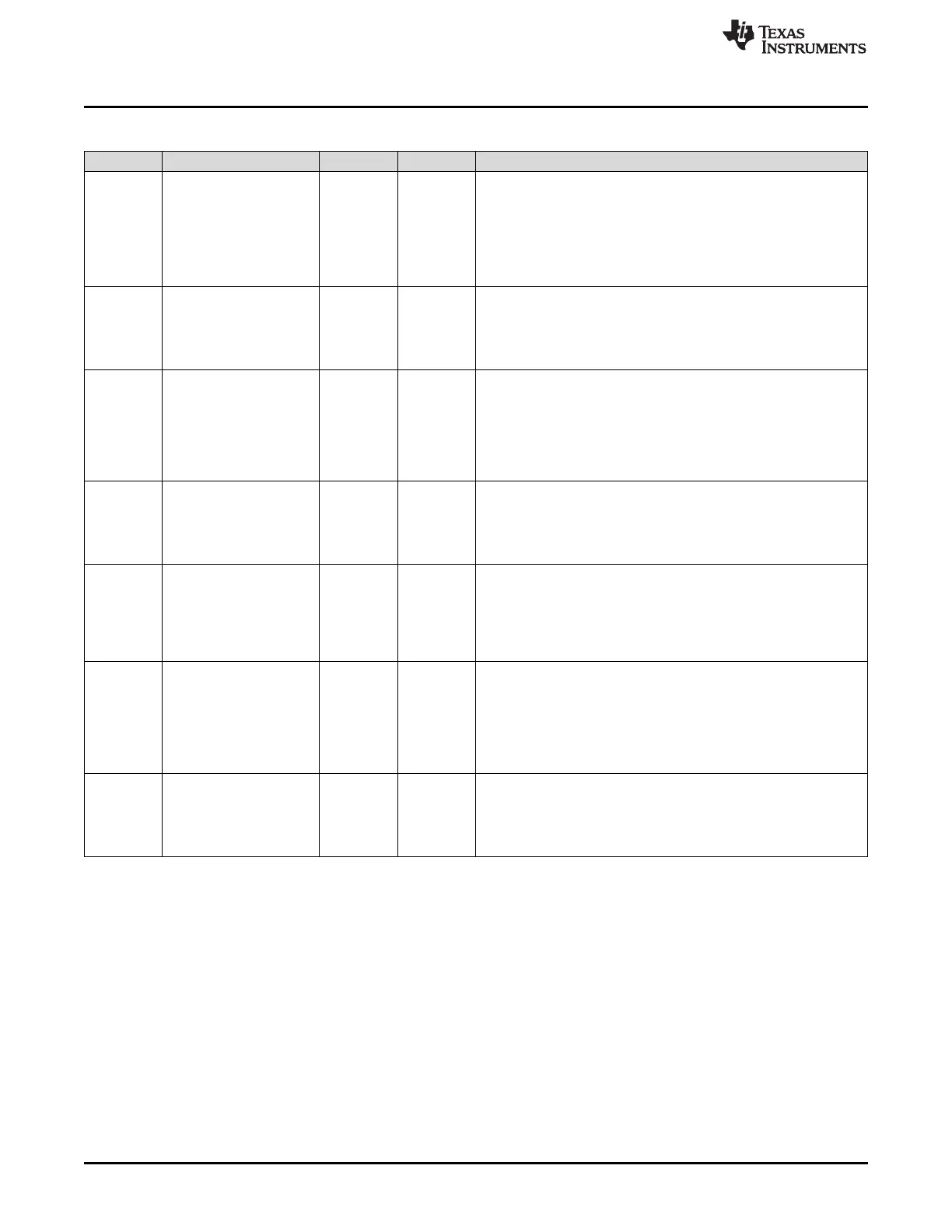

Table 14-9. XTIMING0 Register Field Descriptions (continued)

Bit Field Type Reset Description

14 USEREADY R/W 1h

Determines if accesses to the zone will sample or ignore the

XREADY input signal.

0h = The XREADY signal is ignored when accesses are made to the

zone.

1h = The XREADY signal can further extend the active portion of an

access to the zone past the minimum defined by the XRDACTIVE

and XWRACTIVE fields.

13-12 XRDLEAD R/W 1h Two-bit field that defines the read cycle lead wait state period, in

XTIMCLK cycles. If the X2TIMING bit is set, then the number of wait

states are doubled.

See Section 14.4 for minimum requirements in different modes.

See Table 14-12.

11-9 XRDACTIVE R/W 1h Three-bit field that defines the read cycle active wait state period, in

XTIMCLK cycles. The active period is by default 1 XTIMCLK cycle.

Therefore, the total active period is (1 + XWRACTIVE) XTIMCLK

cycles. If the X2TIMING bit is set, then the number of wait states are

doubled.

See Section 14.4 for minimum requirements in different modes.

See Table 14-13.

8-7 XRDTRAIL R/W 1h Two-bit field that defines the read cycle trail wait state period, in

XTIMCLK cycles. If the X2TIMING bit is set, then the number of wait

states are doubled.

See Section 14.4 for minimum requirements in different modes.

See Table 14-14.

6-5 XWRLEAD R/W 1h Two-bit field that defines the write cycle lead wait state period, in

XTIMCLK cycles.

If the X2TIMING bit is set, then the number of wait states are

doubled.

See Section 14.4 for minimum requirements in different modes.

See Table 14-15.

4-2 XWRACTIVE R/W 1h Three-bit field that defines the write cycle active wait state period, in

XTIMCLK cycles. The active period is by default 1 XTIMCLK cycle.

Therefore, the total active period is (1 + XWRACTIVE) XTIMCLK

cycles. If the X2TIMING bit is set, then the number of wait states are

doubled.

See Section 14.4 for minimum requirements in different modes.

See Table 14-16.

1-0 XWRTRAIL R/W 1h Two-bit field that defines the write cycle trail wait state period, in

XTIMCLK cycles. If the X2TIMING bit is set, then the number of wait

states are doubled.

See Section 14.4 for minimum requirements in different modes.

See Table 14-17.

Loading...

Loading...