Cortex-M3 Processor (Reference Material)

UG0331 User Guide Revision 15.0 97

Note: Writing 1 to the NVIC_ISPR bit corresponding to:

• An interrupt that is pending has no effect

• A disabled interrupt sets the state of that interrupt to pending.

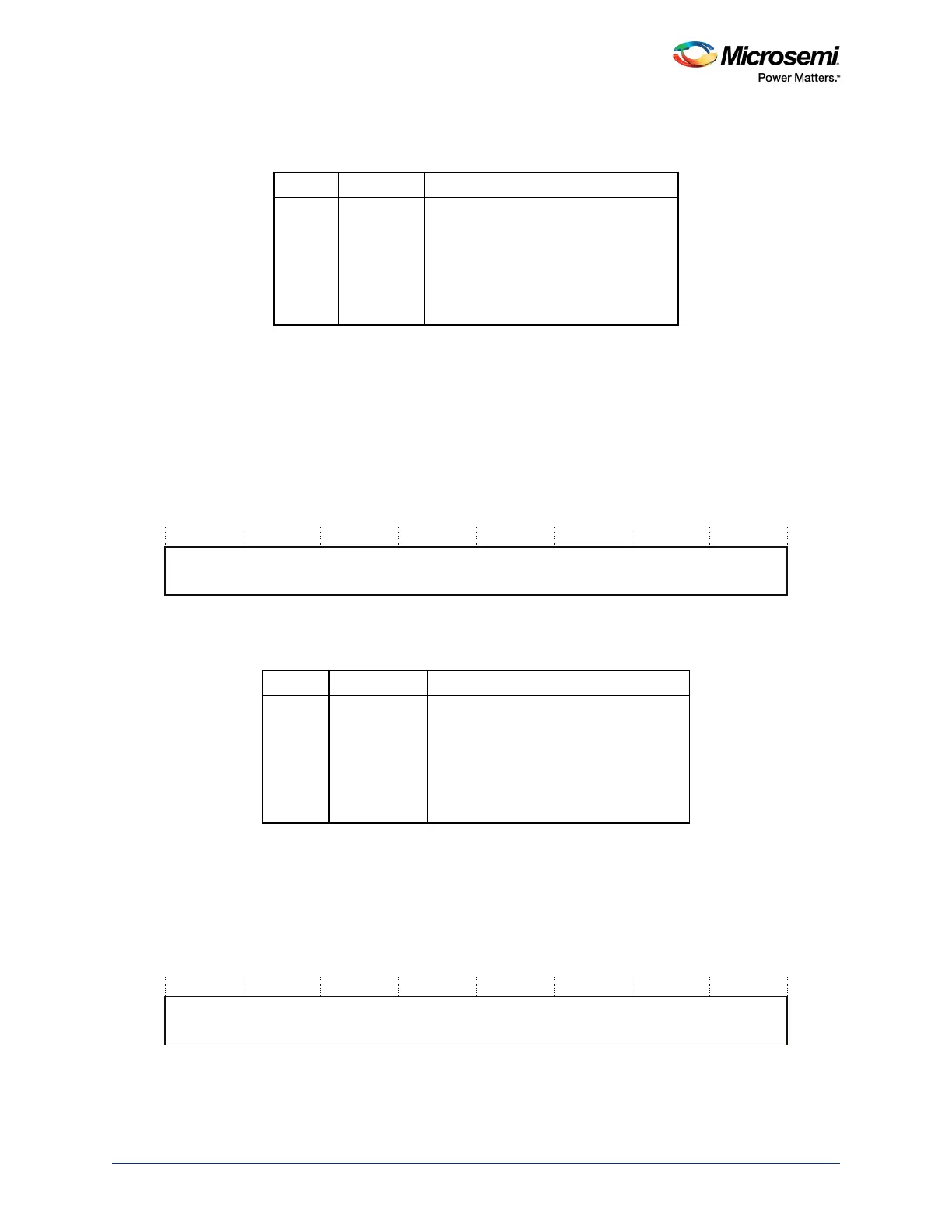

3.7.1.6 Interrupt Clear-Pending Registers

The NVIC_ICPR0-NVIC_ICPR7 registers remove the pending state from interrupts, and show which

interrupts are pending. See the register summary in Table 40, page 95 for the register attributes.

The bit assignments are:

Figure 26 • ICPR Register Bit Assignments

Note: Writing 1 to an NVIC_ICPR bit does not affect the active state of the corresponding interrupt.

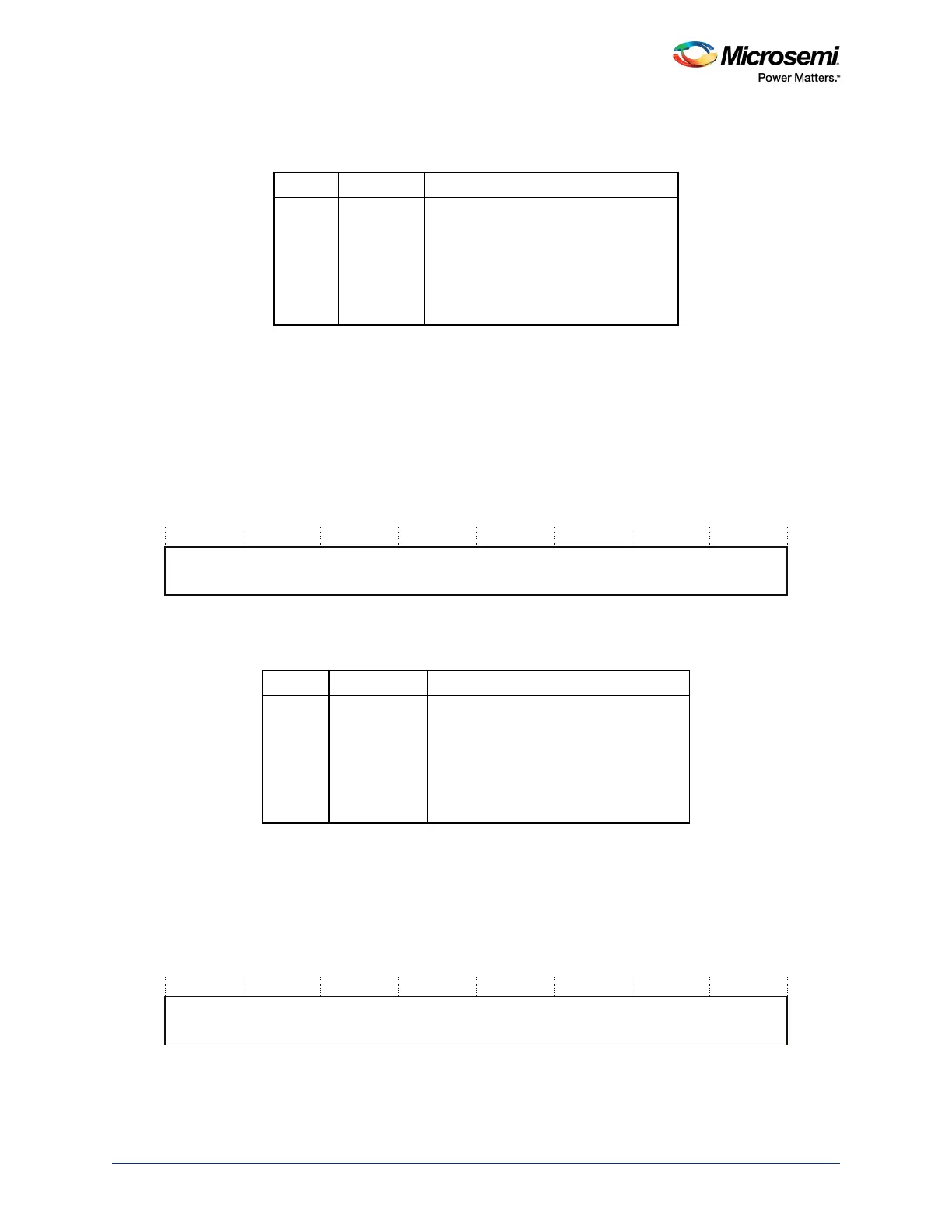

3.7.1.7 Interrupt Active Bit Registers

The NVIC_IABR0-NVIC_IABR7 registers indicate which interrupts are active. See the register summary

in Table 40, page 95 for the register attributes.

The bit assignments are:

Figure 27 • IABR Register Bit Assignments

Table 44 • NVIC_ISPR Bit Assignments

Bits Name Function

[31:0] SETPEND Interrupt set-pending bits.

Write:

0: No effect

1: Changes interrupt state to pending.

Read:

0: Interrupt is not pending

1: Interrupt is pending.

Table 45 • NVIC_ICPR bit assignments

Bits Name Function

[31:0] CLRPEND Interrupt clear-pending bits.

Write:

0: no effect

1: removes pending state an interrupt.

Read:

0: interrupt is not pending

1: interrupt is pending.

CLRPEND bits

31 0

ACTIVE bits

31 0

Loading...

Loading...