Universal Serial Bus OTG Controller

UG0331 User Guide Revision 15.0 311

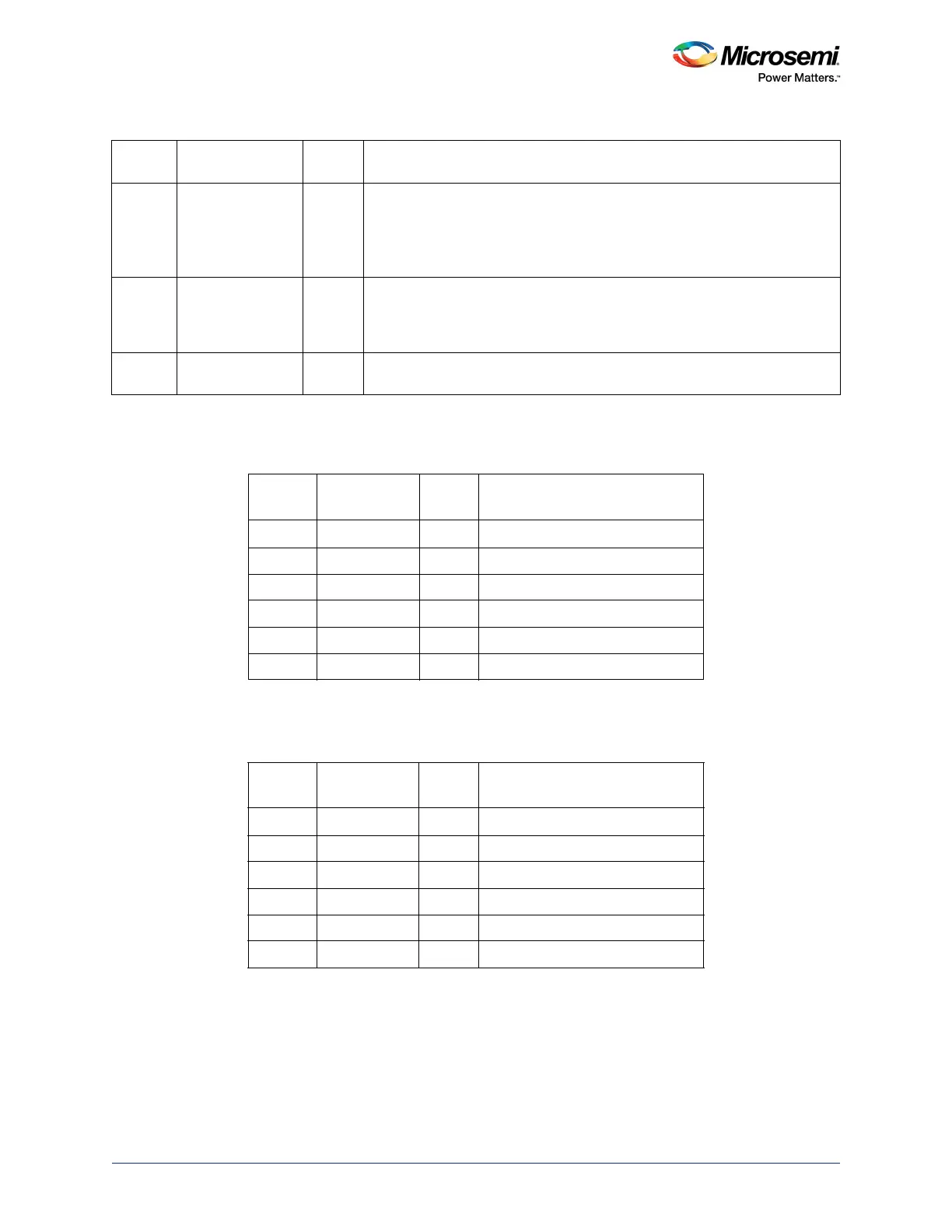

10.3.5.3 TX_IRQ_REG Bit Definitions

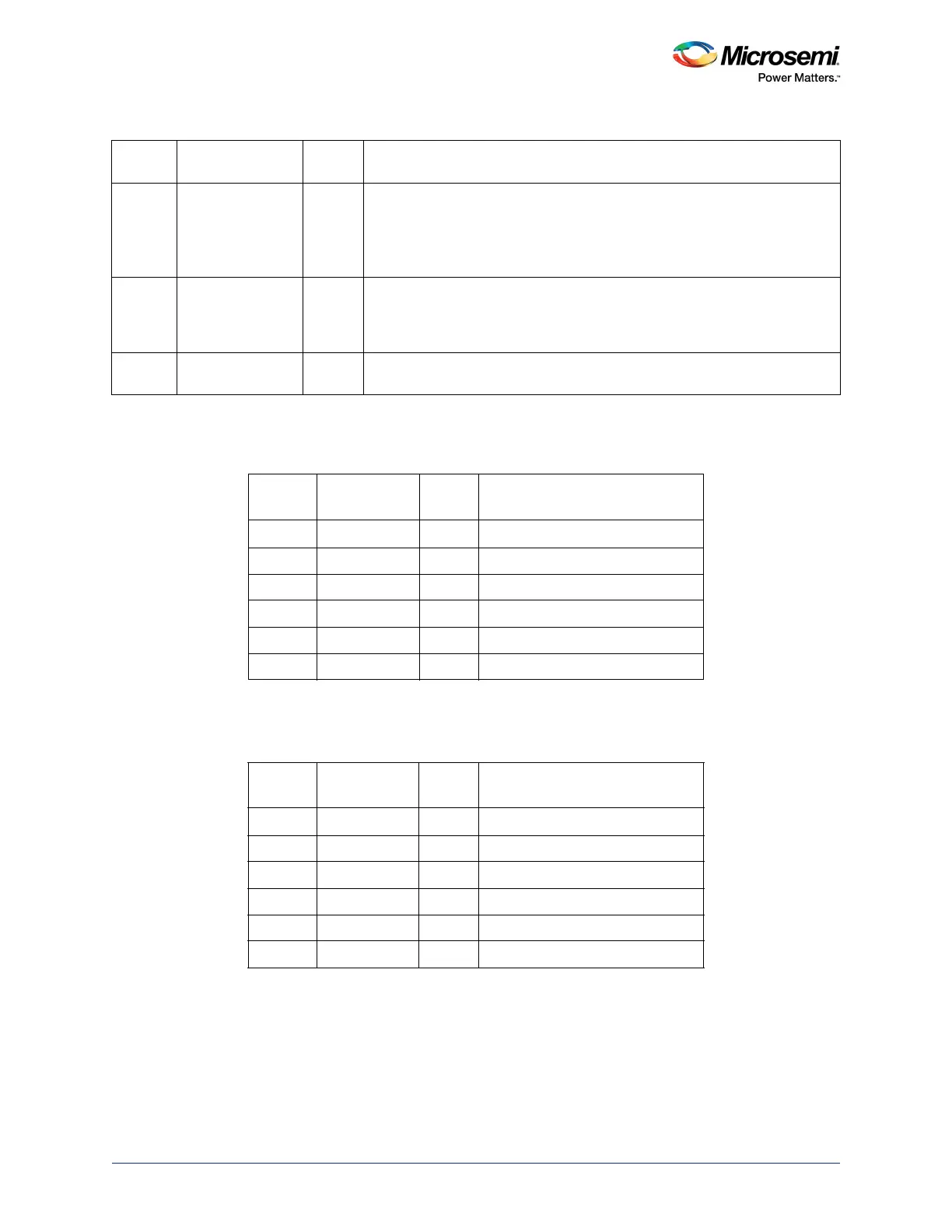

10.3.5.4 RX_IRQ_REG Bit Definitions

2 Resume 0 Set by the Cortex-M3 processor (or fabric master) to generate resume

signaling when the device is in Suspend mode. In Peripheral mode, the

Cortex-M3 processor (or fabric master) should clear this bit after 10 ms (a

maximum of 15 ms), to end resume signaling. In Host mode, the Cortex-M3

processor (or fabric master) should clear this bit after 20 ms.

1 Suspend Mode 0 In Host mode, this bit is set by the Cortex-M3 processor (or fabric master) to

enter Suspend mode. In Peripheral mode, this bit is set on entry into

Suspend mode. It is cleared when the Cortex-M3 processor (or fabric

master) reads the interrupt register, or sets the resume bit above.

0 Enable SuspendM 0 Set by the Cortex-M3 processor (or fabric master) to enable the

SUSPENDM output.

Table 201 • TX_IRQ_REG (0x40043002)

Bit

Number Name

Reset

Value Function

[15:5] Reserved N/A N/A

4 EP4 Tx 0 Transmit endpoint 4 interrupt

3 EP3 Tx 0 Transmit endpoint 3 interrupt

2 EP2 Tx 0 Transmit endpoint 2 interrupt

1 EP1 Tx 0 Transmit endpoint 1 interrupt

0 EP0 0 Endpoint 0 interrupt

Table 202 • RX_IRQ_REG (0x40043004)

Bit

Number Name

Reset

Value Function

[15:5] Reserved N/A N/A

4 EP4 Rx 0 Receive endpoint 4 interrupt

3 EP3 Rx 0 Receive endpoint 3 interrupt

2 EP2 Rx 0 Receive endpoint 2 interrupt

1 EP1 Rx 0 Receive endpoint 1 interrupt

0 Reserved 0 Always returns zero

Table 200 • POWER_REG (0x40043001) (continued)

Bit

Number Name

Reset

Value Function

Loading...

Loading...